Fターム[2G132AK10]の内容

電子回路の試験 (32,879) | 試験のための被試験体の構成、回路構成 (3,847) | 試験のための回路構成 (3,586) | プルアップ、プルダウンのためのもの (10)

Fターム[2G132AK10]に分類される特許

1 - 10 / 10

半導体集積回路及びそのテスト方法

【課題】プローブ針を接触させる外部端子の数を抑制してDCテストを行うことが可能な半導体集積回路を提供すること

【解決手段】本発明にかかる半導体集積回路は、入出力端子P1を介して外部にデータを出力する出力バッファ21と、外部から入出力端子P1を介してデータが入力される入力バッファ22と、入出力端子P1と入力バッファ22の入力との間の信号線上のノードN1と第1入力端子T1との間に設けられたスイッチ26と、外部から第2入力端子T2に供給される第2基準電位とノードN1の電位とを比較して比較結果を出力する比較部23と、入力バッファ22から出力されるデータと比較部23の比較結果との何れかを選択しテスト結果として出力する選択部52と、を備える。

(もっと読む)

電子部品及び検査システム

【課題】特別な検査装置を要することなく、基板への実装状態の適否を容易且つ迅速に検査可能な電子部品の提供。

【解決手段】デバイス1に内蔵されたCPU14は、I/F17が外部端末3から検査開始コマンドを受信したことを契機として検査処理を開始し、冗長端子11である検査用端子13をプルアップ抵抗付きの入力に切り替え、検査用端子13に所定電圧を印加し、検査用端子13の入力電圧を検出し、検出した入力電圧を検査結果として外部端末3へ送信する。

(もっと読む)

半導体装置のテスト回路およびテスト方法

【課題】半導体装置に内蔵されたテスト回路の回路面積を抑えながら直流試験を少ないピン数で行うことができるテスト回路及びテスト方法を提供する。

【解決手段】テスト回路は直流試験用の負荷制御回路(112a,112b)、基準電圧生成回路(113)及び比較回路(114a,114b)、または定電圧回路(214a,214b)、電流−電圧変換回路(215a,215b)、基準電圧生成回路(216)及び比較回路(217a,217b)を、内部コアロジック(102)内のスキャン設計が施された記憶装置(103a〜103d)で制御して直流試験を実施するので、少ないピン数の試験を行う時でもバウンダリスキャン回路が不要となり、TAPコントローラ分の回路面積を削減でき、内部コアロジックの通常動作で使用するレジスタを記憶装置(103a〜103d)と兼用すれば面積を削減できる。

(もっと読む)

積層集積回路デバイス中のティアツーティア結合を検出するための回路

第1の半導体ティアは、積層集積回路(IC)デバイス中のティアツーティア結合を検出するための第1のティアツーティアコネクタを有する。第2の半導体ティアは、第1のティアツーティアコネクタに電気的に結合するように構成された第2のティアツーティアコネクタを有する。ティアツーティア検出回路が第2のティアツーティアコネクタに電気的に結合する。ティアツーティア検出回路は、第1の半導体ティアと第2の半導体ティアとの間の電気的結合を示す出力信号を生成する。  (もっと読む)

(もっと読む)

マイクロコントローラ

【課題】本発明は、テスト端子を有効に利用することが可能なマイクロコントローラを提供することを目的とする。

【解決手段】 本発明に記載の1つのマイクロコントローラは、テスト信号を入力可能なテスト端子2と、テスト端子2に接続され、テスト信号を内部で生成するテスト信号生成回路とを備えている。このテスト信号生成回路は、テスト端子2と所定の電位(VSS電位又はVCC1電位)とを接続する抵抗3を有する。

(もっと読む)

半導体集積回路

【課題】接続端子数を十分に削減することが可能な半導体集積回路を提供する。

【解決手段】信号が入力されるアナログ入力端子110を有し、アナログ入力端子110への信号入力により所定の動作を実行するアナログ回路100と、アナログ回路100外部からアナログ入力端子110への信号入力経路に接続され、アナログ入力端子110をVDD電位の状態にするVDDセル200と、アナログ回路100外部からアナログ入力端子110への信号入力経路に接続され、アナログ入力端子110をVDD電位と異なるVSS電位の状態にするVSSセル210と、VDDセル200とアナログ入力端子110との間又はVSSセル210とアナログ入力端子110との間を導通状態にするか否かを制御するアナログスイッチ330および340とを備える

(もっと読む)

半導体集積回路およびその実装検査方法

【課題】入出力端子の入出力特性を劣化させることなく実装不良の検出を行うことを可能とする半導体集積回路、および、その不良端子の特定を可能とする検査方法を提供する。

【解決手段】半導体集積回路2は、内部回路3、電源端子4、グランド端子5、入出力端子6、および保護ダイオード8の他、検査時に電流または電圧が印加されるテスト端子10と、テスト端子10と入出力端子6との間に接続された検査用ダイオード9とを備える。集積回路2を回路基板20に実装したとき、信号配線23にグランド電圧を与えるとともに、テスト端子10に対して電流印加電圧測定を行うことにより、入出力端子6の実装不良を検出することができる。また、テスト端子10にグランド電圧を与えるとともに、信号配線23に対して電流印加電圧測定を行うことにより、入出力端子6の実装不良を検出することも可能である。

(もっと読む)

信号測定方法と装置および電子部品

【課題】回路基板等の信号測定方法に関するものであり、プローブとの接触点で発生する反射が被測定回路に伝わり、信号波形が変化することを低減するものである。

【解決手段】信号配線106に接続されるインピーダンス整合用等の回路素子を2つ以上に分割し、その接続点にプローブ107を接触させて信号の分圧電圧を測定することで、被測定回路に隣接する回路素子101で信号の反射を減衰させている。さらに、回路素子101と102のインピーダンス値と測定した分圧電圧を用いて補正演算を行い、測定点の信号を導出する。

(もっと読む)

半導体集積回路、システムインパッケージ型半導体装置及び半導体集積回路間の接続状態の検査方法

【課題】 バンプによる接続におけるその接続状態を精度よく検査すること。

【解決手段】 複数の入力端子と、この複数の入力端子にそれぞれ接続された複数の入力回路とを備えた半導体集積回路において、入力端子と入力回路との間にそれぞれ配置され、入力端子と所定電位間の抵抗値を変化させる複数の検査用回路と、複数の検査用回路を動作させるために設けられた共通の検査端子とを備えた。また、検査端子に印加される電圧に応じて、入力端子と所定の電位との間の抵抗値を変化させることができる。

(もっと読む)

アナログ差動回路試験装置

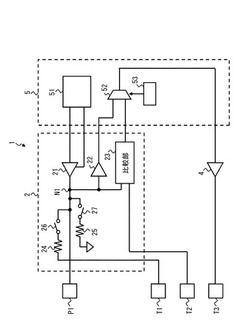

【課題】 LSI内部に配設されるアナログ差動回路の特性を測定、解析するアナログ差動回路試験装置を提供する。

【解決手段】 試験装置10は、テストモードで被試験回路であるアナログ差動回路17の入力対をLSI内部の入力ノードIN、INBから切り離すトランスファゲート13、14と、テストモードの際に、制御信号CODE[1:n]によって外部から調整可能な電圧を生成して入力対のそれぞれに印加する電圧調整回路15と、クロック信号に応答して被試験アナログ差動回路17の出力をラッチするFF回路16とを備える。LSI内部のアナログ差動回路17のHigh特性及びLow特性の測定を可能にする。

(もっと読む)

1 - 10 / 10

[ Back to top ]