Fターム[4M106AA08]の内容

半導体等の試験・測定 (39,904) | 対象 (8,684) | 被テスト回路 (17)

Fターム[4M106AA08]に分類される特許

1 - 17 / 17

半導体装置

【課題】

実施形態は、解析が簡便な半導体装置を提供する。

【解決手段】

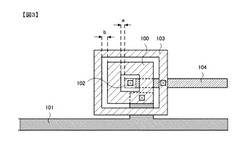

本実施形態の半導体装置は、内部信号を伝送可能な第1配線101と、第1配線101

と電気的に接続された測定電極100と、測定電極100と隣接するように配置され、内

部信号を計測するときに接地電位VSSが印加され、内部信号を計測する以外のときに所

望の電圧が印加されたダミー電極102,103とを備える。

例えば、測定電極100は、環状に形成されており、ダミー電極は、第1電極102と

第2電極103とを有し、第1電極102は、測定電極100の内側に形成された空間に

隣接するように配置され、第2電極103は、測定電極100の外側に隣接するように配

置される。

(もっと読む)

テスト回路、集積回路、及び、テスト回路のレイアウト方法

【課題】 より簡易な設計手法で作製可能なテスト回路を提供する。

【解決手段】 テスト回路100は、基板と、基板上に形成された配線部及び被試験デバイス部10とを備える構成とする。テスト回路100では、被試験デバイス本体のパターン形成面内における回転中心位置Oと複数の接続電極13a〜13dのそれぞれとを結ぶ直線L1の延在方向が、配線21の延在方向に対して所定の角度で傾いている。さらに、被試験デバイス本体及び複数の接続電極13a〜13dをパターン形成面内で90度回転させた際にも、複数の接続電極13a〜13d及び複数の配線21〜24間の接続が維持されるような位置に複数の接続電極13a〜13dが配置される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】TEGによる検査結果を容易に確認できるようにしつつ、TEGの占有面積を小さくする。

【解決手段】TEG群300は、第1テスト用パッド310、第2テスト用パッド312、及び複数のTEG(例えば第1TEG320、第2TEG340、及び第3TEG360)を有している。複数のTEGは、電気回路上、第1テスト用パッド310と第2テスト用パッド312の間に位置し、互いに直列又は並列に配置されており、かつ平面視で互いに重なっていない。本実施形態において、TEG群300を構成するTEGは、OBRICH(Optical Beam Induced Resistance Change)用のTEGである。

(もっと読む)

半導体装置及びその検査方法並びにその設計方法

【課題】不良箇所を容易に特定し得る半導体装置及びその形成方法並びにその設計方法を提供する。

【解決手段】配線パターン32aと、ダミーパターン32bと、一方の端部が配線パターンに電気的に接続され、他方の端部がダミーパターンに電気的に接続されたヒューズ32cとを有している。

(もっと読む)

半導体装置及び半導体装置の製造管理方法

【課題】製造マージンの評価や製造マージンの管理を容易にする半導体装置を提供する。

【解決手段】セルアレイを含む半導体装置において、セルアレイの周囲に設けられたダミー領域にセルアレイのセルと略同一形状のレイアウトパターンを有するプロセス不良検出回路を設ける。特に、プロセス不良検出回路がセルアレイの周辺部に設けられたダミーパターンとしての機能を備えることによって、プロセス不良検出回路によるチップ面積を抑制できる。

(もっと読む)

半導体チップの検査方法

【課題】半導体チップの側部に生じた欠損やクラックによるシールリングのダメージを検出して、半導体チップの信頼性向上を図ることが可能な検査方法を提供する。

【解決手段】半導体基板上に、能動素子及び電極パッドを形成した能動領域Aと、これを囲むシールリング5を含む環状の周辺領域Cとを形成して構成され、さらに周辺領域Cのうちシールリング5の外側に、能動領域Aを囲むと共に両端が隣り合って位置する線状を呈して一端7aが半導体基板に接地された検査用配線7、及び、この他端に接続された検査用パッド9を形成した半導体チップ1に対し、キャピラリにより電極パッド3とパッケージ11の接続端子面13とをボンディングワイヤ15により電気接続する工程において、キャピラリの先端部から引き出されたボンディングワイヤ15を検査用パッド9に押し当てることで、キャピラリにより検査用配線7の電気的な導通状態を検出する。

(もっと読む)

半導体装置および半導体装置の検査方法

【課題】リモート温度センサ等の温度制御装置を追加設置することなく半導体集積回路上に形成された温度検出回路の検査が可能な半導体装置およびその検査方法を提供する。

【解決手段】半導体ユニット100は、温度変化に応じて変化する第1電流を出力する第1電流源111と、基準信号VREFにより出力電流が制御可能かつ温度に対して略一定の第2電流を出力する第2電流源112と、第1電流と第2電流の差を第3電流として入力し電圧に変換して温度信号VTMPとして出力する電流電圧変換回路113から構成される温度検出回路110と、温度検出回路110と同一チップ上に形成され、設定信号VSETにより発熱量が変化する信号処理回路120を具備する。判定手段は、設定信号VSETおよび基準信号VREFを印加した際の温度検出回路110から出力される温度信号VTMPを検査基準値VTESTと比較し、半導体ユニット100の適否を判定する。

(もっと読む)

遅延測定装置および半導体装置

【課題】半導体装置内部の遅延値を測定でき、回路規模の増加を抑制し、ノイズの発生が少ない遅延測定装置を提供する。

【解決手段】半導体装置の内部に配置される遅延測定装置Aは、入力データ値をクロックCKのエッジで取り込んで保持するフリップフロップ(記憶素子)1と、フリップフロップ1の反転出力端子NQに接続された遅延素子2と、外部入力データ値Dinと遅延素子2による遅延出力データ値DLのいずれか一方を選択しフリップフロップ1へ出力するセレクタ3と、フリップフロップ1の正転出力端子Qに接続された測定結果出力端子O1とを備える。フリップフロップ1は、セレクタ3の選択信号SEが“1”の場合、外部入力データ値Dinを入力し、クロックCKの立ち上がりエッジで取り込む。また、選択信号SEが“0”の場合、遅延出力データ値DLを入力し、クロックCKの立ち上がりエッジで取り込む。

(もっと読む)

半導体試験システム、半導体試験装置、被試験ウェハおよび半導体試験方法

【課題】 被試験ウェハ直前のプローブ針までの全ての系を自己診断する。

【解決手段】 本発明の半導体試験システム100は、被試験ウェハ300と、被試験ウェハと電気的に接続される半導体試験装置200とを用いて、被試験ウェハの電気的試験を行い、被試験ウェハには、複数の半導体回路350と、複数の半導体回路の外縁に配され、半導体回路と等しい電極を有する自己診断回路400と、が印刷され、半導体試験装置は、被試験ウェハに圧接するプローブカード240と、プローブカードに接続され、半導体試験装置とウェハとの電気信号を中継するパフォーマンスボード230と、を備え、プローブカードが半導体回路に接続されているときは半導体回路の試験を行い、プローブカードが自己診断回路に接続されているときは半導体試験装置の自己診断を行う。

(もっと読む)

半導体テスト装置

【課題】被試験デバイスである半導体装置の動作テストに必要なテスト情報を、容易に半導体装置に入力することのできる、半導体テスト装置を提供する。

【解決手段】半導体テスト装置は、被試験デバイスである半導体装置の動作テストを行う際に必要となるテスト情報がアドレスに対応付けられて格納されており、前記動作テストの際に、半導体装置に前記テスト情報を出力する、テスト情報格納部と、前記テスト情報格納部にアドレス情報を出力するアドレス出力回路であって、前記テスト情報格納部は、前記アドレス情報で特定されるアドレスのテスト情報を出力する、アドレス出力回路と、を備えて、構成されている。

(もっと読む)

半導体装置及びその検査方法

【課題】パッド電極の面積を大きくすることなく、低荷重の接触でプローブ端子とパッド電極との間の接触抵抗を小さくして、半導体装置を安定して検査できるようにする。

【解決手段】半導体装置は、半導体ウエハ20の上に形成され、内部回路6に電気信号を印加するための複数のパッド電極1と、プローブ端子と各パッド電極との間の電気的な接続を取るためのダミーパッド電極2と、パッド電極1ごとに設けられた複数のスイッチ素子3と、各スイッチ素子3を介して、ダミーパッド電極2と各パッド電極1とを電気的に接続するダミー配線4とを有している。各パッド電極1は、ダミーパッド電極2と各パッド電極1とにプローブ端子により印加された電圧によって、パッド電極1の表面に形成された酸化膜が絶縁破壊されることにより、ダミーパッド電極2と各パッド電極1とが導通状態とされる。

(もっと読む)

半導体装置及び半導体集積回路検査方法

【課題】プローブ密集度を高めることなく、検査時間を短縮することができる半導体検査装置及び半導体集積回路検査方法を提供する。

【解決手段】ウェハ2に複数個の半導体集積回路3が形成されている。ウェハ2の有効領域外周2A上又はレチクル外周上に形成された複数の検査用パッド4aと、検査用パッド4aから複数個の半導体集積回路3に沿ってそれぞれ延びるバス配線である電源供給用メタル配線12、グランド用メタル配線15、出力信号検査用メタル配線、制御信号用メタル配線及びスイッチ素子制御用メタル配線14と、バス配線と個々の半導体集積回路3とを接続する連結用メタル配線と、連結用メタル配線16上に形成され、かつ検査対象となる半導体集積回路3を選択するスイッチ素子とが設けられている。

(もっと読む)

半導体装置とその製造方法

【課題】本発明は、ダイシング工程の際に「残留したバンプ」が発生せず、加えて半導体装置の取れ数を落とすことの無いスクライブ部分の電極パッド構造をもった半導体装置およびその製造方法を提供することを目的とする。

【解決手段】ウェハ1の最外周部分のスクライブ3の一部分に、スクライブPCM4の電極パッド5にそれぞれ対応する電流供給パッド7を集めて備え、スクライブPCM4の電極パッド5からそれぞれ引き出した配線を、対応する電流供給パッド7に接続し、複数の電流供給パッド7を碁盤目状にお互いショートしないように配列した構成とする。この構成によれば、無電解めっきの際に、電流供給パッド7からスクライブPCM4の電極パッド5へ電流を供給することにより、選択的に、半導体チップ2の電極パッド8にバンプを形成し、スクライブPCM4の電極パッド5にはバンプを形成しないようにできる。

(もっと読む)

電源ノイズ耐性検査回路及び電源ノイズ耐性検査方法

【課題】IPコアのテスト時にIPコアの電源ノイズ耐性テストを施行する等を図る。

【解決手段】縦続接続の電源ノイズ生成回路からなるオンチップキャパシタ兼用電源ノイズ生成回路14をIPコア12の外周に配置する。電源ノイズ生成回路の電源部は、IPコア12の電源部と接続される。テストモード時に、電源ノイズ生成回路の各々は駆動されて電源ノイズを電源部を経てIPコアに印加する。IPコア12のデータ入力にはテストパターンデータが印加され、IPコア12のデータ出力から出力される出力データとテストパターンデータに対する期待値と比較してIPコア12のファンクションテスト時に電源ノイズ耐性の検査を行う。

(もっと読む)

素子基板、素子基板の検査方法、及び半導体装置の作製方法

【課題】複数の評価用発振回路を用いた検査回路および検査方法において、検査時間の短縮、及び検査の煩雑さを低減する方法を提供する。

【解決手段】表示装置などの半導体装置と同一基板に一体形成された複数の評価用発振回路に共有される1つの測定用出力端子で検査を行うことができる。そして測定結果に対しフーリエ変換することによって同時に複数の評価用発振回路の発振周波数を得て、半導体素子のばらつきを評価することができる。

(もっと読む)

半導体ウエハ、および強誘電体メモリ装置の試験方法

【課題】 製造コストが低減された半導体ウエハ、ならびに製造コストを低減することができる強誘電体メモリ装置の試験方法を提供する。

【解決手段】 本発明の半導体ウエハ200は、強誘電体メモリ装置100を含む複数の半導体チップ領域220と、試験用チップ領域210と、複数の半導体チップ領域220と試験用チップ領域210とを接続する配線230,240と、を含む。

(もっと読む)

パターン検査方法および検査装置

【課題】帯電が蓄積しやすい試料に対して電子線を照射し続けると、帯電電位が経時変化することにより電子線画像の位置や焦点がドリフトするため、高感度・高安定での検査が困難である。

【解決手段】ウエハ上部の帯電制御電極用電源の電極電位を低くしていくと、画像の明るさが低下してくる。画像の明るさが一定の領域は正帯電の状態であり、暗くなる領域は負帯電の状態である。従って、正帯電の状態と負帯電の状態との境目、すなわち明るさの変化点が正帯電と負帯電とが切り替わる点であり、帯電が弱い状態である。この変化点を検査条件として設定することにより帯電量を抑制し、安定したウエハの検査を行うことができる。印加電圧V1が変化点であると推定され、大まかには、印加電圧V1の近傍の破線で囲まれた領域の電圧範囲内に含まれる。この電圧範囲内であれば、検査条件における帯電の影響を低減できる。

(もっと読む)

1 - 17 / 17

[ Back to top ]