Fターム[4M109DA05]の内容

半導体又は固体装置の封緘、被覆構造と材料 (27,768) | 外形 (595) | 部分的形状 (423)

Fターム[4M109DA05]の下位に属するFターム

Fターム[4M109DA05]に分類される特許

1 - 12 / 12

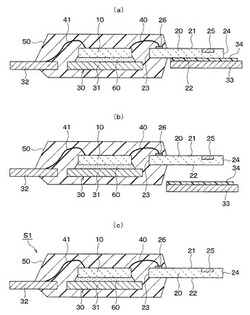

モールドパッケージの製造方法

【課題】センサチップの一端側をモールド樹脂で封止してモールド樹脂で片持ち支持するようにしたモールドパッケージの製造方法において、モールド樹脂による封止前におけるセンサチップのぐらつきを防止して、工程中のワークの取り扱い性に優れた製造方法を実現する。

【解決手段】センサチップ20の一端23側をモールド樹脂50で封止してモールド樹脂50で片持ち支持するようにしたモールドパッケージS1の製造方法においてリードフレーム30として、センサチップ20の他端24側を支持する支持部33を有するものを用意し、センサチップ20の他端23側を支持部33で受けて支持するようにし、支持部33による支持を維持した状態にてモールド樹脂50による封止を行った後に、リードフレーム30から支持部33をカットして、センサチップ20の他端24側から支持部33を除去する。

(もっと読む)

電子機器およびその製造方法

【課題】部品の破損を効果的に防いだ上で、軽量且つ安価な電子機器およびその製造方法を提供する。

【解決手段】電子機器は、ケース1と、前記ケース1の底部1aに下面2aが対向して、前記ケース1の内部に配置された回路基板2と、前記回路基板2の上面2bに実装された電子部品3と、上部開口端4aと下部開口端4bとを有し、前記電子部品3を囲み且つ前記回路基板2の上面2bに前記下部開口端4bが接するように配置されたチューブ状部材4と、前記チューブ状部材4内で前記電子部品3を封止する第1のモールド樹脂5と、前記ケース1内で、前記チューブ状部材4で囲まれた領域の外側の前記回路基板2を封止する第2のモールド樹脂6と、を備える。前記回路基板2の上面2bに垂直な方向の前記第2のモールド樹脂6の厚さh2は、前記回路基板2の上面2bに垂直な方向の前記第1のモールド樹脂5の厚さh1より薄い。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体素子を搭載する基板と当該基板に接続する実装基板との接続部における応力を緩和して、接続品質が高く、生産性が高い半導体装置を提供する。

【解決手段】半導体装置は、基板1と、基板1に搭載された半導体素子3と、該半導体素子を覆うように形成された樹脂体2と、基板1の裏面に設けられた接続端子7とを備える。封止体2の上面には、環状の凹部8が形成されている。

(もっと読む)

半導体装置

【課題】小型化、薄型化、放熱性の要求が強い樹脂封止型半導体装置において、特に放熱性能に優れた半導体装置を提供する。

【解決手段】その第1主面に素子電極(図示せず)を有する半導体素子1と、その第1主面に半導体素子1が電気的に接続されたダイパッド2と、リード端子3と、前記素子電極とリード端子3のリード第1先端部3aとを電気的に接続する金属細線4と、リード第2先端部3bを露出する形で半導体素子1の周囲を封止する封止樹脂5と、封止樹脂5の下面に前記ダイパッド2の第2主面を露出する開口部5aとを備えることを特徴とする。この構成により、放熱性能に優れた半導体装置を提供する。

(もっと読む)

半導体装置とその製造方法

【課題】トランジスタが高性能化されるとともに製品の信頼性が向上した半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体素子32と、半導体素子32の上部に設けられ、内側に空洞部38を形成する枠材36と、枠材36の周囲を覆うモールド樹脂層42と、を備える。枠材36は同一の樹脂を含む樹脂膜(第1樹脂膜57a,第2樹脂膜58a)から形成されている。空洞部38内に半導体素子32の能動領域34が露出している

(もっと読む)

半導体装置

【課題】複数の半導体素子を搭載することで性能が効率的に向上する半導体素子を提供する。

【解決手段】本発明によって提供される半導体装置Aは、第1と第2の半導体素子41,42と、表面に第1と第2の半導体素子41,42がダイボンディングされた第1と第2のダイボンディングパッド11,21と、半導体素子41,42を覆う樹脂パッケージ60と、を備えており、上記第1のダイボンディングパッド11と上記第2のダイボンディングパッド21とは、第1の半導体素子41と第2の半導体素子42とが正対する配置とされており、かつそれぞれの裏面の少なくとも一部ずつが樹脂パッケージ60から露出していることを特徴とする。

(もっと読む)

半導体装置

【課題】低抵抗化による性能の向上を図ることが可能な半導体装置を提供する。

【解決手段】モールド樹脂6には、切り欠き部9が設けられている。切り欠き部9は、ソース側リード電極4の上部に位置するモールド樹脂6の端部から、このソース側リード電極4に接続されたコネクタ8に沿って溝状に形成されており、この切り欠き部9の部分において、ソース側リード電極4の上面及びコネクタ8の上面は外部に露出した状態となっている。

(もっと読む)

半導体装置およびその製造方法

【課題】 シリコン基板および該シリコン基板上に設けられた低誘電率膜と配線との積層構造からなる低誘電率膜配線積層構造部を備えた半導体装置において、低誘電率膜が剥離しにくいようにする。

【解決手段】 シリコン基板1の上面の周辺部を除く領域には低誘電率膜4と配線5との積層構造からなる低誘電率膜配線積層構造部3が設けられている。低誘電率膜配線積層構造部3の上面にはパッシベーション膜7および保護膜9が設けられている。保護膜9の上面およびシリコン基板1の周辺部上面には封止膜14が設けられている。これにより、特に、低誘電率膜配線積層構造部3の側面は封止膜14によって覆われ、低誘電率膜4が剥離しにくい構造となっている。

(もっと読む)

半導体メモリカードおよび半導体メモリカードの製造方法

【課題】ソケットへの挿入時に接点電極が削られるのを抑制し、接触不良を防止することが可能な半導体メモリカードを提供する。

【解決手段】本発明に係る半導体メモリカード100は、外部装置のソケットの接点電極と接続するためのコンタクト端子1が上面の先端側に形成された回路基板2と、この回路基板2の下面に載置され、コンタクト端子1とボンディングワイヤ3で接続された半導体メモリチップ4と、回路基板2表面上で半導体メモリチップ3を封止する第1の樹脂からなる第1の樹脂層5と、コンタクト端子1が形成された部分より少なくとも回路基板2の先端側に設けられ、第1の樹脂のよりも硬度が低い第2の樹脂からなる第2の樹脂層6と、を備える。

(もっと読む)

樹脂注型形電力用回路ユニット

【課題】ケースを大形にすることなく電子部品からの放熱を良好に行なわせることができるようにした樹脂注型形電力用回路ユニットを提供する。

【解決手段】高さが不揃いな複数の電子部品3ないし6を実装した回路基板2を一端が開口したケース1内に収容し、ケース1内に絶縁樹脂を注型することにより形成した樹脂モールド部8内に回路基板2と電子部品3ないし6とを埋設する。回路基板2に実装された電子部品3ないし6のうち、回路基板2の板面から測った高さが低い電子部品4,5に放熱フィン7cを有するヒートシンク7を熱的に結合する。ヒートシンク7は、放熱フィン7cを外部に露呈させた状態で、その一部を絶縁樹脂中に埋め込んでおく。

(もっと読む)

半導体メモリカードおよび半導体メモリカードの製造方法

【課題】 製造コストの低減を図ることが可能な半導体メモリカードを提供する。

【解決手段】 本発明に係る半導体メモリカード100は、所定の信号を入出力するための入出力端子1が上面側に形成された配線基板2と、配線基板2の下面側に形成されたパッド3と接続された半導体メモリ4と、配線基板2上に形成され配線基板2の側端部5で切断された、電解メッキに必要な電力を供給するためのメッキ配線6と、配線基板2上で半導体メモリ4を封止するとともに、配線基板2の側端部5および少なくとも1つのメッキ配線6の端部6aを封止する封止樹脂7と、を備える。

(もっと読む)

光電子半導体構成素子及び該構成素子のためのケーシング基体

少なくとも1つの放射線(11)を送出する半導体チップ(1)を備えた光電子半導体構成素子であって、前記半導体チップがケーシング基体(3)の切欠き(2)に配置されており、該切欠き(2)が、側方を半導体チップ(1)を取り囲む壁(31)によって制限されており且つ少なくとも部分的に被覆コンパウンド(4)によって満たされており、該被覆コンパウンドが、半導体チップ(1)を被覆しており且つ該半導体チップ(1)から送出される電磁放射線を良好に透過させる。切欠き(2)を制限する壁(31)の内面(32)が、半導体構成素子の正面側を上から見て半導体チップ(1)を完全に環状に取り囲む内面(32)の部分面(33)が形成されているように形成されており、該部分面が、放射線を送出する半導体チップ(1)から見て陰になっており且つ半導体チップ(1)を完全に取り囲みつつ少なくとも部分的に被覆コンパウンド(4)によって被覆されている。更に、このような半導体構成素子のためのケーシング基体が記載されている。  (もっと読む)

(もっと読む)

1 - 12 / 12

[ Back to top ]