Fターム[4M118DD09]の内容

Fターム[4M118DD09]の下位に属するFターム

Fターム[4M118DD09]に分類される特許

861 - 874 / 874

アクティブ画素センサーセル、その利用方法及び読み出し方法、画像センサー

アクティブ画素センサーセルは、少なくとも1つのフォトダイオード及びリセット回路及びフォトダイオードと結合された統合バラクタを有する。方法は、前記セルを読み出す。及び画像センサーは、前記セルのアレイを有する。フォトダイオードは、露光間隔の間、光子に露光され、フォトダイオードの第1の節点で一連の部分露光電荷を蓄積する。各部分露光電荷は、露光間隔の異なる部分露光間隔の間に第1の節点において蓄積する。フォトダイオードは、一連のリセット間隔のそれぞれの間にリセットされる。各リセット間隔は、部分露光間隔の異なる1つの前に生じる。露光間隔の間に記憶節点に蓄積された露光電荷を示す出力信号は、セルからアサートされる。露光電荷は、全ての部分露光電荷の和を示す

(もっと読む)

(もっと読む)

センサ回路の列回路における画素信号のビニングおよび補間

センサ回路内の列回路からの画素信号をサンプリングおよび補間するビニング回路と、それに関連する方法である。該ビニング回路は異なるセンサ回路列ラインからのアナログ画素信号とリセット信号をサンプリングする。ビニング回路において所定数の列ラインがサンプリングされると、サンプリングした画素信号を一工程で共に平均化し、別工程でリセット信号を共に平均化する。  (もっと読む)

(もっと読む)

CMOS撮像装置及びデジタルビデオ装置

CMOS撮像装置(300、400)は、分散されたフィードバックを提供するアクセス信号源を有する能動画素センサ(302)と、(利得及びFPN抑圧を有する)列バッファ(304)と、列バッファ(又は任意のアナログPGA)との間の実効伝送路が、リアクタンスとしてではなく、主として抵抗として機能するように、センサと併設されたA/D変換器(312)とを備える。この装置は、更に、アナログ利得増幅段及びデジタルプログラマブル増幅段(314,402)を備えていてもよい。  (もっと読む)

(もっと読む)

マルチモード・デジタル・イメージング装置およびシステム

【解決手段】本発明は、読み出し回路に接続されている検出器を有するデジタル・イメージング・アーキテクチャを提供するものであって、前記読み出し回路は特定のモードで機能し、前記モードは、前記検出器から前記読み出し回路に転送される入力信号の特徴、若しくは前記読み出し回路から要求される出力信号の特徴に基づいて使用することができる。例えば、前記入力信号がある特定の大きさを有する場合、前記読み出し回路は、前記入力信号を測定可能なレベルに増幅することができる第1のモードで機能し、前記入力信号が別の大きさを有する場合、前記読み出し回路は、別の増幅を伴う、若しくは増幅を伴わない前記入力信号を読み出し可能な代替モードで機能することができる。前記入力信号に様々なレベルの増幅を提供するために複数のモードを実装することが可能であり、例えば、3若しくはそれ以上の前記読み出し回路の動作モードを実装することができる。さらに、同じ入力信号の読み出しに2つ以上のモードを用いることも可能である。従って、本発明のデジタルイメージング装置およびシステムは幅広いダイナミックレンジの検出を提供することが可能であり、同ダイナミックレンジにより、高速なピクセル読み出し時間において、検出器からの敏感な信号を増幅して外部ノイズ源に対する前記入力信号のノイズ排除性を向上させ、更に増幅を殆どまたは全く行わずに、より大きな信号を読み出すことができる。また、本発明は、前記読み出し回路に電流減算回路を実装することによって、ダイナミックレンジの検出をさらに向上する手段も提供する。この電流減算回路は、例えば、電荷増幅率が高くなる場合に飽和する可能性のある、前記読み出し回路の一部を通って流れる総電流量を減少するために使用することができる。総出力電流の減少により、前記入力信号の増幅がより大きくなるため、より小さな入力信号の検出が可能となる一方前記読み出し回路内での飽和の可能性が低くなり、その結果、前記装置の前記ダイナミックレンジが拡大するものである。 (もっと読む)

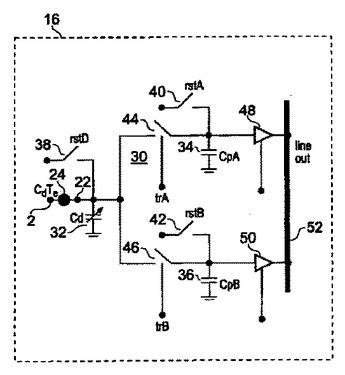

電離放射線検出装置

電離放射線を監視するためのアセンブリ(13)は、入射電離放射線に応答して電荷を生成すると共に、その中に形成された電離放射線検出ボリューム(12)のアレイを有する検出基板(2)を備える。検出ボリュームのアレイに対応する読出し回路(16)のアレイを支持するための回路基板(14)は、検出基板(14)に機械的かつ電気的に接続されている。各読出し回路(16)は、対応する検出ボリュームから電荷を受取るため、第一と第二の電荷集積モード間で切替え可能である。電荷集積回路(30)は、第一の電荷集積モードにおいて、対応する検出ボリュームにおける単一の電離放射線検出イベントの検出に対応して電荷を集積するとともに、第二の電荷集積モードにおいて、対応する検出ボリュームにおける複数の電離放射線検出イベントの検出に対応して電荷を集積するように、構成されている。別の実施例において、読出し回路構成は、光子計数回路構成(140)を含む。

(もっと読む)

(もっと読む)

固体撮像装置

【課題】画素構成の簡素化によって画素の縮小を図ることができ、また複数系統の出力構成とした場合の画素間のばらつきを抑制できる固体撮像装置を提供する。

【解決手段】単位セル30は2つの画素31、32を含み、上下2つの光電変換素子33、34と、それぞれに転送トランジスタ35、36と、1つのリセットトランジスタ37と、1つの増幅トランジスタ38で2つの画素31、32が構成されている。そして、全面選択信号配線39は、各リセットトランジスタ37と増幅トランジスタ38のドレインに接続されており、この全面選択信号配線39を転送信号配線42、43、リセット信号配線40とともに制御して、信号の読み出し動作を行うことにより、画素配線の簡素化、画素の縮小等を実現する。

(もっと読む)

固体撮像装置

【課題】デジタルカメラにおいて、CCDの不要電荷を掃き捨てる動作と、安定したCDS回路のクランプ動作との両立。

【解決手段】撮像素子の蓄積期間中に

1.垂直CCDは高速転送、あるいは、すべてLOW側の電圧に固定する。

2.水平CCDを停止させる。

3.フローティングディフュージョンアンプのリセットパルスは停止しない。

4.CDS回路に与えるクランプパルスは、常に出しておく。

とすることで、この間は、フローティングディフュージョンアンプの基準レベルをクランプするように構成する。

そのため、蓄積期間中に安定したクランプ動作が行える。

(もっと読む)

撮像装置および画像ピックアップシステム

【課題】デジタルカメラ等に使用されるMOS型撮像チップとDSPチップのチップセットに関するもので、高性能で高付加価値なチップセットを提供する。

【解決手段】半導体基板上に、入射光を光電変換し得られた電気信号を増幅する増幅型単位画素を一次元状または二次元状に配列した感光領域と単位画素を駆動するドライバ回路を有する撮像チップ220と、撮像チップ220から出力される信号を信号処理し、所望の信号に変換するデジタル信号処理チップいわゆるDSPチップ221からなるチップセットにおいて、DSPチップ221はCMOSで構成されており、撮像チップ220のトランジスタはnMOS型又はpMOS型のみの低リーク電流構造のトランジスタから構成される。

(もっと読む)

固体撮像装置およびその信号処理方法

【課題】 4画素加算を行うときに、行わないときの4倍の電流がカレントミラー回路の入力側に流れ込むと、カレントミラー回路の動作点が大きくずれて正常な動作が行われない。

【解決手段】 通常の撮像モードとn画素加算モード(モニターモード)とを選択的にとり得るCMOS型イメージセンサ等のX−Yアドレス型固体撮像装置において、カレントミラー回路23の入力側のMOSトランジスタ231に対して(n−1)個、本例の場合には3個のMOSトランジスタ234−1〜234−3を並列に接続し、これらMOSトランジスタ234−1〜234−3を加算画素数nに応じて動作状態にする。これにより、MOSトランジスタ231にn画素分の信号電流を流すのではなく、その平均の信号電流を流して、カレントミラー回路の動作点が大きくずれないようにする。

(もっと読む)

撮像センサ

【課題】 OPLFを用いることなく結像光学系の光学特性を活かした撮像装置を実現することのできる撮像センサを提供する。

【解決手段】 撮像センサはR,G,Bの三原色に感度を有する3種類の複数の受光素子がベイヤー型に配置された受光部を有している。受光部は画素位置(i,j)にフォトダイオードからなる受光素子PDij(i=1,2,…、j=1,2,…)を配置し、R,G,Bの各色毎に、同一色の隣り合う4個の受光素子PDijをそれぞれ1つのフローティングディフュージョンアンプからなる増幅回路FDA(q)(q=R,G,B)に接続した構成となっている。各増幅回路FDA(q)は対応する色の出力ラインLR,LG,LBに接続されている。露光によって各受光素子PDijで得られた電気信号は、各色毎に、隣り合う4個の電気信号が増幅回路FDA(q)で加算されて出力ラインLR,LG,LBから順次、出力される。

(もっと読む)

固体撮像装置

【課題】 入射光の利用効率を高めると共に、得られる画像の解像度をより高く実現できる固体撮像装置を提供することを目的とする。

【解決手段】 Yh補間部46で、実画素位置に市松状にデータを配置し、G信号位置では、撮像部から得られるG信号を2倍にし、Ye、Cy信号位置では自画素と周辺に位置するCy、Ye信号を50%の割合で加算し、等価的にGとMg(マゼンタ)を加算した信号を生成する。そして、データ補正部44で、ゲイン調整、補色を原色に色変換、ホワイトバランス、ガンマ補正等の各補正が行なわれたRGBの補正データと、Yh補間部46によって生成され、Hpf50を介して得られるYh信号とを加算器48で加算処理する。

(もっと読む)

撮像装置およびその駆動方法

【課題】 多数個の補色系画素が画素ずらし配置された固体撮像素子を利用した撮像装置であって、画素加算によって増感したときでも解像度の低下、偽色の発生および色のS/N比の低下を抑制することが容易な撮像装置は、未だ開発されていない。

【解決手段】 緑色画素とマゼンタ色画素とを交互に繰り返し配置した画素行と、シアン色画素と黄色画素とを交互に繰り返し配置した画素行とを、交互に繰り返し形成し、前記緑色画素と前記シアン色画素または前記黄色画素とを対象に画素加算を行うと共に、前記マゼンタ色画素と前記黄色画素または前記シアン色画素とを対象に画素加算を行う。

(もっと読む)

電荷検出信号処理回路

【課題】 CCDからFDAに転送された信号を処理する電荷検出信号処理回路のノイズ特性及び入出力特性を向上させること。

【解決手段】 ゲートがFDAに接続されソース・ドレインが電源VDDと出力端子Voutとの間に接続されたエンハンスメントNMOSトランジスタ101と、ゲートが電源VDDに接続されソース・ドレインが出力端子Voutと電源GNDとの間に接続されたエンハンスメント型NMOSトランジスタ102とを備える。

(もっと読む)

固体撮像素子およびその駆動方法並びにカメラシステム

【課題】 電子スチルカメラにおいて、モニタリングモードでは、フレームレートを上げることを目的として間引き読み出しの駆動方法が採られるため、スミアや暗電流等の垂直転送と同方向に乗るノイズ成分が問題となる。

【解決手段】 1垂直画素列の受光素子(画素)12の各々に対応する信号パケットと1垂直画素列につき少なくとも1個の空パケットを持つパケット列からなり、各画素から読み出される信号電荷を垂直方向に転送する垂直転送部13を具備するCCD撮像素子において、空パケットの成分をP(プリセット)相に乗せて出力するようにし、後段の信号処理系において、CCD撮像素子の信号出力VoutのD(データ)相の成分とP相の成分との差分をとることで、スミアや暗電流等の垂直転送と同方向に乗るノイズ成分を抑制する。

(もっと読む)

861 - 874 / 874

[ Back to top ]