Fターム[4M119FF13]の内容

MRAM・スピンメモリ技術 (17,699) | コンタクト (2,004) | コンタクトの場所 (1,215) | 記憶素子と上部配線間 (221)

Fターム[4M119FF13]に分類される特許

1 - 20 / 221

磁気抵抗効果素子、および磁気ランダムアクセスメモリ

記憶素子、記憶装置

【課題】書き込みエラーを生じることなく、短い時間で書き込み動作を行うことができる記憶素子及び記憶装置を提供する。

【解決手段】情報に対応して磁化の向きが変化される記憶層と、磁化の向きが固定された磁化固定層と、上記記憶層と上記磁化固定層との間に配された非磁性体による中間層とを含む層構造を有する記憶素子を構成する。そして上記磁化固定層が、少なくとも2つの強磁性層が結合層を介して積層され、上記2つの強磁性層が上記結合層を介して磁気的に結合し、上記2つの強磁性層の磁化の向きが膜面に垂直な方向から傾斜している。このような構成により、上記記憶層及び上記磁化固定層のそれぞれの磁化の向きがほぼ平行又は反平行とされてしまうことによる磁化反転時間の発散を効果的に抑えることができ、書き込みエラーを低減し、より短い時間で書き込みができる。

(もっと読む)

記憶素子、記憶装置

【課題】熱安定性の情報書き込み方向に対する非対称性をすくなくし特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。そして上記層構造の積層方向に電流を流すことで記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる。この場合に、磁化固定層を少なくとも2層の強磁性層とCrを含む非磁性層とを有する積層フェリピン構造とする。

(もっと読む)

記憶素子、記憶装置

【課題】熱安定性を確保して特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。その上で、上記層構造の積層方向に電流を流すことで記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる。そして記憶層は、Co−Fe−B磁性層と、少なくとも1つの非磁性層を有し、酸化物層、Co−Fe−B磁性層、非磁性層が順に積層された積層構造が形成されているようにする。

(もっと読む)

記憶素子、記憶装置

【課題】書き込みエラーを生じることなく、短い時間で書き込み動作を行うことができる記憶素子及び記憶装置を提供する。

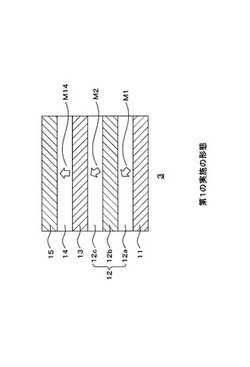

【解決手段】情報に対応して磁化の向きが変化される記憶層14と、磁化の向きが固定された磁化固定層12と、上記記憶層14と上記磁化固定層12との間に配された非磁性体による中間層13と、垂直磁気異方性誘起層15とを含む層構造を有する記憶素子3を構成する。そして、上記記憶層14が、第1の強磁性層14aと第1の結合層14bと第2の強磁性層14cと第2の結合層14dと第3の強磁性層14eとが同順に積層されて、上記第1の強磁性層14aが上記中間層13に接し、上記第3の強磁性層14eが上記垂直磁気異方性誘起層15に接し、上記結合層14b,14dを介して隣接する上記強磁性層14a,14c,14eの磁化の向きが膜面に垂直な方向から傾斜している。

(もっと読む)

記憶素子、記憶装置

【課題】熱安定性の情報書き込み方向に対する非対称性をすくなくし特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。そして上記層構造の積層方向に電流を流すことで記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる。この場合に、磁化固定層を少なくとも2層の強磁性層と非磁性層とを有する積層フェリピン構造とし、かつ、いずれかの上記強磁性層に接して反強磁性酸化物層が形成されているようにする。

(もっと読む)

記憶素子、記憶装置

【課題】環境温度によらず、熱安定性を確保して特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。そして上記層構造の積層方向に電流を流すことで記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる。この場合に、記憶層は正の磁歪定数を持つ磁性層を有するようにし、上記層構造に加えてさらに、負熱膨張材料層が設けられるようにする。

(もっと読む)

記憶素子、記憶装置

【課題】熱安定性を確保して特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。

そして、上記記憶層は非磁性体と酸化物が積層された積層構造層を含み、上記層構造の積層方向に電流を流すことにより、上記記憶層の磁化の向きが変化して、上記記憶層に対して情報の記録が行われる。

(もっと読む)

不揮発性メモリ

【課題】メモリセルへのデータの書き込みと読出しの信頼性を高くした不揮発性メモリを提供する。

【解決手段】2つのメモリセルを隣接させた基本ユニットを単位にするメモリセルアレイを有し、前記基本ユニットの2つのメモリセルのメモリセル選択用トランジスタのソース端子を共通のソース線に接続し、前記2つのメモリセルを2つのビット線に接続した抵抗変化型メモリであって、前記ソース線の配線パターンと前記ビット線の配線パターンを平行に走行させ、前記ソース線の配線パターンと前記ビット線の配線パターンの一部の領域を上下で重ねあわせて対向させる。

(もっと読む)

磁気記憶素子

【課題】書き込み電流を低減する。

【解決手段】磁気記憶素子10は、膜面に垂直方向の磁気異方性を有し、かつ磁化方向が可変である記憶層12と、記憶層12上に設けられた非磁性層13と、非磁性層13上に設けられ、かつ膜面に垂直方向の磁気異方性を有し、かつ磁化方向が不変である参照層14とを含む。記憶層12の面積は、参照層14の面積より大きく、記憶層12の端部の磁化は、記憶層12の中央部の磁化より小さい。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】MTJ素子内における層間の短絡を抑制し、かつ、MTJ素子を構成する磁性層の劣化を抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板を備える。磁気トンネル接合素子は、2つの磁性層と該2つの磁性層間に設けられたトンネル絶縁膜とを含み、半導体基板の上方に設けられている。側壁膜は、磁気トンネル接合素子の側面の上部に設けられている。フェンス層は、導電性材料を含み、側壁膜の側面および磁気トンネル接合素子の側面の下部に設けられている。フェンス層の頂点は、側壁膜の頂点よりも低く、かつ、トンネル絶縁膜よりも高い位置にある。

(もっと読む)

半導体磁気記憶装置

【課題】磁気記憶素子を構成する層を、周辺回路部内で有効に活用する。

【解決手段】実施形態によれば、半導体磁気記憶装置は、セルトランジスタを含むセル部と、周辺トランジスタを含む周辺回路部とが形成された半導体基板を備える。さらに、前記装置は、前記セル部内に配置され、下部電極と、前記下部電極上に形成された電極間層と、前記電極間層上に形成された上部電極とを含む磁気記憶素子を備える。さらに、前記装置は、前記周辺回路部内に配置され、前記下部電極を形成している第1の層と、前記電極間層を形成している第2の層と、前記上部電極を形成している第3の層とを含む構造体を備える。さらに、前記装置は、前記第1の層に電気的に接続された第1及び第2のプラグを備える。さらに、前記第1の層は、前記第1のプラグと前記第2のプラグを電気的に接続する配線として機能する。

(もっと読む)

半導体装置及びその製造方法

【課題】配線コーナーでの電子散乱を減らし、配線の抵抗率の増大を抑制する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板上に形成され、配線溝を有する層間絶縁膜とを備える。さらに、前記装置は、前記配線溝内に形成された配線を備える。さらに、前記配線溝の底面と側面との間の角部の曲率半径は、前記配線の配線幅の1/10以上である。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】チップ面積の縮小を図る。

【解決手段】磁気ランダムアクセスメモリは、メモリセル部の素子領域10a上に形成された第1の拡散層17aと、第1の拡散層に接続された第1のコンタクトCB1と、第1のコンタクト上に形成された第1の下部電極層21aと、第1の下部電極層上に形成された第1の抵抗変化層22a及び第1の上部電極層23aと、周辺回路部において互いに異なる素子領域に形成された第2乃至第4の拡散層17d、17eと、第2乃至第4の拡散層に接続された第2乃至第4のコンタクトCS1、CS2と、第1の下部電極層、第1の抵抗変化層、第1の上部電極層と同じ高さに形成された第2の下部電極層21b、第2の抵抗変化層22b、第2の上部電極層23bとを具備する。第2の下部電極層は、第2及び第3のコンタクトを接続する第1のローカル配線L1として機能する。

(もっと読む)

記憶素子及び記憶装置

【課題】書込電流と熱安定性をバランスさせた記憶素子の提供。

【解決手段】記憶素子は、情報を磁性体の磁化状態により保持する記憶層と、記憶層に記憶された情報の基準となる磁化を有する磁化固定層と、記憶層と磁化固定層の間に設けられる非磁性体による絶縁層とを有する。そして記憶層、絶縁層、磁化固定層を有する層構造の積層方向に流れる電流に伴って発生するスピントルク磁化反転を利用して上記記憶層の磁化を反転させることにより情報の記憶を行うとともに、記憶層のサイズが磁化の向きの変化が一斉に生じる大きさよりも小さくなっている。

(もっと読む)

半導体装置及び磁気ランダムアクセスメモリ

【課題】磁気ランダムアクセスメモリの読み出しマージンを増大させる。

【解決手段】メモリセル200は、磁気記録層2と、磁気記録層2に接合された固定層11、12と、磁気記録層2に対向するように設けられたリファレンス層41、42と、リファレンス層41、42と磁気記録層2との間にそれぞれに挿入されたトンネルバリア膜31、32とを備えている。固定層11、12は、互いに逆の方向に固定された磁化を有している。リファレンス層41、42とトンネルバリア膜31、32とは、固定層11、12の間の位置に設けられている。リファレンス層41、42は、互いに逆の方向に固定された磁化を有している。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】微細化されても、MTJ素子がコンタクトプラグ内のシームまたはボイドの影響を受けることなく、MTJ素子の特性の劣化を抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。複数のセルトランジスタは、半導体基板上に設けられている。コンタクトプラグは、隣接するセルトランジスタ間に埋め込まれ、該隣接するセルトランジスタ間にある拡散層に電気的に接続されている。層間絶縁膜は、複数のコンタクトプラグ間を埋め込む。記憶素子は、コンタクトプラグの上方に設けられておらず、層間絶縁膜の上方に設けられている。側壁膜は、記憶素子の側面の少なくとも一部を被覆し、半導体基板の表面上方から見たときに、コンタクトプラグに重複するように設けられている。下部電極は、記憶素子の底面と層間絶縁膜との間、および、側壁膜とコンタクトプラグとの間に設けられ、記憶素子とコンタクトプラグとを電気的に接続する。

(もっと読む)

磁気抵抗効果素子及びその製造方法

【課題】素子特性の劣化なしにリデポ現象による電気的ショートを防止する。

【解決手段】実施形態に係わる磁気抵抗効果素子は、磁化方向が可変の記憶層11と、記憶層11上のトンネルバリア層12と、トンネルバリア層12上の磁化方向が不変の参照層13と、参照層13上のハードマスク層14と、参照層13及びハードマスク層14の側壁上の側壁スペーサ層17とを備える。記憶層11及び参照層13は、垂直磁化を有し、参照層13の平面サイズは、記憶層11の平面サイズよりも小さい。記憶層11及び参照層13のサイズ差は、2nm以下であり、側壁スペーサ層17は、ダイアモンド、DLC、BN、SiC、B4C、Al2O3及びAlNのうちの1つを備える。

(もっと読む)

半導体装置、電子装置、配線基板、半導体装置の製造方法、及び配線基板の製造方法

【課題】配線基板に半導体素子を形成する場合において、配線基板の製造工程数を少なくする。

【解決手段】コア層200の一面上には、第1配線232が設けられている。第1配線232上、及びその周囲に位置するコア層200の一面上には、半導体層236が形成されている。第1配線232及び半導体層236は、半導体素子を形成している。本実施形態において半導体素子は、第1配線232をゲート電極としたトランジスタ230であり、半導体層236と第1配線232の間に、ゲート絶縁膜234を有している。

(もっと読む)

半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

(もっと読む)

1 - 20 / 221

[ Back to top ]