Fターム[4M119GG05]の内容

MRAM・スピンメモリ技術 (17,699) | レイアウト (382) | 周辺回路レイアウト (23)

Fターム[4M119GG05]に分類される特許

1 - 20 / 23

半導体記憶装置

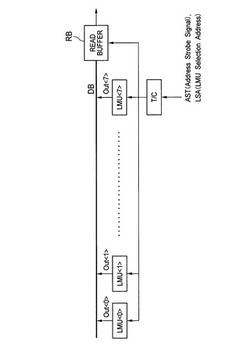

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

半導体装置

【課題】直流電源配線に電流が流れたか否かを検出可能な回路を備えた半導体装置を提供する。

【解決手段】半導体装置において、駆動回路BLDU,BLDD,BLBDU,BLBDDは、電流磁界またはスピン注入によってトンネル磁気抵抗素子TMR,TMRBを第1の磁化状態に初期設定するために、制御信号線BL,BLBに直流電流を流す。電源配線DLは、トンネル磁気抵抗素子TMR,TMRBに近接して設けられる。ここで、トンネル磁気抵抗素子TMR,TMRBは、電源配線DLに直流電流が流れるときに生じる電流磁界によって第2の磁化状態に変化する。センスアンプ10は、トンネル磁気抵抗素子TMR,TMRBが第1の磁化状態から第2の磁化状態に変化したか否かを判定するために、制御信号線BL,BLBを介してトンネル磁気抵抗素子TMR,TMRBに流れる電流を検出する。

(もっと読む)

磁気メモリ

【課題】磁気メモリの動作不良を抑制する。

【解決手段】本実施形態の磁気メモリは、第1領域内の第1の磁気抵抗効果素子1Aと、第2の領域の磁気抵抗効果素子1Xとを含む。第1の磁気抵抗効果素子1Aは、磁化の向きが可変な第1の記憶層10と、磁化の向きが不変な第1の参照層12と、非磁性層11と、第1のシフト調整層13と、を含む。第2の磁気抵抗効果素子1Xは、磁化の向きが可変な第2の記憶層10と、磁化の向きが不変な第2の参照層12と、第2の非磁性層11と、第2のシフト調整層13Xと、を含む。第2のシフト調整層13Xの膜厚t2は、第1のシフト調整層13の膜厚t1以下である。

(もっと読む)

情報格納装置

【課題】より容易な方法で集積度を向上させた情報格納装置を提供する。

【解決手段】本発明の情報格納装置は、基板と、基板上のゲートライン構造体を含むトランジスターと、少なくとも一部が基板内に埋め込まれてトランジスターの活性領域を定義する導電性分離パターン(conductive isolation patterns)と、を有し、導電性分離パターンは、互いに電気的に連結される。

(もっと読む)

半導体装置の製造方法

【課題】側壁マスクプロセスにより同時に異なる幅を持つパターンを形成する。

【解決手段】実施形態に係わる半導体装置の製造方法は、被加工材12上に第1及び第2の芯材を形成する工程と、第1及び第2の芯材の上面及び側面を覆う第1及び第2の層16a,16bを有する被覆材を形成する工程と、第1の芯材を覆う第2の層16bを除去する工程と、被覆材をエッチングすることにより、第1の芯材の側面に第1の層16aを有する第1の側壁マスクを形成し、第2の芯材の側面に第1及び第2の層16a,16bを有する第2の側壁マスクを形成する工程と、第1及び第2の芯材を除去する工程と、第1及び第2の側壁マスクをマスクとして被加工材12をエッチングすることにより、異なる幅を持つ第1及び第2のパターンを同時に形成する工程とを備える。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】孤立パターンに銅の化合物が析出するのを抑制する半導体装置の製造方法と、半導体装置とを提供する。

【解決手段】半導体装置では、素子・基板層ESLの低誘電率膜LOW1、ファイン層FLの極低誘電率膜ELK1等およびセミグローバル層SGLの低誘電率膜LOW2等のそれぞれの開口部に形成されるアライメントマークAMおよび重ね合わせ検査マークKMが、半導体基板SUBに形成された所定の導電型の不純物領域IRに電気的に接続されて、アライメントマークAMおよび重ね合わせ検査マークKMが接地電位に固定されている。

(もっと読む)

半導体装置

【課題】集積度の高い相変化メモリを実現する。

【解決手段】本発明による半導体装置は、複数のワード線と、複数のワード線と直交する複数のビット線との交点に配置された複数のメモリセル群を有する。複数のメモリセル群は、直列接続された第一乃至第二のメモリセルを有する。第一乃至第二のメモリセルの各々は、並列接続される選択トランジスタと抵抗性記憶素子とを有する。第一のメモリセルにおける選択トランジスタのゲート電極は、第一のゲート線に接続され、第二のメモリセルにおける選択トランジスタのゲート電極は、第二のゲート線に接続される。そして、複数のワード線を駆動する第一の回路ブロック(ワードドライバ群WDBK)は、第一乃至第二のゲート線を駆動する第二の回路ブロック(相変化型チェインセル制御回路PCCCTL)と、複数のメモリセル群(メモリセルアレーMA)との間に配置される。

(もっと読む)

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

半導体装置およびその検査方法

【課題】半導体基板上に形成された周辺回路上にさらに多層配線層が形成された構造の半導体装置において、周辺回路を構成する素子の特性を変化させずに周辺回路の不良解析を行うことができる半導体装置を提供する。

【解決手段】半導体基板11と、半導体基板11上に層間絶縁膜30を介して形成される多層配線構造を有する不揮発性メモリ層14と、半導体基板11上に形成され、不揮発性メモリ層14中のメモリセルを制御する回路を含む周辺回路12と、を備え、周辺回路12を構成する素子に接続され、周辺回路12の外部に引き出される配線35と、配線35の形成位置に対応する半導体基板11の上面から所定の深さまで設けられる拡散層27と、配線35と拡散層27との間を接続するコンタクト31と、を有する電極加工部15が、半導体基板11上の周辺回路12の形成領域R1以外の領域R2に形成される。

(もっと読む)

半導体集積回路

【課題】リードワード線およびライトワード線のドライブ回路を分割配置してレイアウト面線を減少させる。

【解決手段】

磁性体メモリセルMCは、メモリアレイに行列状に配置される。リードワード線RWL1〜RWLnおよびライトビット線WBL1〜WBLnは、磁性体メモリセルの行に対応して配置される。ライトワード線WWL1〜WWLmおよびリードビット線RBL1〜RBLmは、磁性体メモリセルの列に対応して配置される。この結果、リードワード線ドライバ30rおよびリードワード線ドライバ30wは、メモリアレイに対して異なる方向に隣接するように分割配置することができる。

(もっと読む)

抵抗変化型メモリ装置

【課題】 小型のセルを有し、大きな双方向電流を供給可能な抵抗変化型メモリ装置を提供する。

【解決手段】 抵抗変化型メモリ装置は、第1ノードと接続ノードとの間に並列接続された2つのトランジスタと、一端を接続ノードと接続され且つ抵抗値が異なる少なくとも2つの状態を有する抵抗変化素子と、を各々が具備し、第1軸および第2軸からなる行列状に配置された複数のメモリセルMCと、複数のビット線BLと、を含んでいる。各メモリセルの第1ノードと、このメモリセルの抵抗変化素子の他端である第2ノードとは別々のビット線と接続される。メモリセルの1つである第1メモリセルの第1ノードと、第1メモリセルと第2軸に沿った第1方向側で隣接するメモリセルの第1ノードとは、同じビット線と接続される。第1メモリセルの第2ノードと、第1メモリセルと第2軸に沿った第2方向側で隣接するメモリセルの第2ノードとは、同じビット線と接続される。

(もっと読む)

不揮発性記憶装置、集積回路装置及び電子機器

【課題】加工精度の向上等が可能な不揮発性記憶装置、集積回路装置及び電子機器を提供すること。

【解決手段】不揮発性記憶装置は、電気的に書き換え可能な不揮発性の複数のメモリーセル及び複数のビット線が配置される主記憶回路10と、電気的に書き換え可能な不揮発性の複数の情報メモリーセル及び複数のビット線が配置され、少なくとも主記憶回路10の不良メモリーセルのアドレス情報を記憶する情報記憶回路20と、主記憶回路10の複数のビット線のうちの対応ビット線と情報記憶回路20の複数のビット線のうちの対応ビット線との電気的接続をオン状態又はオフ状態にするための選択トランジスターが配置される選択回路30とを含み、情報記憶回路20は主記憶回路10と選択回路30との間に配置される。

(もっと読む)

半導体集積回路装置

【課題】複数のMTJメモリセルアレイを同一チップ内に含む半導体集積回路装置の製造工程を効率化する。

【解決手段】システムLSI100は、複数のMRAM回路ブロック110a〜110fを備える。MRAM回路ブロック110a〜110fは、MTJメモリセルが行列状に配置されるMTJメモリセルアレイ10a〜10fをそれぞれ含む。MTJメモリセルアレイ10a〜10fの各々には、書込データに応じて双方向のデータ書込電流を流すためのビット線BLが配置される。MTJメモリセルアレイ10a〜10fのそれぞれにおけるビット線BLの延在方向は、システムLSI100上で同一方向である。

(もっと読む)

薄膜磁性体記憶装置

【課題】メモリセルサイズの増加を招くことなく、安定的かつ効率的にデータ書込電流を供給可能な構成を備えた薄膜磁性体記憶装置を提供する。

【解決手段】各ビット線BLの両端には、データ書込電流を流すためのビット線ドライバ50が配置される。各ビット線の一端は、データ読出時に選択メモリセルからの読出データを伝達するための読出選択ゲート65を介して、データバスRDB1またはRDB2と接続される。読出選択ゲート65は、メモリセルアレイ10に対して、ビット線ドライバ50よりも外側に配置される。これにより、データ書込電流の電流経路を短くして、その経路抵抗を低減できるので、データ書込電流の確保が容易になる。

(もっと読む)

薄膜磁性体記憶装置

【課題】メモリセルサイズの増加を招くことなく、安定的かつ効率的にデータ書込電流を供給可能な構成を備えた薄膜磁性体記憶装置を提供する。

【解決手段】ライトディジット線WDLは、データ書込電流の供給時に電源配線90と接続される。ライトディジット線WDLは、電源配線90側の末端付近に、MTJメモリセルの配置位置に対応する定常部分93と比較して断面積を増大ざせた強化部分95を有する。これにより、定常部分93ではMTJメモリセルの最小設計ルールに従った配線幅とすることによってメモリセルを高集積に配置できるとともに、電源配線90側の末端付近で金属原子の移動による配線幅の減少が生じても、この部分で電流密度が局所的に増大して動作信頼性に影響を与えることを防止できる。

(もっと読む)

磁気ランダムアクセスメモリ及びその書き込み方法

【課題】コストの増加を抑制しつつ、磁化反転をアシストする。

【解決手段】スピン注入型の磁気ランダムアクセスメモリは、固定層11と記録層13と非磁性層12とを有し、固定層及び記録層の磁化は膜面に対して垂直方向を向く磁気抵抗効果素子10aと、磁気抵抗効果素子の一端に接続されたソース線SLaと、磁気抵抗効果素子の他端に電流経路の一端が接続されたトランジスタTraと、トランジスタの電流経路の他端に接続され、ソース線と平行に延在されたビット線BLと、磁気抵抗効果素子及びトランジスタを介してビット線及びソース線間に書き込み電流Iを流し、ビット線を通過した書き込み電流によって発生された磁場の磁気抵抗効果素子に対する印加方向が磁気抵抗効果素子を通過する書き込み電流の方向と反対であるソース/シンカとを具備する。

(もっと読む)

三次元六角形マトリックスメモリアレイとその製造方法

不揮発性メモリデバイスは、実質的に六角形のパターンに配置された複数の不揮発性メモリセルを含む。不揮発性メモリセルはピラー形の不揮発性メモリセルであってよく、これは三重または四重露光リソグラフィか自己集合層によりパターニングできる。セルは平行四辺形のサブアレイに配置される。ビット線は60度の角度でワード線と交差する。このメモリデバイスは三次元アレイにできる。  (もっと読む)

(もっと読む)

スピントロニクスチップ

【課題】コストをかけずに作製してチップに加わった磁場を不揮発に記録することによって、チップに加わる磁場の大きさや向きを推定することが可能なスピントロニクスチップを提供することを目的とする。

【解決手段】本発明の一実施形態によるスピントロニクスチップ1は、スピントロニクスを用いた素子を含む回路部2と、フリー層5とピン層6をトンネル膜7を介して積層してなるTMR素子3とが同一チップ上に配置され、TMR素子3によりチップに加わった磁場を不揮発に記録することが可能であることを特徴とする。

(もっと読む)

磁気抵抗性記憶装置

【課題】スピン注入型磁気メモリにおいて、チップ面積および消費電力を低減することができるドライバ配置を有する磁気抵抗性記憶装置を提供する。

【解決手段】メモリセルアレイにおいて、2つのビット線(BL<0>−BL<3>)あたり1つのコモン線(CL<0>−CL<1>)を設け、隣接列のメモリセルでコモン線を共有する。データ書込時にビット線およびコモン線をそれぞれ駆動するビット線ドライバおよびコモン線ドライバを、メモリセルアレイの両側に対向して配置する。メモリセルは、各行において各列ごとに異なるワード線に接続するように配置する。

(もっと読む)

磁気的に軟らかい基準層を有する磁気抵抗素子のための読出し方法

【課題】磁気的に軟らかい基準層を有する磁気抵抗素子のための読出し方法の提供。

【解決手段】データ層および基準層を含む磁気トンネル接合を有する磁気抵抗素子の読出し方法であって、ビット線の一端から当該ビット線の他端に読出し電流を供給し、前記基準層の磁化を既知の向きに一時的に設定する段階と、ワード線と前記ビット線の他端との間に、前記磁気トンネル接合を介して電圧を印加し、前記磁気トンネル接合にセンス電流を流す段階と、前記読出し電流と前記センス電流との和から前記磁気トンネル接合の抵抗を判定する段階と、を有することを特徴とする読出し方法。

(もっと読む)

1 - 20 / 23

[ Back to top ]