Fターム[4M119JJ10]の内容

MRAM・スピンメモリ技術 (17,699) | 製造方法 (929) | 貼合せ (4)

Fターム[4M119JJ10]に分類される特許

1 - 4 / 4

磁気メモリチップを有する半導体装置の製造方法

【課題】アセンブリ段階において外部磁場から磁気メモリチップを保護する。

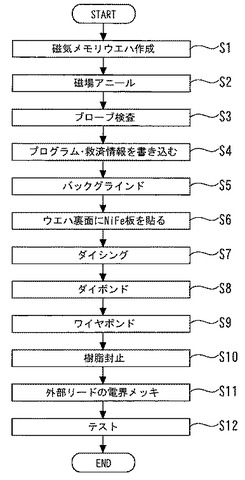

【解決手段】主面に磁気メモリ素子および複数のワイヤボンドパッドが形成された磁気メモリチップを準備する。シリコンより高透磁率を有する第1の磁気シールド板を磁気メモリチップの主面に搭載する。磁気メモリチップをリードフレームのダイパッド上に搭載しダイアタッチフィルムにより接着する。磁気メモリチップのワイヤボンドパッドとリードフレームのリードとをワイヤで電気的に接続する。磁気メモリチップ、磁気シールド板、ワイヤ及びリードの一部を樹脂により封止する。複数の磁気メモリチップを有するシリコンウェハを準備し、シリコンウェハの裏面を研削することによりシリコンウェハを所定の厚さまで薄くしてダイアタッチフィルムを張り付けた後にシリコンウェハをダイシングして各々がダイアタッチフィルムをその裏面に有する複数の磁気メモリチップを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】磁気シールド材と半導体チップとの各材料の線膨張係数の差に基づく反りを小さく抑制できる半導体装置およびその製造方法を提供する。

【解決手段】リードフレームLFのダイパッドDP上に磁気シールド材PM1が配置されている。半導体チップCHは、MRAMデバイスを有し、かつ磁気シールド材PM1上に配置されている。接着材AD2は、磁気シールド材PM1と半導体チップCHとを接着するために磁気シールド材PM1と半導体チップCHとの間に位置し、かつDAFのような熱可塑性樹脂を含む材質よりなっている。

(もっと読む)

機能素子の製造方法および機能材料の製造方法

【課題】ボトムアップ系とシリコンLSIに代表されるトップダウン系との利点を最大限活かすことができる高機能の機能素子を従来のクリーンルームを用いることなく、高い歩留まりで製造する方法を提供する。

【解決手段】局所的な相互作用により形成される第1の構造と予め設定された大局的な規則により形成された第2の構造とが、1次元超格子を薄片化した超格子薄片を複数交差させて重ねたものからなる第3の構造を介して結合されてなる機能素子を製造する場合に、防塵フィルター256を用いて作業室251をクリーンな環境に維持するクリーンユニットを用いる。防塵フィルター256は送風動力を有し、作業室251から流出する気体の全てが防塵フィルター256の入り口に入るように構成する。

(もっと読む)

レーザ移動を用いて感熱基板上に移植した磁気ランダム・アクセス・メモリ(MRAM)デバイスおよびこれを製造する方法

【課題】 ポリマおよびプラスチック等の低温基板上に磁気メモリ・デバイスを製造する方法を提供する。

【解決手段】 低温基板上に磁気メモリ・デバイス(およびその結果として生じる構造)を形成する方法は、メモリ・デバイスを、分解可能な材料層で被覆された透明基板上に形成し、所定の高圧を生成させる急速加熱を施すステップと、メモリ・デバイスを低温基板に移動するステップと、を含む。

(もっと読む)

1 - 4 / 4

[ Back to top ]