Fターム[5B001AB02]の内容

Fターム[5B001AB02]に分類される特許

1 - 20 / 181

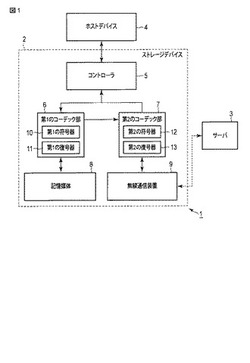

ストレージデバイス及び誤り訂正方法

【課題】ストレージデバイスにおいて、記憶媒体の記憶容量の低下を抑制しつつ、誤り訂正能力を向上させる。

【解決手段】実施形態に係るストレージデバイス2は、第1の符号器10と、記憶媒体8と、第2の符号器12と、無線通信部9とを含む。第1の符号器10は、書き込みデータの少なくとも一部に対応する第1の情報部と、第1の情報部の訂正に用いられる第1の冗長部とを含む第1の符号語を生成する。記憶媒体8は、第1の符号語を記憶する。第2の符号器12は、第1の符号語又は第1の情報部に対応する第2の情報部の訂正に用いられる第2の冗長部を生成する。無線通信部9は、第2の冗長部を、外部の記憶装置3へ無線通信する。

(もっと読む)

半導体メモリ装置および復号方法

【課題】復号効率がよい半導体メモリ装置1を提供する

【解決手段】半導体メモリ装置1は、半導体メモリ部3と、LDPC符号化データをサムプロダクトアルゴリズムを用い復号する復号部18と、を具備し、復号部18が、検査行列の行毎に、行処理演算と列処理演算とからなるイタレーション処理を繰り返し実行することで事後尤度比を更新するときに、列処理演算において事後尤度比の絶対値が閾値以上の場合、列要素尤度比には事後尤度比をそのまま使用し、事後尤度更新処理において、列要素尤度比の絶対値が前記閾値以上の場合、事後尤度比には列要素尤度比をそのまま使用する。

(もっと読む)

誤り訂正装置、誤り訂正方法及び演算装置

【課題】RAS機能の性能を向上させる。

【解決手段】ECC生成回路110は、各バイトがnビットのデータを有するmバイトの情報部データと、その情報部データの1バイト毎に1ビットずつ設けられた合計mビットのパリティビットとを含むデータの情報部データから、情報部データの誤りを訂正する誤り符号を構成するビットのうち、そのパリティビットに一致するビット以外のビットを生成する。エラー検出・訂正部140は、上述のデータの排他的論理和を生成して、情報部データの誤りの検出を行い、誤りが検出された場合には、情報部データの誤りの訂正を、上述のデータに含まれるパリティビットと、生成された誤り訂正符号の部分とを用いて行う。

(もっと読む)

マルチチャネルを有するメモリ装置及び同装置における誤り訂正チャネル決定を含む書き込み制御方法

【課題】誤り訂正チャネルを適用していながら、データ読み出しの並列度を向上できるようにする。

【解決手段】実施形態によれば、誤り訂正チャネル決定手段は、論理ブロックを構成する複数の論理ページがページ単位に複数のチャネルを介してメモリに書き込まれる際に、複数のチャネルのそれぞれに誤り訂正チャネルが割り当てられる論理ページの数が均等になるように、ページ単位に誤り訂正チャネルが割り当てられるチャネルを決定する。コマンドリスト生成手段は、誤り訂正チャネルが割り当てられるチャネルの決定に基づいて、複数のチャネルのうちの誤り訂正チャネルを除くチャネル群を介して、対応する論理ページを並列に書き込むためのライトコマンド群のリストを生成する。コマンドリスト投入手段は、ライトコマンド群のリストをメモリインタフェースに投入する。

(もっと読む)

メモリコントローラ及びメモリコントローラの動作方法

【課題】メモリ装置を制御するメモリシステムのコントローラが提供される。

【解決手段】本発明のコントローラはコントローラによって受信された読出しベクトルのエラー位置多項式を演算するキー公式解き方部、演算されたエラー位置多項式及び前記エラー位置多項式の情報の中で少なくとも1つにしたがって受信された読出しベクトルのエラー数を測定する制御部、及び演算されたエラー位置多項式にしたがって受信された読出しベクトルのエラー位置を検索するチェン検索部に構成される。

(もっと読む)

エラー訂正装置、エラー訂正方法及びエラー訂正プログラム

【課題】半導体メモリに記憶したデータにソフトエラーが発生した場合に、ソフトエラーを修正して正しいデータを得ることを目的とする。

【解決手段】補正データ格納用メモリ9には、少なくとも格納時点においては同一のデータであった補正データであって、複数のビットからなる補正データが、3つ以上の奇数個の領域に格納されている。多数決処理部12は、補正データ格納用メモリ9の各領域に格納された補正データの間で各ビットの値について多数決をとり、多数決データを生成するとともに、各領域に格納された補正データの間で値が異なるビットを示す差異データを生成する。妥当データ復元処理部15は、多数決データが妥当条件を満たす妥当データになるように、差異データが示すビットの値を変更して妥当データを生成する。

(もっと読む)

データ転送装置、メモリ制御装置、およびメモリシステム

【課題】誤り訂正が発生したとしてもデータ伝送が待たされる時間を少なくし、データ転送に要する時間を短縮することが可能なデータ転送装置、メモリ制御装置、およびメモリシステムを提供する。

【解決手段】データ転送元の第1メモリ装置200の第1メモリアドレスと、データ転送先の第2メモリ装置の第2メモリアドレスと、転送データに誤りが検出されたか否かを示す誤り信号と、誤り訂正が完了して第2メモリ装置106に格納しているデータが有効であるか否かを示す有効信号を記憶する領域を複数含むデータ情報記憶領域109と、第2メモリ装置に格納しているデータのうち、データが有効であるメモリのアドレスである第2メモリ有効アドレスを出力し、第2メモリ装置の第2メモリ有効アドレスからデータを読出し、読出したデータと共に、第2メモリ有効アドレスに対応する第1メモリ装置のアドレスを転送する制御部108とを有する。

(もっと読む)

NANDフラッシュ・メモリにおける確率論的多層エラー訂正のためのシステム、方法、およびコンピュータ・プログラム

【課題】メモリからデータを検索するためのシステム、方法、およびコンピュータ・プログラムを提供する。

【解決手段】メモリからデータを検索するためのシステムを含むNANDフラッシュ・メモリにおけるエラー訂正。このシステムは、メモリと通信するデコーダを含む。デコーダは、メモリにおけるページ上に記憶されたコードワードを受信することを含む方法を実行するためのものであり、コードワードは、データおよびこのデータに応じて発生された第1の層のチェック・シンボルを含む。この方法は更に、コードワードが第1の層のチェック・シンボルを用いて訂正することができないエラーを含むと判定することを含み、これに応じて、第2の層のチェック・シンボルを受信する。第2の層のチェック・シンボルは、データの受信に応じて、更にコードワードを含むページよりも前に書き込まれたメモリにおける他のページの内容に応じて発生させる。第2の層のチェック・シンボルに応じてコードワードを訂正する。訂正したコードワードを出力する。

(もっと読む)

エラー訂正回路及びエラー訂正方法

【課題】固定的に生じているエラーを含む場合は、訂正能力を超えて訂正を行う。

【解決手段】エラー訂正回路は、入力データに含まれるエラーの種別を判別する第1のエラー検出回路1と、エラー種別が1バイトエラーか、2バイトエラーである場合に、当該エラーが特定のバイトに固定的に発生している固定エラーであるか否かを判定する固定エラー検出回路2と、2バイトエラーに固定エラーが含まれる場合に、固定エラーが発生しているバイトの代わりとなる代替バイトを繰り返し発生するデータ発生回路4と、2バイトエラーに固定エラーが含まれる場合に、代替バイトで固定エラーが発生しているバイトを置き換えて、2バイトエラーが1バイトエラーとなるまで誤り検出を繰り返す第2のエラー検出回路3と、第2のエラー検出回路3で入力データが1バイトエラーとなったことを検出したら、当該入力データのエラー訂正を実行するエラー訂正回路5とを有する。

(もっと読む)

RAID装置及びガロア体の積演算処理方法

【課題】ガロア体を用いてパリテイデータを生成する際に、高速にガロア体の積演算を実行する。

【解決手段】n台のデータストレージユニット(10−1〜10−16)の内、 (n−1)/2より大きな最小の整数をsとして、i=1〜s+1番目のデータストレージユニットのデータのガロア体の元として、α^(i−1)を、i=s+2〜n番目のデータストレージユニットのデータのガロア体の元を、α^(−i+s+1)を、重み付けとして、積演算を実行する。

(もっと読む)

周辺装置の設定情報のエラー検出を有するデータ処理システム

【課題】高い強固であり、且つ高い信頼性を有するデータ処理システムを提供する。

【解決手段】データ処理システムは、周辺装置用バスインタフェースと動作可能に接続された第1マスタと、周辺装置用バスインタフェースに動作可能に接続された複数の周辺装置とを含む。第1マスタは、前記周辺装置用バスインタフェースを介して複数の周辺装置の各々と通信する。該データ処理システムにおける方法は、第1マスタによって設定情報を複数の周辺装置のうちの第1周辺装置に書き込みを開始することを含む。書き込み開始に応答して、第1周辺装置に格納するために周辺装置用バスインタフェースを介して設定情報が供給される。設定情報の第1エラーシンドロームは、周辺装置用バスインタフェースによって生成される。供給された設定情報は第1周辺装置に格納され、第1エラーシンドロームは周辺装置用バスインタフェースの記憶回路に格納される。第1エラーシンドロームは、次のエラー検出中に、設定情報の完全性をチェックするように使用され得る。

(もっと読む)

データ処理回路及びデータ処理方法

【課題】データの処理時間を短縮するデータ処理回路及びデータ処理方法を提供する。

【解決手段】制御用ビットを含むデータを受信する受信回路211と、受信回路211から出力されたデータを保持する保持回路215と、受信回路211から出力されたデータのエラーを検出するエラー検出回路212と、エラー検出回路212により検出された制御用ビットのエラーである第1エラーを訂正する第1訂正回路と、エラー検出回路212で第1エラーが検出されないときは、保持回路215を経由したデータを出力し、エラー検出回路212で第1エラーが検出されたときは第1エラーが訂正されたデータを出力する出力選択回路と、を有する。

(もっと読む)

情報処理装置および情報処理方法

【課題】動作に重要なプログラムが書き込まれているフラッシュROM上の物理的な記憶領域のデータが不良になっている場合にもプログラムを実行できるようにする。

【解決手段】この情報処理装置は、複数のカラムを一単位とするブロック単位にデータを記憶可能な物理的な記憶領域を有するフラッシュメモリと、プログラムデータを複数のブロックに分けて前記物理的な記憶領域に書き込み、各ブロックに付与した第1のエラー訂正符号を前記物理的な記憶領域に書き込み、前記プログラムデータに付与した第2のエラー訂正符号を前記フラッシュメモリに書き込む書き込み装置とを備える。

(もっと読む)

誤り検出訂正回路、メモリコントローラ、および半導体メモリ装置

【課題】処理効率のよい誤り検出訂正回路1を提供する

【解決手段】LDPC誤り検出訂正回路1は、サイズpの単位行列からなるブロックと複数のシフトブロックとからなる検査行列Hをもとに、受信データを、p個のグループに分割するセレクタ23と、グループをY個のサブグループに分割するセレクタ36と、確率βを算出するためのLMEM変数を第1のアドレスと関連付けて格納するビットノード記憶部26と、外部値αを算出するためのTMEM変数を第2のアドレスと関連付けて格納するチェックノード記憶部31と、チェックノード記憶部31に格納されたTMEM変数に対してシフト値にもとづくローテイト値のローテイト処理を行うローテイター35と、サブグループ単位で並列演算処理を行う(p/Y)個の演算回路からなる演算ユニット30と、全体の制御を行う制御部20と、を具備する。

(もっと読む)

ソリッド・ステート・ストレージ・デバイスのsレベル・ストレージに入力データを記録するための方法、エンコーダ装置、およびソリッド・ステート・ストレージ・デバイス

メタデータタグを介した不規則なパリティ分布の検出

エラー訂正方法

【課題】訂正前データと訂正後データを記憶するメモリの規模を小さくでき、オーバーフローの発生を未然に防止することができるエラー訂正方法を提供することにある。

【解決手段】所定時間においてエラー訂正処理を行い、そのエラー訂正処理の間に、エラー訂正処理にかかる負荷を検出し、検出した負荷が大きいほど、所定時間に対するエラー訂正処理の割合を大きくする。

(もっと読む)

演算処理装置、情報処理装置および演算処理装置の制御方法

【課題】演算処理装置において、読み出されたデータのエラーを検出してからエラーを訂正して通常の動作状態に復帰するまでの時間を短縮すること。ハードウェアの量を減らすこと。

【解決手段】チェック部43が記憶部33の出力データのエラーを検出すると、演算制御部31はエラー検出信号EU_PDを出力する。演算制御部31は、記憶部33にエラーが発生したことを示すエラー識別信号GPR_DATA_ERRORを出力する。命令制御部36は、エラー検出信号およびエラー識別信号に基づいてキャンセル信号CANCELおよび訂正開始信号CORRECT_STARTを出力する。演算処理装置12は、キャンセル信号によって演算部32の動作を停止し、エラーの報告処理を開始する。演算処理装置12は、訂正開始信号によってエラー訂正部34でのエラーの訂正処理を開始する。エラーの訂正処理はエラーの報告処理と並行して行われる。

(もっと読む)

エラー検出・訂正符号生成回路及びその制御方法

【課題】 簡易な構成でエラー検出・訂正符号付きデータを生成することが課題である。

【解決手段】 各バイトがnビットを有するmバイトの情報部分とmバイトの情報部分に設けられるmビットのエラー検出用ビットの冗長部分とを含むエラー検出用ビット付きデータのmバイトの情報部分の排他的論理和演算を行い、エラー検出・訂正符号付きデータの冗長部分のうち、log2(n+1)ビットの一の部分を生成し、生成した一の部分とエラー検出用ビットとを入力してmビットの他の部分を生成する。

(もっと読む)

情報処理装置および情報処理方法

【課題】冗長ビットのビット長を抑制しつつ誤り訂正・検出の精度を向上させる。

【解決手段】誤り検出・誤り訂正を行う誤り制御を実現するための情報処理装置は、情報ビット列を取得する情報ビット列取得部と、情報ビット列に基づき、所定の符号を用いた符号化により、情報ビット列全体の誤り制御を実行可能な冗長ビット列を生成して、情報ビット列と冗長ビット列とを含む符号語を生成する符号化部とを備える。符号化部は、冗長ビット列に含まれる少なくとも1つのビットのそれぞれが、情報ビット列を複数に分割したビット列であって情報ビット列における連続した複数のビットにより構成されるビット列である分割情報ビット列の1つに対するパリティビットとしても機能するように、冗長ビット列を生成する。

(もっと読む)

1 - 20 / 181

[ Back to top ]