Fターム[5B005MM21]の内容

階層構造のメモリシステム (9,317) | 階層メモリの種類 (2,100) | バッファメモリ (133)

Fターム[5B005MM21]の下位に属するFターム

Fターム[5B005MM21]に分類される特許

21 - 25 / 25

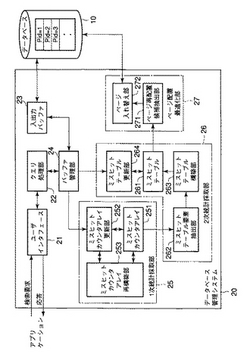

データベース管理システム、同システムにおけるページ配置最適化方法及びデータベース管理プログラム

【課題】データ格納手段におけるページ再配置が、再配置の効果の大きいページについて、システムに最適となるように行えるようにする。

【解決手段】ミスヒットテーブル261の各行及び各列には、データベース10内の全ページのうちの、例えばバッファミスヒットの頻度が高い上位一定数のページの各々が対応付けられる。ミスヒットテーブル更新部264はバッファミスヒット時に、ミスヒットテーブル261の、直前にバッファミスヒットしたページに対応する例えば行と、今回バッファミスヒットしたページに対応する例えば列とで決まる、当該テーブル261の配列要素の値をインクリメントする。ページ配置最適化部27は、テーブル261内の各配列要素のうち、例えば閾値を超える配列要素の、行及び列にそれぞれ対応付けられたページのデータがデータベース10内で連続するようにページを再配置する。

(もっと読む)

プロセッサと外部周辺装置との間の通信を制御するコントローラおよび方法

本発明は、マルチスレッド・オペレーティング・システムに基づくデータ処理システムに関する。このデータ処理システムは、複数のスレッドに基づいてデータを処理する少なくとも1つのプロセッサ(PROC)と、前記少なくとも1つのプロセッサ(PROC)と少なくとも1つのコントローラ・ユニット(CU)に接続された外部周辺装置(PD)との間の通信を制御する前記少なくとも1つのコントローラ・ユニット(CU)とを備える。前記少なくとも1つのコントローラ・ユニット(CU)は、前記少なくとも1つのコントローラ・ユニット(CU)に接続された前記周辺装置(PD)からのデータをバッファリングする少なくとも1つのバッファ・メモリ(BM)と、前記少なくとも1つのバッファ・メモリ(BM)を、それぞれが専用プリフェッチ・レジスタ(Addr_0−Addr_3)を有するN個のバンク(C0〜C3)にマッピングすることによって、前記少なくとも1つのバッファ・メモリ(BM)へのアクセスを管理する少なくとも1つのメモリ管理ユニット(MMU)とを備える。前記複数のスレッド(T0〜T3)のうちの少なくとも1つが、前記N個のバンク(C0〜C3)のうちの1つと、その専用プリフェッチ・レジスタ(Addr_0〜Addr_3)とにマッピングされる。  (もっと読む)

(もっと読む)

分岐ターゲットバッファと使用方法

【課題】分岐命令に関するデータエントリを貯蔵する分岐ターゲットバッファとその使用方法を提供する。

【解決手段】分岐ターゲットバッファは、分岐ターゲットバッファ内にあるワードラインと関連したワードラインゲーティング回路に応じてデータエントリに対するアクセスを条件的にイネーブルする。ワードラインゲーティング回路は、命令に関連した分岐ヒストリデータから誘導されたワードラインゲーティング値を貯蔵する。また、分岐予測ユニットと、分岐ターゲットバッファと結合されたプロセッサについて、分岐ターゲットバッファを動作するための方法と共に提供する。これにより、電力消費を減らし、分岐命令処理速度を高くし、全体的な複雑性を減らすプロセッサの実現と動作を可能にする。

(もっと読む)

データプロセッサ

CPUによってアクセス可能な内部メモリ(5)と外部メモリ(25,26)との間のデータ転送を高速化、高効率化するために、CPUによる特定の命令実行に応答してブロック転送制御部(12)にブロック転送を起動可能にする。特定の命令はそのアドレス指定フィールドで指定されたアドレスが内部メモリにマッピングされたアドレスであるとき当該論理アドレスをデータブロック転送の転送元又は転送先の一方のアドレスとする命令である。内部メモリは仮想アドレス空間の一部に割り付けられ、他方のアドレスとされる外部メモリが割り付けられる物理アドレス空間との対応は、MMUオンの場合にはTLBを用いて、MMUオフの場合には所定のレジスタにより行う。  (もっと読む)

(もっと読む)

組込みシステムのためのメモリ圧縮アーキテクチャ

命令コードおよびデータの両方を柔軟に圧縮することができる組込みシステム・アーキテクチャが開示される。  (もっと読む)

(もっと読む)

21 - 25 / 25

[ Back to top ]