Fターム[5B005NN01]の内容

階層構造のメモリシステム (9,317) | W/R制御 (1,413) | 要求元からのW/R (254)

Fターム[5B005NN01]の下位に属するFターム

書込み (151)

Fターム[5B005NN01]に分類される特許

1 - 20 / 103

複数の状態のプロセッサのための命令のキャッシング

複数のデータ・エレメントの収集及び分散

【課題】複数のデータ・エレメントの収集及び分散におけるオーバーヘッドを低減するプロセッサを提供する。

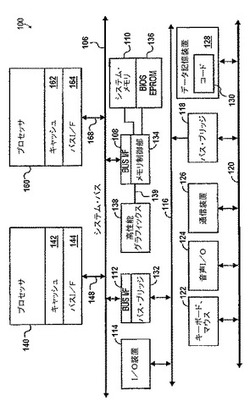

【解決手段】効率的なデータ転送処理は、単一の命令が複数のデータ・エレメントに対する第1の記憶域と第2の記憶域との間の転送処理を指定し、プロセッサ装置140,160によりデコードする段階、前記プロセッサ内の演算実行部による実行のために単一の命令を発行する段階、単一の命令の実行中に例外の発生を検出する段階、及び該例外に応答して、該例外を分配する前に、未解決のトラップ又は割り込みを例外ハンドラに分配する段階、により達成されうる。

(もっと読む)

記憶制御システムおよび方法、置換方式および方法

【課題】キャッシュ置換方法に関し、無駄なプリチャージを削減しメモリの消費電力を削減する。

【解決手段】DRAM100内のロウバッファ102は、メモリアレイ101から所定のデータ長を単位とするいずれかのデータを読み出して格納する。LLC206は、ロウバッファ102に記憶されたデータの一部をキャッシュデータとして抽出して記憶するキャッシュメモリである。MAC601において、LLC206の追い出し制御が実施される場合に、MRQ203のキューイング状態に基づいて近い将来ロウバッファ102にどのDIMMアドレスのデータが記憶されるかを予測する。MACにおいて、LLC上の追い出し対象範囲702のキャッシュデータデータの各物理アドレスをDIMMアドレスに変換する。変換された各アドレスと予測されたデータのアドレスとが一致した場合に、その一致アドレスに対応するキャッシュデータを優先してLLCから追い出す。

(もっと読む)

複数ノード間での通信方法、相互接続ポートおよび相互接続システム

【課題】複数のノード間での通信方法を開示する。

【解決手段】各ノードは、複数のプロセッサおよび相互接続チップセットを含み、第1のノード内のプロセッサからデータ要求を発行し、拡張ポート(またはスケーラビリティポート)を通してこのデータ要求を他のノードに渡す。また、データ要求に応答してメモリのアクセスを開始し、各ノード内の各プロセッサのプロセッサキャッシュをスヌープする。従って、該要求を発行するプロセッサを持つノード内の(あるいは別のノードの)プロセッサキャッシュまたはメモリ内のデータの格納場所を識別する。さらに、ルータシステムにて2つの直接結合されたノード間でデータを要求する方法と、相互接続システム内の3またはそれ以上のノード間でのデータ要求方法と、相互接続システム内のクロスケースの解消方法と、ノードを直接またはプロトコルエンジンを通して結合するための相互接続システムも開示する。

(もっと読む)

アクセラレータ用低コストのキャッシュ一貫性を維持するシステム

【課題】アクセラレータとCPUとの一貫性を維持しながら通信によるノード間の帯域幅の消費を低減する。

【解決手段】CPU210およびアクセラレータ220はマルチプロセッシング環境において個別のノードにクラスターできる。共有メモリ・デバイス212、222を収容する各ノード0、1は、他のノードでキャッシュされたかもしれない共有メモリのブロックを追跡するディレクトリを維持できる。そのため、コマンドとアドレスは、メモリ位置があるノード以外でキャッシュされたときに限り、他のノードのプロセッサおよびアクセラレータに送信できる。加えて、アクセラレータは一般的にCPUと同じデータにはアクセスしないため、最初の読み出し、書き込み、および同期の操作のみを他のノードに送信できる。データへの中間アクセスは一貫性を保たないで行える。その結果、一貫性を維持するために消費するチップ間の帯域幅を低減できる。

(もっと読む)

プログラマブルコントローラ

【課題】ラダー言語用のビット演算プロセッサを備えるプラグラマブルコントローラにおいて多発する、リードモディファイライトによるパイプライン処理の中断を防ぐ。

【解決手段】リードモディファイライトの対象データをバッファレジスタにロードするとともに対象データのアドレスをレジスタファイル152に保持しておくパイプラインステージR(リードステージ)の後ろに、ビット演算及びビットデータのマージを行うパイプラインステージEX(実行ステージ)を設け、その後ろにリードステージRにて保持したアドレスにマージ結果をストアするパイプラインステージW(ライトステージ)を設ける。

(もっと読む)

情報処理装置及び情報処理方法

【課題】キャッシュメモリが無効な状態でキャッシュライン中の複数の要素データをアクセスするロード命令に関し、実行性能を向上させる。

【解決手段】

情報処理装置400は、プロセッサ410、主記憶420、ネットワーク430を備え、主記憶420に記憶された要素データのうち、命令で指定された複数の要素データを1命令でアクセスできるメモリアクセス命令を命令セットに含む。プロセッサ410は、メモリアクセス命令に従って主記憶420にアクセスする場合に、メモリアクセス命令ごとに指定されたキャッシュラインの有効/無効と、当該キャッシュライン中における要素データの有効な数又は位置の少なくとも1つと、に基づいてアクセス対象バンクへの最適なアクセス単位を判定し、当該判定したアクセス単位でメモリアクセスリクエストを生成し、発行するメモリアクセスリクエスト生成発行手段440を備える。

(もっと読む)

情報処理装置

【課題】装置のクロック信号を停止させることなく消費電力を低減する。

【解決手段】メモリ12の特定の記憶領域へのアクセスの有無をクロック制御部19へ通知する通知部(アドレスデコーダ)21を具備し、クロック制御部19は、メモリ12の特定の記憶領域へのアクセスがないとき、第1のクロック周波数が第2のクロック周波数より高くなるように第1、第2のクロック周波数間の比率を制御し、通知部21からメモリ12の特定の記憶領域へのアクセスがあった旨の通知を受けたとき、第2のクロック周波数をアクセスがない時よりも上昇させる。

(もっと読む)

ディスクアレイ装置のエラー制御方法

【課題】ディスクアレイ装置に接続されるハードディスクのエラー処理が影響して,データ読出し/書き込みの応答時間が遅延することを抑止することである。

【解決手段】冗長化された記録デバイスが接続される状態において,ディスクアレイ装置から記録デバイスに対するコマンド発行時にホストコンピュータ応答用の記録デバイス処理時間を監視する事により,所定の時間を経過した場合に記録デバイスからの応答が無くてもホストコンピュータへ正常応答する事により,短時間での応答時間を実現する。

(もっと読む)

共有キャッシュメモリ装置

【課題】2個のプロセッサに、より高速に連携した処理を行わせることが可能な共有キャッシュメモリ装置を提供する。

【解決手段】共有キャッシュメモリ装置を、第1プロセッサが生成して第2プロセッサが利用するデータを記憶するための幾つかの監視対象記憶領域をデータメモリ部33に確保する機能、管理対象記憶領域毎に第1プロセッサによるデータの書き込みが行われたか否かを管理する機能、データの書き込みが完了していない監視対象記憶領域上のデータを要求するリード要求を受信したときに、その監視対象記憶領域へのデータの書き込みが第1プロセッサにより行われるのを待機してから、当該リード要求に応答する機能を有する装置として構成しておく。

(もっと読む)

キャッシュメモリおよびデータ処理装置

【課題】プロセッサと組み合わせて使用した時に、プロセッサによるバスアクセス回数を低減して、バスアクセスにかかるオーバーヘッドを削減できるキャッシュメモリの実現。

【解決手段】データ格納部21と、データ転送装置14によりまとめて転送されるライトデータを書き込むライト部22,24と、プロセッサ11からのリードアクセスに対してデータを読み出すリード部23,25と、転送される予定のライトデータの転送終了アドレスおよび実際に転送が行われたアドレスの先頭位置を保持するレジスタ26,28,31と、を備え、リード部は、先頭位置と先頭位置からリードデータがデータ格納部に記憶されている場合には読み出しを行い、転送終了アドレスと先頭位置との間の場合には対象データがデータ格納部に書き込まれるまで待機し、それ以外の場合は、MISSを通知するキャッシュメモリ。

(もっと読む)

キャッシュ装置及び情報処理装置

【課題】パイプライン処理を行うプロセッサの性能への影響が少ないソフトエラー訂正方式を実現する。

【解決手段】データアレイ43は、データとパリティビットを記憶し、チェックビットアレイ46は当該データのECCビットを記憶する。パリティチェック部44は、プロセッサ1からリード要求により、リード対象データとそのパリティビットをデータアレイ43から取得し、パリティビットを用いてリード対象データのパリティチェックを行う。データ誤りを検出した場合は、プロセッサ1に対してパイプラインストールを指示するストール指示信号を出力する。誤り訂正部47は、パイプラインストール中に、リード対象データのECCビットをチェックビットアレイ46から取得し、ECCビットを用いてリード対象データの誤り訂正を行い、誤り訂正後のリード対象データと、パイプラインストールの解除を指示するストール解除信号とをプロセッサ1に出力する。

(もっと読む)

情報処理装置、メモリ制御装置、メモリアクセス方法およびプログラム

【課題】複数のバンクにアクセスする場合にキャッシュメモリを効率よく利用する。

【解決手段】キャッシュメモリ120は、複数のバンクを備えるメモリ200の一部の領域に保持されているデータをエントリ単位で保持する。バスマスタ110は、複数のバンクに保持されている同一データへのアクセス要求を行う場合には、1つのアクセスアドレスを発行する。この発行により、キャッシュメモリ120には、同一データが保持されている複数のバンクにおける各メモリアドレスに対応する1つのエントリのみが登録される。メモリコントローラ130は、バスマスタ110からアクセスアドレスが発行された場合には、そのアクセスアドレスに基づいて、同一データが保持されている複数のバンクにおける各メモリアドレスを特定する。そして、その特定された各メモリアドレスのうちの1つのメモリアドレスにアクセスする。

(もっと読む)

キャッシュコントローラ及びその制御方法

【課題】キャッシュコントローラ内のキャッシュデータを破棄する際、プロセッサによる処理の負荷を軽減することができるキャッシュコントローラを提供する。

【解決手段】マスタからのアクセスが無効化範囲設定部121の条件に合致すると判定された場合、キャッシュコントローラ110は、無効化判定回路120及びタグメモリ改変部122により、タグメモリ111内の該当するアドレスのVALIDフラグ113を強制的にリセットする。これにより、VALIDフラグがリセットされた、該当するアドレスのキャッシュデータはメモリ104に書き戻されることなく破棄される。そして、マスタによってアクセスされるデータが該当するアドレスに従って上書きされる。

(もっと読む)

情報処理装置及びデータアクセス方法

【課題】メモリに格納されたストリームデータに対するアクセス効率を向上することができる情報処理装置及びデータアクセス方法を提供すること。

【解決手段】本発明にかかる情報処理装置は、ストリーム識別情報によって識別されるストリームデータを複数格納するメモリ2と、複数のストリームデータのストリーム識別情報に応じて、当該複数のストリームデータに割り当てられ、当該割り当てられたストリームデータをメモリ2から先読みする複数のチャネルユニット21、22、23、24であって、異なるストリーム識別情報によって示されるストリームデータに対して異なるチャネルユニットが割り当てられる複数のチャネルユニット21、22、23、24と、チャネルユニットが先読みしたストリームデータにアクセスするプロセッサ1と、を備える。

(もっと読む)

マルチコアプロセッサアーキテクチャにおけるデータ記憶およびアクセス

キャッシュに記憶されたデータブロックを送るためのシステムに関する技術が一般に記載されている。本明細書中に記載される幾つかの実施例では、システムが第1のタイルの第1のプロセッサを備えてもよい。第1のプロセッサは、データブロックの要求を発生させるのに有効であり、前記要求がデータブロックのための宛先タイルを識別する宛先識別子を含み、宛先タイルが第1のタイルと異なる。幾つかの実施例のシステムは、要求を受けるのに有効な第2のタイルを更に備えてもよく、第2のタイルは、データブロックを含むデータタイルを決定するのに有効であるとともに、要求をデータタイルへ送るのに有効である。幾つかの実施例のシステムは、第2のタイルから要求を受けるのに有効なデータタイルを更に備えてもよく、データタイルはデータブロックを宛先タイルへ送るのに有効である。  (もっと読む)

(もっと読む)

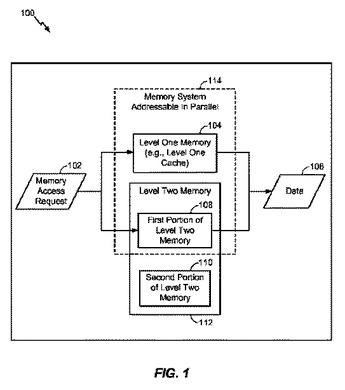

レベル2メモリの一部分とレベル1メモリとにアクセスするシステムおよび方法

レベル2メモリの一部分からのデータまたはレベル1メモリからのデータにアクセスするためのシステムおよび方法が開示される。特定の一実施形態では、本システムはレベル1キャッシュとレベル2メモリとを含む。レベル2メモリの第1の部分が入力ポートに結合され、レベル1キャッシュと並列にアドレス指定可能である。  (もっと読む)

(もっと読む)

マルチプロセッサ、これを用いたコンピュータシステム、およびマルチプロセッサの処理方法

【課題】プロセッサ単体の性能を向上させつつ、プロセッサ数を増やすことができるマルチプロセッサおよびその処理方法を提供する。

【解決手段】マルチプロセッサは、複数のプロセッサと、この複数のプロセッサで共有する共有キャッシュとを有し、複数のプロセッサのうちの空プロセッサを、プリフェッチ機能を使用可能なプリフェッチ専用プロセッサとし、このプリフェッチ専用プロセッサと対を成すプロセッサと共に1つのプログラム実行単位として、複数のプロセッサに最適化された複数種類のオブジェクトソースを実行する。

(もっと読む)

半導体集積回路装置およびキャッシュメモリ制御方法

【課題】処理ユニットの性能劣化を抑えつつ動作周波数を高速化することができる半導体集積回路装置およびキャッシュメモリ制御方法の提供を図る。

【解決手段】処理ユニット100と、該処理ユニットがアクセスするキャッシュメモリ200と、前記処理ユニットが前記キャッシュメモリにアクセスするアドレスを予測するアドレス予測回路401と、前記処理ユニットが前記キャッシュメモリへのアクセスを開始したことを検出してアクセス開始信号ASSを生成するアクセス開始検出回路402と、クロックCLKおよび前記アクセス開始信号を受け取って前記処理ユニットに対する処理クロックclkを制御するクロック制御回路403と、前記キャッシュメモリからのリードデータを遅延して前記処理ユニットに供給する遅延回路405と、を有するように構成する。

(もっと読む)

情報処理装置およびキャッシュメモリ制御装置

【課題】メモリアクセスをアウトオブオーダで処理する情報処理装置において、不要な命令再実行を確実に抑止し、処理性能の低下を招くことなく確実にTSO保証を実現する。

【解決手段】ロード命令の対象データがキャッシュ212から演算器400に転送された後にキャッシュ212のデータに対する無効化要求を受信し、受信した無効化要求の対象アドレスのキャッシュインデクスと一致するキャッシュインデクスを有するロード命令が命令ポート210に存在する場合、第1判定部214Aは、第1フラグ(RIM)を有効化する。命令ポート210のエントリに保持されたロード命令の対象データについてキャッシュミスした後に対象データが転送されてきたと判定した場合、第2判定部215Aは第2フラグ(RIF)を有効化する。命令再実行判定部216は、第1フラグおよび第2フラグがいずれも有効化されている場合に命令の再実行を指示する。

(もっと読む)

1 - 20 / 103

[ Back to top ]