Fターム[5B005NN22]の内容

階層構造のメモリシステム (9,317) | W/R制御 (1,413) | 転送制御 (519) | プリフェッチ (223)

Fターム[5B005NN22]の下位に属するFターム

分岐先のプリフェッチ (20)

Fターム[5B005NN22]に分類される特許

1 - 20 / 203

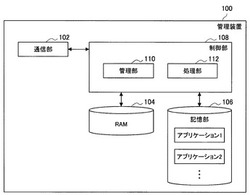

管理装置、管理方法、およびプログラム

【課題】複数のアプリケーションが順次に実行される場合において、効率的なメモリ管理を行うことが可能な、管理装置、管理方法、およびプログラムを提供する。

【解決手段】複数のアプリケーションの実行順序を示す実行制御情報に基づいて、アプリケーションが実行されるときにアプリケーションが一時的に記憶される記録媒体における、実行領域と、キャッシュ領域とを管理する管理部を備える、管理装置が提供される。

(もっと読む)

制御システム、制御方法およびプログラム

【課題】プリフェッチに使用される電力が無駄になることを防止可能な制御システム、制御方法およびプログラムを提供する。

【解決手段】制御システム100は、処理装置と主記憶装置とキャッシュメモリとプリフェッチ部と電源部とを備えた制御システムであって、検出部81と判定部82と電源制御部83とを備える。検出部81は、処理装置が処理を実行していないアイドル状態であるか否かを検出する。判定部82は、アイドル状態であると検出された場合、プリフェッチの状態に応じて、キャッシュメモリに対する電力の供給を停止するか否かを判定する。電源制御部83は、キャッシュメモリに対する電力の供給を停止すると判定された場合は、キャッシュメモリに対する電力の供給を停止するように電源部を制御し、キャッシュメモリに対する電力の供給を停止しないと判定された場合は、キャッシュメモリに対する電力の供給を継続するように電源部を制御する。

(もっと読む)

メモリ管理装置、メモリ管理方法、制御プログラム、および、記録媒体

【課題】適切なブロックサイズでデータの先読みを行う。

【解決手段】データ入出力部は、ページ単位で不揮発記憶装置からのデータの読み出しを要求し、読み出されたデータをバッファに記憶させる。プロファイル作成部は、先読み対象プログラムからの要求に従ってデータ入出力部により発行される不揮発記憶装置からのデータの読み出し要求の履歴を、先読みブロックサイズのブロック単位の読み出し位置およびサイズに変換した先読みプロファイルを作成する。先読み実行部は、先読みプロファイルに基づいて、不揮発記憶装置からバッファへの先読み対象プログラムのデータの先読みをデータ入出力部に要求する。本技術は、例えばメモリ管理装置に適用できる。

(もっと読む)

データ供給装置、キャッシュ装置、データ供給方法、キャッシュ方法およびプログラム

【課題】 データ供給装置において、受信の際に必要となる記憶領域(受信領域)が大きい。またノンブロッキング動作のときに受信領域からデータを保持する記憶領域への転送が必要となる。データを保持する記憶領域(データ領域)と受信領域とを一体化し、受信領域からデータ領域への転送をなくし、装置全体の回路規模を抑制するための技術を提供する。

【解決手段】 フェッチ手段に備えられたデータを保持する記憶領域の一部に受信領域を割り当て、プリフェッチ手段の出力する情報に従い、受信領域の割り当てを更新してデータを取得しフェッチ手段からデータを供給する。

(もっと読む)

キャッシュ制御方法、キャッシュ制御装置およびキャッシュ制御用プログラム

【課題】受信したデータをキャッシュメモリに書き込んで処理を行う場合に、大量のデータを受信する状況であっても、処理性能が低下することを抑制できるキャッシュ制御方法を提供する。

【解決手段】領域設定手段81は、予め定められた量の受信データを書き込み可能な領域である書き込み領域をキャッシュメモリに設定する。領域削除手段82は、書き込み領域に書き込まれた一部または全部の受信データに対する処理ごとに、その処理の対象になった受信データが書き込まれた領域を削除する。また、領域設定手段81は、受信データに対する処理ごとに、予め定められた量の受信データを受信した後に受信する受信データを書き込む位置に、受信データを書き込み可能な領域として、削除された領域に相当する量の領域を新たに設定する。

(もっと読む)

プロセッサ、情報処理装置、情報処理方法及びシステム起動プログラム

【課題】ハーバードアーキテクチャを採用している処理プロセッサにおいて、命令フェッチを行わなければ命令キャッシュに命令を格納しておくことができなかった。

【解決手段】本発明にかかるプロセッサは、命令を一時記憶する第1の記憶手段と、命令及びデータを一時記憶する第2の記憶手段と、前記第2の記憶手段に一時記憶されている命令を前記第1の記憶手段に転送する転送手段と、第3の記憶手段に格納されている命令を前記第2の記憶手段に読み込む第1の制御と前記転送手段に対して前記第2の記録手段へ読み込まれた命令を前記第1の記憶手段に対して転送させる第2の制御とを行う制御手段と、を具備する。本発明の構成によれば、命令フェッチを行うことなく、命令を一旦データキャッシュに読み込んだ後に転送することで命令キャッシュに格納することができる。

(もっと読む)

メモリアクセス制御回路、プリフェッチ回路、メモリ装置および情報処理システム

【課題】プリフェッチバッファのプリフェッチサイズを動的に切り替える。

【解決手段】モード切替レジスタ250はプリフェッチバッファ210におけるプリフェッチサイズのモード切替えをプロセッサから指示する。モード切替指示検出部225はプリフェッチバッファ210におけるプリフェッチサイズのモードを切り替える指示を検出する。転送状態監視部242はデータ転送処理部241におけるデータ転送処理が実行中か否かの状態を監視する。モード切替部227は、モード切替指示が検出された際にデータ転送処理が実行中でなければ、すみやかにプリフェッチバッファ210におけるプリフェッチサイズの切替を実行する。一方、モード切替指示が検出された際にデータ転送処理が実行中である場合には、モード切替部227はデータ転送処理の終了を待ってプリフェッチサイズの切替を実行する。

(もっと読む)

メモリシステム

【課題】キャッシュとプリフェッチがより有効となるメモリシステムを提供する。

【解決手段】実施形態のメモリシステムは、メモリと読み出した所定サイズデータを保持するキャッシュを有すチップと、キャッシュの出力を記憶するバッファと、キャッシュのデータのメモリ上の第1アドレスを管理するI/Fと、I/Fとバッファを制御する制御部を持つ。I/Fは、第2アドレスを受け取ると第1アドレスと一致を判定し、一致の時は、第1アドレスと一致するキャッシュのデータをバッファへ転送し、メモリの第2アドレスに所定サイズ分アドレスを加算したアドレスのデータのキャッシュでの存在を判断し、存在しない時は加算後アドレスのデータを所定キャッシュへ読み出し、不一致の時は、メモリの第2アドレスのデータを所定キャッシュを経てバッファへ転送し、メモリの第2アドレスに所定サイズ分のアドレスを加算したアドレスのデータを所定キャッシュに読み出す。

(もっと読む)

ベクトル演算処理装置、ベクトル演算処理方法およびベクトル演算処理プログラム

【課題】キャッシュメモリと主記憶装置との間の負荷を軽減し、ロードバッファの解放タイミングを早める。

【解決手段】投機的に実行されるベクトルロード命令が発行された場合に、ベクトルデータのバッファ領域M2を確保するロードバッファ管理部31と、メモリアクセスリクエストに基づいて要素データをキャッシュメモリM1又は主記憶装置9から読み出し、読み出した要素データをバッファ領域M2に格納させるキャッシュ処理部4と、投機的実行に成功した場合にバッファ領域の要素データをベクトルレジスタM3に転送してからバッファ領域M2を解放し、一方、投機的実行に失敗した場合にバッファ領域M2の要素データをベクトルレジスタM3に転送せずにバッファ領域M2を解放するベクトル処理部6とを備え、キャッシュ処理部4は投機的実行に失敗した場合に要素データの主記憶装置9からの読み出しを抑止する。

(もっと読む)

メモリアクセス判定回路、メモリアクセス判定方法、キャッシュ制御装置および電子機器

【課題】データ処理の高速化を可能とすること。

【解決手段】キャッシュ制御部32のキャッシュ判定部33は、カウンタ部22のカウント値CTに対応するアドレスADRをキャッシュ判定する。基準値算出部49は、アドレスADRに対するキャッシュヒットのヒット率HRと、キャッシュミスのときにカウント値CTに対応するアドレスADRに対するキャッシュミスのミス率MRとに基づいて、カウンタ部22がカウント値CTをカウントするための基準値m,nを変更する。

(もっと読む)

メモリ管理装置及びメモリ管理方法

【課題】不揮発性半導体メモリに記憶されているデータを、高速アクセス可能な記憶装置にアクセス発生前に記憶し、効率的なアクセスを実行する。

【解決手段】実施形態に係るメモリ管理装置3は、履歴管理部16、アドレス変換テーブル13、アドレス管理部17、先読みデータ管理部18を含む。履歴管理部16は、メインメモリ4として使用される不揮発性半導体メモリ61〜6kに記憶されているデータに対するアクセス履歴を管理する。アドレス変換テーブル13は、データについての論理アドレスと物理アドレスの変換テーブルを含む。アドレス管理部17は、アドレス変換テーブル13の第1の論理アドレスに対するアクセスの後にアクセスされる第2の論理アドレスをアクセス履歴に基づき決定し、第2の論理アドレスに対応する第2の物理アドレスを第1の論理アドレスに対応付けてアドレス変換テーブル13に登録する。先読みデータ管理部18は、第2の物理アドレスに対応するデータをバッファ11に格納する。

(もっと読む)

半導体集積回路、情報記憶方法

【課題】異常画像を発生させることなく、プリフェッチの読み出し時間を短縮することができる半導体集積回路及び情報記憶方法を提供すること。

【解決手段】メモリアービタ15にメモリアクセス要求を発行する周辺回路14の有無を監視するアービタアクセス監視手段35と、周辺回路14がメモリアービタ15にメモリアクセス要求を発行してない場合に、メモリアービタにメモリアクセス要求を発行し、命令又はデータをバーストリードするバーストリード手段37と、メモリ23からバーストリードされた命令又はデータをメモリアービタよりもCPU側で記憶するバッファ手段33,34と、命令のアドレスをデコードするアドレスデコード手段31と、命令又はデータが前記バッファ手段に記憶されているか否かを判定するアドレス判別手段32と、命令又はデータが前記バッファ手段に記憶されている場合は、バッファ手段に記憶されている命令又はデータをCPUに供給する、ことを特徴とする。

(もっと読む)

命令制御装置、及び命令制御方法

【課題】読み出し遅延を抑止する。

【解決手段】実施形態の命令制御装置は、受付手段と、記憶手段と、算出手段と、プリフェッチ手段と、実行手段と、取得手段と、特定手段と、更新手段と、を備える。受付手段は、プリフェッチ付きの読出命令を受け付ける。記憶手段は、読出命令を識別する識別情報と、距離情報と、を対応づけて記憶する。算出手段は、読出命令の読み出し先のアドレスと、記憶手段と、に基づいて、プリフェッチによる読み出し先のアドレスを算出する。プリフェッチ手段は、算出されたアドレスに対してプリフェッチを実行する。実行手段は、読出命令に従って、プリフェッチされたアドレスに対して読み出しを行う。取得手段は、読み出しの完了までの遅延時間を取得する。特定手段は、遅延時間に基づいて、次以降のプリフェッチで用いる距離情報を特定する。更新手段は、特定された距離情報を、識別情報と対応づけて記憶手段に記録させる更新を行う。

(もっと読む)

データ転送装置

【課題】PCI−eバスインタフェースを具備するチャネルハードウェアをメインフレームに搭載する際、システム装置内の大幅な変更無しにスループットの向上が実現できるデータ転送装置を提供する。

【解決手段】チャネルから主記憶を参照する場合に、実際の主記憶参照と並行してプリフェッチ動作を行い、参照の対象となるデータを先行してキャッシュに登録する。本発明によれば、PCI−eバスインタフェースを具備するチャネルハードウェアをメインフレームに搭載する際、データを先行してキャッシュに登録することでデータ転送のスループット低下を防止することができ、且つ主記憶内のデータ更新を反映することが可能なデータ転送装置を提供できる。

(もっと読む)

正確なプレデコードを保証する方法及び装置

【課題】同期された命令ストリングのプレデコードを保証する。

【解決手段】命令ストリングは、可変長の命令セットおよび組込データ320からの命令310を含む。命令セットにおける最短長さの命令に等しくなるようにグラニュールを定義し、命令セットにおいて最長長さの命令を構成するグラニュールの数をMAXに定義する。更に、組込データセグメントの終了を判定し、プログラムが命令ストリングにコンパイル又はアセンブルされる場合、長さMAX−1のパディング330を、組込データの終わりに、命令ストリング内に挿入する。パディングされた命令ストリングをプレデコードすると、たとえ組込データが可変長の命令セット内に存在する命令と類似するように偶然に符号化されても、プレデコーダは、パディングされた命令ストリング内の命令との同期を保つ。

(もっと読む)

情報処理装置及びデータアクセス方法

【課題】メモリに格納されたストリームデータに対するアクセス効率を向上することができる情報処理装置及びデータアクセス方法を提供すること。

【解決手段】本発明にかかる情報処理装置は、ストリーム識別情報によって識別されるストリームデータを複数格納するメモリ2と、複数のストリームデータのストリーム識別情報に応じて、当該複数のストリームデータに割り当てられ、当該割り当てられたストリームデータをメモリ2から先読みする複数のチャネルユニット21、22、23、24であって、異なるストリーム識別情報によって示されるストリームデータに対して異なるチャネルユニットが割り当てられる複数のチャネルユニット21、22、23、24と、チャネルユニットが先読みしたストリームデータにアクセスするプロセッサ1と、を備える。

(もっと読む)

命令フェッチ装置、プロセッサ、プログラム変換装置、および、プログラム変換方法

【課題】命令プリフェッチのためのネクストライン・プリフェッチによるペナルティを平均化して、スループットを改善する。

【解決手段】実行対象となっている命令を含むキャッシュライン(現ライン)の実行中に、それに続くキャッシュライン(ネクストライン)および現ラインに含まれる分岐命令の分岐先命令を含むキャッシュライン(分岐先ライン)の両者を命令キャッシュにプリフェッチする。分岐先ラインは、命令キャッシュにおける衝突を避けるため、ネクストラインと異なるラインアドレスになるように配置される。また、現ラインの分岐命令は、両ラインのプリフェッチを完了させるまでの余裕をもたせるため、現ラインの後半部分に配置される。

(もっと読む)

命令フェッチ装置、プロセッサ、および、プログラムカウンタ加算制御方法

【課題】命令プリフェッチのためのネクストライン・プリフェッチによるペナルティを平均化して、スループットを改善する。

【解決手段】加算制御レジスタ640は、プログラムカウンタ660の加算制御を行うためのデータとして、「増分語数」および「増分回数」を保持する。加算制御部650は、加算制御レジスタ640に保持されたデータに基づいてプログラムカウンタ660の加算制御を行う。プログラムカウンタ660は、実行対象となる命令のアドレスを計数するものであり、プログラムカウンタ値保持部661と加算部662とを備える。「増分回数」がゼロになるまで、加算部662によって増分値として「増分語数」の値が加算され、その度に「増分回数」が1つ減じられる。これにより、複数の命令列が混在したキャッシュラインにおいて目的の命令列の命令のみを実行していくことができる。

(もっと読む)

パケット処理最適化

【課題】データパケット処理の最適化を提供する。

【解決手段】ネットワークを介して送信されるデータパケットを受信する段階と、データパケットについて分類情報を生成する段階と、分類情報に基づきデータパケットについてメモリ格納モードを選択する段階と、選択されたメモリ格納モードを利用してデータパケットを処理する段階とを備え、パッケット処理モジュールは、プリフェッチ・モジュール、キャッシュ蓄積モジュール、及びスヌープ・モジュールにより構成される。

(もっと読む)

電源回復後のリロード機能付きキャッシュ

キャッシュを再配置する方法および機器が開示される。キャッシュの内容の少なくとも部分が、キャッシュから分離した場所に格納される。電源がキャッシュから切られ、いくぶんかの時間の後に回復される。電源がキャッシュに回復された後、それは、キャッシュから分離して格納されたキャッシュの内容の部分で再配置される。 (もっと読む)

1 - 20 / 203

[ Back to top ]