Fターム[5B005PP01]の内容

階層構造のメモリシステム (9,317) | 一致制御 (671) | 下位のメモリの一致制御 (259)

Fターム[5B005PP01]の下位に属するFターム

Fターム[5B005PP01]に分類される特許

1 - 12 / 12

メモリ要求を処理するためのシステム及び方法

【解決手段】

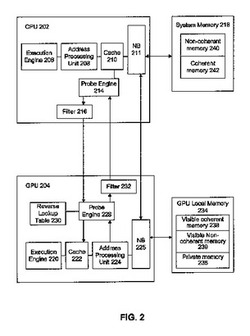

処理システムが提供される。処理システムは、第1のメモリに結合される第1の処理ユニットと、第2のメモリに結合される第2の処理ユニットと、を含む。第2のメモリは、コヒーレントメモリと、第2の処理ユニットにプライベートなプライベートメモリと、を備える。

(もっと読む)

キャッシュメモリシステムおよびキャッシュメモリ制御方法

【課題】演算装置がキャッシュメモリに一時データを書き込むときに生じる無駄なメモリアクセスを回避可能なキャッシュメモリシステムを提供する。

【解決手段】キャッシュメモリシステムは、複数のワードからなる複数のブロックを有するデータアレイ、複数のブロックのうち少なくとも1つのワードにデータが格納されたブロックに対応づけられた記憶装置のアドレス群を格納する格納手段、演算装置からの書込み時に演算装置からのアドレスが格納手段内にないと複数のブロックのいずれかを書込み用ブロックとして割り当てそのブロック内のいずれかのワードに演算装置からのデータを書き込む書込み手段、書込み用ブロック内のワードのうち書込み手段でデータが書き込まれたワードを示すワード情報を記憶するワード状態記憶手段、および、演算装置からの読み出し時にワード情報に示されたワードからデータを読み出した場合にワード情報を消去する読出し手段を含む。

(もっと読む)

信号処理装置

【課題】マルチコアシステムを備えた信号処理装置の性能向上。

【解決手段】キャッシュ用の複数の第1メモリと、各ステージを実行するためのプログラム103H〜103I、第1メモリに記憶されたデータ及び前記各ステージプログラム103H、Iの起動の予約情報を記憶する第2メモリ103と、各ステージプログラム103H〜Lを起動することによって、第1メモリ又は第2メモリに記憶されたデータに対してインバリデート処理、信号処理及びライトバック処理を行うステージを実行する複数のプロセッサと、を備え、各プロセッサは、第1ステージにおいて、前記第2ステージプログラム103Iの起動の予約情報103B、Cを前記第2メモリに記憶し、第2ステージにおいて、前記第2メモリに記憶された予約情報103B、Cに従ってインバリデート処理又はライトバック処理を省略する。

(もっと読む)

ハブ装置、プリフェッチ・モードを選択するための方法、メモリ・システム及びメモリ・サブシステム

【課題】メモリ装置用のプリフェッチ機能の可能化及び不能化のうち何れか一方を動的に選択するためのシステム及び方法を提供する。

【解決手段】

ハブ装置は、入力コマンド・ストリーム・インタフェース及び適応的プリフェッチ論理装置(APLU)を含む。前記入力コマンド・ストリーム・インタフェースは、前記ハブ装置に接続された1つ以上のメモリ装置に向けられる、メモリ・コントローラからのコマンドを検出する。前記APLUは、前記メモリ装置に対するアクセス・パターンを決定するためにこれらのコマンドを独立的に分析するとともに、かかる分析の結果に基づいて、前記メモリ装置用のプリフェッチ機能の可能化及び不能化のうち何れか一方を動的に選択する。

(もっと読む)

データおよび状態メモリを有する大メモリ容量のDIMM

【課題】本発明は、分散共用メモリ(DSM)マルチプロセッサの主メモリを実装するのに用いることができ、メモリを容易に更新または交換できるような機構を提供する。

【解決手段】ディレクトリに基づく分散共用メモリ・マルチプロセッサ・コンピュータ・システムにおいて使用するための大記憶容量デュアル・インライン・メモリ・モジュール(DIMM)は、データを記憶するためのデータ・メモリと、データの少くとも一部に対応する状態またはディレクトリ情報を記憶するための状態メモリとを含む。DIMMによりデータと状態情報を独立してアクセスすることができるようになる。DIMMは複数の記憶容量に構成することが可能である。

(もっと読む)

高速データ処理装置

【課題】I/Oデバイスを制御し、I/Oデバイスからのデータを格納し、CPUからもアクセスすることができる共有メモリを有するカスタムICと、共有メモリと共有メモリの一部のデータを格納するキャッシュメモリを有するCPUを備えた制御装置において、バススヌープ回路なしに共有メモリをキャッシング可能アドレス空間に配置できる高速データ処理装置を提供する。

【解決手段】カスタムIC103内にある共有メモリ107はI/Oデバイス112のデータのみを格納し、共有メモリアドレス空間はCPU101が使用するプログラム、ワークエリアとは別のエリアまたは、別バンクにマッピングし、キャッシュミスするアドレスに変換するアドレス変換回路201を備える。

(もっと読む)

キャッシュシステム

【課題】 本発明は、実現が容易なノン・インクルーシブ方式のキャッシュシステムを提供することを目的とする。

【解決手段】 キャッシュシステムは、主記憶装置にアクセスするよう機能する処理装置と、処理装置に結合され主記憶装置よりも高速にアクセス可能な1次キャッシュと、1次キャッシュを介して処理装置に結合され主記憶装置よりも高速にアクセス可能な2次キャッシュを含み、1次キャッシュと2次キャッシュは、処理装置からのアクセスに応じて主記憶装置から第1のデータを読み出す際に1次キャッシュと2次キャッシュとの両方に第1のデータを登録し、処理装置からのアクセスに応じて2次キャッシュの第2のデータを無効化する必要が生じた際に1次キャッシュに存在する第2のデータを無効化することなく2次キャッシュの第2のデータを無効化する動作を実行するよう構成される。

(もっと読む)

アドレス競合時のスタベーション防止方法およびチップセットおよびマルチプロセッサシステム

【課題】リトライとすべき先行トランザクションが、スヌープの結果リトライできないケースがある。スヌープ結果を待ってからリトライ判定を行うと、レイテンシが伸び、パイプラインが可変長になるため論理が複雑化する。

【解決手段】要求発行時にリトライ判定を受けたトランザクションを発行中のトランザクションと区別し、沈み込み保護対象のトランザクションがリトライ判定中のトランザクションと二度続けてアドレス競合した場合に、これを発行することで沈み込みを解消する。

(もっと読む)

タグ付きキャッシュ状態に基づいて下位レベル・キャッシュへの参照なしに相互接続ファブリック上にリクエストを送出するためのデータ処理システム、キャッシュ・システム、および方法

【課題】キャッシュ・コヒーレント・データ処理システムの提供。

【解決手段】メモリ・アクセス・リクエストをマスタが受けると、キャッシュ階層の上位レベル・キャッシュの第1キャッシュ・ディレクトリをアクセスする。ターゲット・アドレスが有効アドレス・タグおよび第1無効コヒーレンシ状態を有するエントリと関連付けられていることに対応して、即座に相互接続ファブリック上にターゲット・アドレスを指定するリクエストを送出する。ターゲット・アドレスが第一キャッシュディレクトリにおいて第2無効コヒーレンシ状態を有するエントリと関連付けられていることに応答して、キャッシュ・コヒーレンシの下位レベル・キャッシュの第2キャッシュ・ディレクトリにおいてターゲット・アドレスと関連付けられたコヒーレンシ状態を決定した後、相互接続ファブリック上にターゲット・アドレスを指定するリクエストを送出する。

(もっと読む)

マルチプロセッサ計算機、そのキャッシュコヒーレンシ保証方法及びキャッシュコヒーレンシ保証プログラム

【課題】 ソフトウェア的なキャッシュコヒーレンシの保証処理を資源の排他制御の一環として実装することで、低コストでキャッシュコヒーレンシの保証を実現する。

【解決手段】 複数のプロセッサ10−1〜10−Nと、各プロセッサ毎に設けられるキャッシュメモリ20−1〜20−Nと、プロセッサ間で共有される情報としての資源50−1〜50−Mを格納するメインメモリ40を備えるハードウェアによるキャッシュコヒーレンシを保証しない構成のマルチプロセッサ計算機であって、各プロセッサがメインメモリ40の資源に対して排他制御によりアクセスする時に、資源の最後の更新が他のプロセッサによってなされ、かつ当該資源の最後の更新以降に自身のキャッシュメモリのクリア処理が行われていない場合にのみ、プロセッサのキャッシュメモリのクリア処理を実行する。

(もっと読む)

メモリ・システムとその制御方法、データ・コヒーレンシを保つ方法

【課題】 データ・コヒーレンシを保ちつつ、ライト・アクセスを含むメモリ・アクセスの効率化を図る。

【解決手段】 バス10、11と、バスに接続するメモリ17、メモリ・コントローラ16、キャッシュを有する第1デバイス13、および第2デバイス15を備え、メモリ・コントローラは、キャッシュのデータおよび第2デバイスがメモリにライト・アクセスする場合におけるライト・データを一時記憶するためのバッファ20を含むことを特徴とするメモリ・システムを提供する。メモリ・コントローラのバッファに、キャッシュのデータおよび第2デバイスがメモリにライト・アクセスする場合におけるライト・データを一時記憶することにより、第2デバイスのライト・アクセス・リトライをなくしつつ同時にデータ・コヒーレンシを保つことができる。

(もっと読む)

キャッシュメモリ試験システム、試験方法、試験プログラム

【課題】複数のプロセッサが同一アドレス、および同一キャッシュラインに対し、非同期に連続アクセスを行うことで、キャッシュコヒーレンシ維持動作、アクセス結果のメモリ順序性検証を複合的に実施するキャッシュメモリ試験システムを提供する。

【解決手段】キャッシュを保持する複数のプロセッサがプロセッサバスを介してメモリに複数接続されるマルチプロセッサシステムのキャッシュメモリ試験システムにおいて、メモリに対して、ストア命令を連続的に実行するストア命令実行プロセッサと、メモリに対して、ロード命令を連続的に実行するロード命令実行プロセッサとを設け、各プロセッサが同時にメモリにアクセスした実行結果が、所定の期待値と一致するか否かを比較する実行結果比較手段と、比較した結果、一致するときにはメモリ順序性が保持されていると判断するメモリ順序性判断手段とを有することを特徴とするキャシュメモリ試験システム。

(もっと読む)

1 - 12 / 12

[ Back to top ]