Fターム[5B005QQ00]の内容

階層構造のメモリシステム (9,317) | 置換制御 (233)

Fターム[5B005QQ00]の下位に属するFターム

FIFO (9)

LRU (60)

ランダム (3)

データの優先度に基づくもの (113)

複数のアルゴリズムの切換 (17)

Fターム[5B005QQ00]に分類される特許

1 - 20 / 31

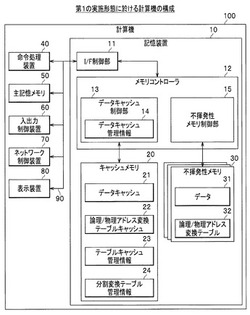

記憶装置および計算機

【課題】不揮発性メモリからキャッシュメモリへの書込回数を削減する。

【解決手段】記憶装置10は、不揮発性メモリ30とキャッシュメモリ20とメモリコントローラ12とを有する。不揮発性メモリ30は、分割データと格納場所を管理する論理/物理アドレス変換テーブル32を記録している。キャッシュメモリ20は、データキャッシュ21と、論理/物理アドレス変換テーブル32の一部を保持する論理/物理アドレス変換テーブルキャッシュ22を記録している。メモリコントローラ12は、外部からデータの読み出し要求を受けたとき、データキャッシュ21上に空きエントリが無かったならば、データキャッシュ21上の分割データのうち、論理/物理アドレス変換テーブル32のエントリが、論理/物理アドレス変換テーブルキャッシュ22に有るものを優先的に不揮発性メモリ30に退避して空きエントリを作成し、データを読み出す。

(もっと読む)

アドレス変換装置、アドレス変換装置の制御方法及び演算処理装置

【課題】エントリのヒット率の低下を抑制できるようにする。

【解決手段】仮想アドレスと物理アドレスとの対応関係を示すアドレス情報がそれぞれ記憶される複数のCAM回路を有するCAM部と、新たなアドレス情報を記憶させる場合に書込みポインタが示しているCAM回路にアドレス情報の書込みを指示する書込み制御部とを有するマイクロTLBにおいて、書込みポインタが示しているCAM回路に記憶されているアドレス情報が、アドレス変換に使用されたことが示されている場合には書込みポインタをインクリメントするようにして、アドレス情報の使用が示されたCAM回路に新たなアドレス情報が書込まれることを回避して最近使用されているアドレス情報を保持し、ヒット率の低下を抑制する。

(もっと読む)

マルチレベルのキャッシュ階層におけるキャストアウトを低減するための装置および方法

【課題】下位レベルキャッシュから置換されたキャッシュラインの上位レベルキャッシュへの割り当てを低減する方法を提供する。

【解決手段】置換ラインがすでに上位レベルに割り当てられと決定されたとき、置換されたキャッシュラインの割り当ては、次のレベルキャッシュにおいて防がれ、これにより、キャストアウトが低減する。そのような目的に、ラインは、下位レベルキャッシュ204において置換されるように選択される。上位レベルキャッシュ208において選択されたラインが存在するか示す選択されたラインに関連する情報が識別される。上位レベルキャッシュにおける選択されたラインの割り当ては、識別された情報に基づいて防がれる。選択されたラインの割り当てを防ぐことは、割り当てに関連するであろう電力を蓄える。

(もっと読む)

記憶制御システムおよび方法、置換方式および方法

【課題】キャッシュ置換方法に関し、無駄なプリチャージを削減しメモリの消費電力を削減する。

【解決手段】DRAM100内のロウバッファ102は、メモリアレイ101から所定のデータ長を単位とするいずれかのデータを読み出して格納する。LLC206は、ロウバッファ102に記憶されたデータの一部をキャッシュデータとして抽出して記憶するキャッシュメモリである。MAC601において、LLC206の追い出し制御が実施される場合に、MRQ203のキューイング状態に基づいて近い将来ロウバッファ102にどのDIMMアドレスのデータが記憶されるかを予測する。MACにおいて、LLC上の追い出し対象範囲702のキャッシュデータデータの各物理アドレスをDIMMアドレスに変換する。変換された各アドレスと予測されたデータのアドレスとが一致した場合に、その一致アドレスに対応するキャッシュデータを優先してLLCから追い出す。

(もっと読む)

情報処理装置、メモリ管理装置、メモリ管理方法、及びプログラム

【課題】キャッシュメモリから他の不揮発性半導体メモリへの書き戻しの効率化を図る。

【解決手段】実施形態に係る情報処理装置1は、メインメモリとして用いられる不揮発性半導体メモリ61〜6n上の第1のデータと、不揮発性半導体メモリ61〜6nのキャッシュメモリとして用いられる半導体メモリ5上の第1のデータと対応する第2のデータとの不一致が発生しているか否かを判断する第1の判断部91と、第1の判断部91によって第1のデータと第2のデータとが不一致であると判断された場合、第2のデータのアクセス頻度情報に基づいて、第1のデータと第2のデータとを一致させる書き戻しの実行タイミングを設定する設定部92と、第2のデータが最後に書き戻されてからの経過時間が、設定部92により設定された実行タイミングとなったか否か判断する第2の判断部93と、第2の判断部93によって、第2のデータの書き戻しの実行タイミングとなったと判断された場合、書き戻しを実行する書き戻し部94とを具備する。

(もっと読む)

置換領域選択装置、置換領域選択システム、置換領域選択方法、および置換領域選択プログラム

【課題】

通信装置において、記憶領域を効率的に使用する。

【解決手段】

置換領域選択装置は、データを格納する少なくとも1つの記憶手段に対する参照回数を記憶手段ごとに計測し、保持する参照回数保持手段と、記憶手段ごとに参照予定回数を保持する参照予定回数保持手段と、記憶手段ごとに参照回数と参照予定回数とを比較して、記憶手段ごとに参照回数が参照予定回数に達したか否かの判定を行う参照回数上限到達判定手段と、参照回数が参照予定回数に達している記憶手段を置換領域候補として選択する置換領域候補選択手段と、を備えることを特徴とする。

(もっと読む)

TLBサポート設計のIOMMU

【解決手段】

実施形態は、ページテーブルの構造及びフォーマットに依存しない改良されたトランスレーション挙動を有する入力/出力メモリ管理ユニット(IOMMU)のより小さくより単純なハードウエア実装を可能にする。実施形態はまた、デバイスに依存しない構造及び実装の方法を提供し、ソフトウエアのより大きな一般性を可能にする(より少ない特定のソフトウエアバージョンは同時に開発コストを低減する)。

(もっと読む)

キャッシュメモリ制御回路

【課題】複数のメモリ空間のデータをキャッシュメモリにキャッシュするキャッシュメモリ制御回路において、プロセッサの動作周波数の低減及びメモリアクセスのレイテンシの増加をさせることなく、消費電力を低減することができるキャッシュメモリ制御回路を提供する。

【解決手段】キャッシュメモリ制御回路は、それぞれがセット21a〜21d毎及びメモリ空間A及びB毎に設けられ、それぞれが対応するセットに対応するメモリ空間のデータがいくつ格納されているかをカウントする複数のカウンタ32a〜32d及び34a〜34dを有する。そして、キャッシュメモリ制御回路は、複数のカウンタ32a〜32d及び34a〜34dのそれぞれのカウント値に応じて、複数のセット21a〜21dのそれぞれのタグメモリ38a〜38d及びデータメモリ40a〜40dの活性化を制御する。

(もっと読む)

データ処理装置

【課題】キャッシュのヒット率を増加して処理時間を削減する。

【解決手段】データ処理システムは、コンピュータ10と、このコンピュータ10にネットワーク20を介して接続されたデータ処理装置(例えば、プリンタ)30とを備えている。プリンタ30は、1つの画像データを複数に分割した、それぞれの分割データを格納するデータ格納部34と、データ削除部35と、各分割データの関連を示す関連情報を格納する情報格納部36等とを有している。データ削除部35は、データ格納部34から所定のデータを削除する場合、この削除対象データが関連情報により、関連するデータがあると判断されたとき、関連する分割データに対し最後に使用される分割データから削除する。

(もっと読む)

データベース装置、キャッシュ装置、データベースシステム、キャッシュメンテナンス方法およびそのプログラム

【課題】データベースシステムにおけるキャッシュメンテナンス処理の負荷を軽減する。

【解決手段】データベース装置は、キャッシュ装置200のキャッシュトラック部により、キャッシュ231上の最新のキャッシュエントリを把握し、これをキャッシュ管理テーブル1312に記録する。データベース装置は、ベーステーブル1311の更新処理が発生したとき、キャッシュ管理テーブル1312を参照して、ベーステーブル1311の更新処理により影響を受け、かつ、キャッシュ231上に存在するベーステーブル1311上のデータを特定する。そして、データベース装置は、この特定したデータのキャッシュエントリの破棄メッセージをキャッシュ装置200へ送信する。キャッシュ装置200は、破棄メッセージにより指示された、キャッシュ231上のキャッシュエントリを破棄する。

(もっと読む)

リンクされているデータストアにおいて、アイテムの保存およびアイテムの上書きを決定するデータ保存プロトコル

【課題】複数のアイテムを保存するための記憶装置および方法を提供する。

【解決手段】記憶装置は、同一のクロックサイクルで、各アイテムにアクセスするための第1アクセス要求および第2アクセス要求を受信するように構成される。前記記憶装置は、複数のアイテムのサブセットをそれぞれ保存する2つのストアを具備し、第1アクセス要求は第1ストアに送信されるとともに、第2アクセス要求は第2ストアに送信され、前記記憶装置は、要求されたアイテムがアクセスされたストアに保存されていないというミスを検出するミス検出回路30と、アクセスがミスを起こしたアイテムを別のストアから読み出すアイテム読み出し回路と、個々のストアのアクセス履歴に従って2つのストアの各々に上書きするアイテムを選択するアップデート回路26とを具備する。

(もっと読む)

キャッシュメンテナンス装置、その方法及びそのプログラム

【課題】本発明は、データベースに高い頻度で更新処理が行われる環境においても、参照速度が低下せず、処理負荷の増大を最小限に抑えるキャッシュメンテナンス技術を提供する。

【解決手段】キャッシュメンテナンス装置1は、キャッシュエントリ更新情報を記憶する更新情報記憶部11と、メンテナンス条件を記憶するメンテナンス条件記憶部21と、メンテナンス条件を生成してメンテナンス条件記憶部21に書き込むメンテナンス条件生成部31と、メンテナンスの対象となるキャッシュエントリ1CEを選択するメンテナンス対象選択部41と、メンテナンス条件を満たすか否かを判定するメンテナンス判定部51と、キャッシュエントリ1CEをメンテナンスするキャッシュメンテナンス部61と、を備える。

(もっと読む)

印刷装置におけるメモリ管理用システム及びその方法

【課題】メモリ容量、記憶速度、キャッシュ容量、プロセッサ速度及びその他のシステムパラメータがプリンタ間で異なる印刷環境において、印刷キャッシュメモリの最適化を柔軟に行う。

【解決手段】キャッシュ内にオブジェクトが存在しない場合に参照カウントに初期値を割り当てる工程と、キャッシュ内にオブジェクトが既に存在する場合に参照カウントを第一の重み分だけインクリメントする工程と、ページ終了事象に応じて参照カウントを第二の重み分だけデクリメントする工程と、参照カウントが閾値未満の場合にキャッシュからオブジェクトを削除する工程と、を有する。

(もっと読む)

仮想メモリを利用したトランザクショナルメモリ実行

【課題】ハードウェアサポートなしにトランザクショナルメモリ実行が仮想メモリを利用することを可能にする。

【解決手段】ローカルトランザクショナルキャッシュを有するプロセッサと、要求元スレッドからのトランザクショナルメモリトランザクション要求に応答して、前記ローカルトランザクショナルキャッシュが前記トランザクショナルメモリトランザクション要求を収容可能であるか判断するリソースマネージャとから構成される装置であって、前記トランザクショナルメモリトランザクション要求が収容可能である場合には、前記ローカルトランザクショナルキャッシュは前記トランザクショナルメモリトランザクションを実行し、前記トランザクショナルメモリトランザクション要求が収容可能でない場合には、前記トランザクショナルメモリトランザクション要求が、前記要求元スレッドに係るアプリケーション仮想アドレス空間にオーバフローされる。

(もっと読む)

マルチレベルのキャッシュ階層におけるキャストアウトを低減するための装置および方法

技術および方法は、下位レベルキャッシュから置換されたキャッシュラインの上位レベルキャッシュへの割り当てを低減するために使用される。置換ラインがすでに上位レベルに割り当てられと決定されたとき、置換されたキャッシュラインの割り当ては、次のレベルキャッシュにおいて防がれ、これにより、キャストアウトが低減する。そのような目的に、ラインは、下位レベルキャッシュにおいて置換されるように選択される。上位レベルキャッシュにおいて選択されたラインが存在するか示す選択されたラインに関連する情報が識別される。上位レベルキャッシュにおける選択されたラインの割り当ては、識別された情報に基づいて防がれる。選択されたラインの割り当てを防ぐことは、割り当てに関連するであろう電力を蓄える。  (もっと読む)

(もっと読む)

マルチプロセッサシステム,システムボードおよびキャッシュリプレース要求処理方法

【課題】マルチプロセッサシステムに関し,キャッシュリプレース要求によってグローバルバスに負荷がかかることを防ぐことが可能となる技術を提供する。

【解決手段】CPU120aから発行されたリクエストは,CPUバス130a,CPU発行リクエストキュー112aを介し,ローカルアービタ113から出力される。キャッシュリプレース要求折り返し回路140は,折り返し判定回路141によって,出力されたリクエストがキャッシュリプレース要求か否かを判定する。キャッシュリプレース要求以外のリクエストは,ローカルバス300aに出力される。キャッシュリプレース要求は,セレクタ142に出力され,グローバルバス301に有効なリクエストがないタイミングで,リクエスト処理部114に送られる。

(もっと読む)

仮想化されたトランザクショナルメモリのグローバルオーバーフロー方法

トランザクショナルメモリを仮想化及び/又は拡張するための方法及び装置を記載する。トランザクションは、キャッシュメモリといったローカルの共有トランザクショナルメモリを用いて実行される。共有トランザクショナルメモリは、オーバーフローすると、システムメモリといった上位メモリ内へと仮想化/又は拡張される。現在ペンディングのトランザクションの間に前にアクセスされたキャッシュラインを退避させるといったオーバーフローイベントが発生すると、オーバーフローフラグがセットされて、トランザクショナルメモリはグローバルオーバーフローテーブル内に仮想化されるべきであることがプロセッサ/コアに通知される。グローバルオーバーフローテーブルのベースアドレスも上位メモリにおけるグローバルオーバーフローテーブルのベースを参照すべく格納されうる。 (もっと読む)

情報処理装置およびプログラムロード方法

【課題】プログラムを効率良くロードすることができるようにする。

【解決手段】ストレージデバイス30からメモリ113上にロードされるプログラムを実行する情報処理装置において、プログラム30が起動されてから個々のページがCPU111により参照されるまでの個々の時間が複数に区分された時間帯のうちのいずれに該当するかを前記個々のページのアドレスと前記時間帯との対応付けで示す管理情報を作成し、プログラム30が起動された後に、前記管理情報の中において1つの時間帯に対応付けられている個々のアドレスのページが一括してストレージデバイス30からメモリ113上にロードされるよう制御する。

(もっと読む)

上位レベル・キャッシュのエビクション候補を識別するための巡回スヌープ

【課題】 キャッシュ・ライン置換を改善することによって、コンピュータ・システムの性能を高める方法及び装置を提供する。

【解決手段】 上位レベル・キャッシュに保持されたキャッシュ・ラインのアドレス指定を順番に行い、それらのアドレスを用いて下位レベル・キャッシュのスヌープ読み出しを行う巡回スヌープ・シーケンサを有するコンピュータ・システムである。上位レベル・キャッシュに保持された特定のキャッシュ・ラインが下位レベル・キャッシュに保持されていない場合には、新しいキャッシュ・ラインが上位レベル・キャッシュにロードされなければならないときに、特定のキャッシュ・ラインが上位レベル・キャッシュ内のエビクション候補として識別される。

(もっと読む)

画像形成装置

【課題】 1段階の処理が終了した際に、同じプロセッサが処理データをそのまま引き続いて使用するような場合は、不要なフラッシュ処理は行わないようにして処理速度を向上させる。

【解決手段】 画像処理を、RIP処理,UCR処理,圧縮処理に分割し、プロセッサ13,14で、それらの処理を分担して実行する。その際、処理データを内部のキャッシュメモリ15,16に保持した後、データバッファ24にフラッシュし、該データバッファ24を介して処理データを受け渡しながら処理を進めていく。各プロセッサ13,14の処理状況を制御情報テーブル23に記憶し、制御部20は、それを参照し、各プロセッサ13,14の処理状況に応じて各プロセッサへの処理の割り当てを制御する。さらに、制御情報テーブル23を参照して、キャッシュメモリ15,16からデータバッファ24への処理データのフラッシュ処理を実行するか否かを決定する。

(もっと読む)

1 - 20 / 31

[ Back to top ]