Fターム[5B005SS13]の内容

階層構造のメモリシステム (9,317) | 例外処理 (115) | フォールト処理 (108) | TLBフォールト時の処理 (62)

Fターム[5B005SS13]の下位に属するFターム

セグメント、ページフォールト時の処理 (31)

Fターム[5B005SS13]に分類される特許

1 - 20 / 31

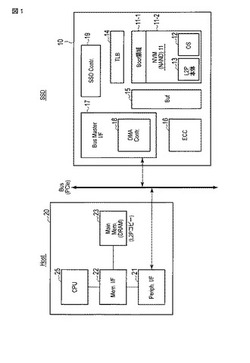

情報処理装置及び半導体記憶装置

【課題】製造コストの低減に対して有利な情報処理装置及び半導体記憶装置を提供する。

【解決手段】実施形態によれば、ホスト装置と、前記ホスト装置にバスを介して接続された半導体記憶装置とを備える情報処理装置であって、前記ホスト装置は、メインメモリを備え、前記半導体記憶装置は、第1の論物変換テーブル及びデータを格納する不揮発性半導体メモリと、前記第1の論物変換テーブルの一部である第2の論物変換テーブルを格納する記憶部と、前記第2の論物変換テーブルを参照し前記不揮発性半導体メモリにアクセスする制御部とを備え、前記第1の論物変換テーブルの少なくとも一部が前記メインメモリ上にコピーされ、前記第2の論物変換テーブルに前記制御部がアクセスする論理アドレス又は物理アドレスが登録されていない場合、前記メインメモリ上の第3の論物変換テーブルの一部が前記第2の論物変換テーブルにコピーされる。

(もっと読む)

変換索引マニピュレーション

【課題】多段パイプラインを有するプロセッサにおけるTLBミス時の非効率を改善する方法を提供する。

【解決手段】TLBミス信号に応じて、TLBコントローラはメモリあるいは高いレベルのTLBのいずれかからアドレス変換情報を要求するTLB再ロードを開始し、その情報をTLBの中に配置する。プロセッサはミスしている仮想アドレスを有するインストラクションをフラッシュし、そしてインストラクションをリフェッチし、結果的にインストラクションを再挿入する。TLB再ロードの開始およびインストラクションのフラッシュ/リフェッチは、直ちにパイプラインをストールすることなしに、実質的に平行して行われる。リフェッチされたインストラクションはTLB再ロードが完了するまでTLBアクセスポイント上部のパイプラインのポイントに保持され、リフェッチされたインストラクションが次のアクセスに際してTLB内に「ヒット」を発生する。

(もっと読む)

ページ属性サポートのある仮想アドレスから物理アドレスへの変換

【課題】ページ属性サポートのある仮想アドレスから物理アドレスへの変換のためのシステム、方法及び装置を提供する。

【解決手段】仮想メモリ・ポインタをあるメモリ位置についての物理的なメモリ・アドレスに変換する命令を受領する段階502と、仮想メモリ・ポインタをページ・テーブル情報に基づいて物理的なメモリ・アドレスに変換する段階504と、物理的なメモリ・アドレスおよび一つまたは複数のページ属性を返す段階506を含む。

(もっと読む)

DMAセキュリティチェック回路及びDMAセキュリティチェック方法

【課題】IO TLB(I/O Translation Look aside Buffer)でキャッシュミスした場合にDMAが待たされることを防止する。

【解決手段】IOV(I/O Virtualization) HBA(Host Bus Adapter)に対応したDMA(Direct Memory Access)セキュリティチェック回路が、HBAからのDMAリード要求に対しディスクリプタフェッチを検知した場合に、当該DMAリード要求のリプライデータの中から抽出した論理アドレスと、当該リプライデータに含まれるリクエストIDとが同じゲスト空間のものであるかを判定し、同じゲスト空間のものである場合に当該リプライデータに含まれるアドレスが適切であると判断する。

(もっと読む)

アーキテクチャイベントの間のプロセッサリソースの保持

【課題】アドレス空間のコンテクストの切り替えに関連するオーバヘッドを低減する。

【解決手段】本方法は、システムのプロセッサが、第一のアドレス空間と第二のアドレス空間との間でコンテクストを切り替えるステップ、第二のアドレス空間がプロセッサのスクラッチパッドメモリに記憶されているアドレス空間のリストに存在するかを判定するステップ、第二のアドレス空間がアドレス空間のリストに存在しない場合に、第二のアドレス空間へのコンテクストの切り替えの後に、第二のアドレス空間の新たなエントリであって、第一のアドレス空間の現在のエントリとは異なる新たなエントリを割り当てるステップ、及び第二のアドレス空間がアドレス空間のリストに存在する場合に、第二のアドレス空間へのコンテクストの切り替えの後に、第一のアドレス空間の現在のエントリをプロセッサの変換バッファに保持するステップ、を含む。

(もっと読む)

複数の仮想キューを含むアドレス変換ユニット

アドレス変換ユニットが、変換索引バッファ(TLB)、ミスキュー、及び制御ユニットを含む。TLBは、複数のアドレス変換を記憶することができる。ミスキューは、TLB内でミスになった受信アドレス変換要求を記憶することができる。ミスキューは、複数のエントリを含む。少なくともいくつかのエントリの各々は、それぞれのアドレス変換要求及び対応する識別子を記憶することができる。所与のエントリの対応する識別子は、所与のエントリ内のそれぞれのアドレス変換要求の処理順序制約と同じ処理順序制約を有する別のそれぞれのアドレス変換要求を記憶するミスキュー内の別のエントリを識別する。同じ処理順序制約を有し、識別子を介してともにリンクされたアドレス変換が同じ仮想ミスキューに属する。制御ユニットは、受け取ったアドレス変換要求を識別子に依存する順序で処理することができる。 (もっと読む)

プロセッサ及び演算処理方法

【課題】TLBスラッシング発生を抑制することにより、論理アドレスから物理アドレスへのアドレス変換を高速に行い、プロセッサの実行性能の向上を実現する。

【解決手段】TLB比較部20が、プログラムによるアクセス対象となるページの論理アドレスにおいてTLBミスが発生したと判定し、且つ、EAB比較部21が、当該論理アドレスが、既にアクセス対象となった論理アドレスが含まれるEAB17に存在しないと判定したとき、遅延制御部22が、ページテーブル25から対応エントリを読み出すタイミングを所定時間遅延させる。その後、ページテーブル読出部23が、ページテーブル25から対応エントリを読み出す。そして、登録部24が、当該読み出したエントリが示す物理アドレスを関連付ける新規エントリをTLB16に登録し、アドレス変換部19が、TLB16のエントリに基づいて論理アドレスを物理アドレスに変換する。

(もっと読む)

TLBプリフェッチング

一実施形態において、メモリマネージメントユニット(MMU)は、複数のページテーブルエントリーを含むデータのブロックを保持するように構成される。MMUは、TLBミスに応答してブロックをチェックし、ブロックに変換が見つかった場合には、その変換についてメモリ読み取りを発生せずにブロックから変換を供給するように構成される。ある実施形態では、MMUは、ブロックからの変換を使用したTLBミスの履歴も維持し、その履歴に基づいて第2ブロックのプリフェッチを発生する。例えば、その履歴は、最も最近使用されたQ個のページテーブルエントリーのリストであり、又、履歴は、ブロックの端に接近するアクセスのパターンを示す。別の実施形態では、履歴は、使用されたブロック内のページテーブルエントリーの数のカウントを含む。 (もっと読む)

凝集された小さいページを用いて拡張されたページサイズ

【解決手段】

仮想メモリページングメカニズムを含むプロセッサ。仮想メモリページングメカニズムは、プロセッサ上で動作しているオペレーティングシステムが、第1のサイズ及び第2のサイズのページを用いることを可能にし、第2のサイズは第1のサイズより大きい。メカニズムは、更に、オペレーティングシステムが第1のサイズの2つ以上の連続的なページを含むスーパーページを用いることを可能にする。スーパーページのサイズは第2のサイズより小さい。プロセッサは、更に、各スーパーページに含まれるページの各々に対して別個のエントリを有するページテーブルを含む。オペレーティングシステムは、単一の仮想アドレスを用いて各スーパーページへアクセスする。メカニズムは、トランスレーションルックアサイドバッファTLBにおける単一のエントリを、TLBにおけるエントリに関連するスーパーページ有効標識がアサートされていることを検出することに応答して、スーパーページに対応する一連のページを備えているメモリの領域を参照するものとして解釈する。

(もっと読む)

アドレスマッピング方法

【課題】プログラム実行時におけるTLBミスヒットの発生頻度を抑制できるアドレスマッピング方法を提供する。

【解決手段】TLB機構2のエントリの一部をタスクテキスト部専用エントリ21として確保する。専用エントリ21に対して、タスクAのテキスト部全体が収まるようにページサイズを指定し、論理アドレスおよび主記憶5上の物理アドレスを対応付けて設定する。さらに、専用エントリ21がTLBミスヒット発生時に変更されることを防ぐために、OSは専用エントリ21をロックして変更されないようにTLB機構2を管理する。

(もっと読む)

半導体集積回路及びアドレス変換方法

【課題】回路規模を大きくしないで、TLBヒット率を改善する半導体集積回路及びアドレス変換方法を提供する。

【解決手段】アドレス変換部を搭載した半導体集積回路は、マイクロTLB14と、メインTLB15と、CPU13を有する。CPU13は、プロセスの切替時に、切替元のプロセスのプライベートなマッピングを有するTLBエントリを、マイクロTLB14から読み出して、複数のプロセスのそれぞれのプライベートなマッピングを有するTLBエントリを、TLBのコンテキストとして記憶する複数のTLBコンテキスト記憶領域を有するTLBコンテキスト記憶部18における対応するTLBエントリ記憶領域に記憶し、切替先のプロセスのプライベートなマッピングを有するTLBエントリを、TLBコンテキスト記憶部18から読み出してメインTLB15に書き込む。

(もっと読む)

仮想アドレスキャッシュメモリ及び仮想アドレスキャッシュ方法

【課題】TLBの機能をキャッシュメモリ上で実現して、回路量の削減を図り、かつエイリアスの問題を解消する仮想アドレスキャッシュメモリを提供する。

【解決手段】仮想アドレスキャッシュメモリ12は、プロセスの仮想アドレスの所定の上位ビットの仮想ページタグを含むエントリデータを保持し、プロセッサからの仮想ページタグが一致するとヒット信号を出力するTLB仮想ページメモリ21と、仮想ページタグとページオフセットをキャッシュインデックスとしてキャッシュデータを保持するデータメモリ23と、キャッシュインデックスに対応してデータメモリ23に記憶されたキャッシュデータのキャッシュステートを保持するキャッシュステートメモリ24と、を有する。

(もっと読む)

データ処理装置

【課題】メモリとストレージで重複してデータを保持することによる無駄を省くことができる仮想記管理を実現する。

【解決手段】仮想アドレスと物理アドレスの管理において、メモリ(102)だけではなく、ストレージ(103)のアドレスも変換索引バッファ(107)により変換可能にする。これにより、ストレージからメモリへのデータロードの指示に際して、このアドレス変換索引バッファには、当該仮想ページとストレージのアドレスを登録する事により、メモリとストレージ間のリード・ライトを発生させずに処理を完了することができる。ストレージからメモリにロードするデータやプログラムのコピー動作と、ストレージ上に配置される仮想メモリのページファイルを削除できる。したがって、メモリとストレージの情報格納効率が向上し、メモリの帯域利用効率が上がり、低消費電力にも寄与する。

(もっと読む)

メモリ制御装置

【課題】アドレス変換にかかるオーバヘッドを抑制することができるといった効果を有するメモリ制御装置を提供する。

【解決手段】複数のページに区画されたデータ格納領域10と、ページを示す物理アドレスと論理アドレスとの対応を1つのレコードとするページテーブルを格納するテーブル格納領域11とを有し、物理アドレスでデータ格納領域10にアクセスされるメモリ2と、メモリ2に向けて論理アドレスでアクセスの要求を行うデバイス3と、ページテーブルの複数のレコードを一時記憶するためのキャッシュ12を有し、キャッシュ12に記憶されたレコードが表す対応にしたがって論理アドレスを物理アドレスに変換することにより、デバイス3から要求されたアクセスをメモリ2に要求するメモリ制御部4とを備え、メモリ制御部4は、キャッシュ12でミスヒットが発生したときに、キャッシュ12に記憶された全てのレコードを更新する。

(もっと読む)

ロックインジケータを有するマルチスレッドプロセッサ

ロックインジケータを有するマルチスレッドプロセッサを含むシステムと方法が開示される。実施形態において、システムは、マルチスレッドプロセッサ内の共有リソースのロック状態を示す手段を含む。システムは共有リソースに関連する例外処理命令を処理する前に、共有リソースを自動的にロックする手段を含む。システムは、共有リソースをアンロックする手段をさらに含む。 (もっと読む)

コンフィギュラブル・トランスレーション・ルックアサイド・バッファ

この開示は、トランスレーション・ルックアサイド・バッファ(TLB)をコンフィギュレーションする方法とシステムとを含む。一実施形態においては、前記TLBは、第1の部分と、第2の部分と、を含む。前記第1の部分又は前記第2の部分は、TLBコンフィギュレーション・インジケータの値に応答して選択的にディスエーブルにすることができる。 (もっと読む)

情報処理装置

【課題】キャッシュヒット率に応じて遅延時間を発生することなしにCPUクロックを制御する情報処理装置の制御方法を提供する。

【解決手段】本発明は、キャッシュメモリを有するプロセッサと、プロセッサへクロック信号を供給するクロック供給部とを備える情報処理装置の制御方法であって、前記キャッシュメモリにおけるヒット率を予測するキャッシュヒット率予測部201と、予測したヒット率に応じてCPUクロック周波数を決定する周波数決定部203と、周波数にクロック信号を変更するようクロック供給部を制御するクロック制御部205とを備える。

(もっと読む)

マイクロプロセッサ内の例外を引き起こすページを示す方法およびシステム

ソフトウェア管理されたページテーブル内のどのページが、例えばデジタル信号プロセッサのような、マイクロプロセッサ内の例外を引き起こすか示す方法およびシステムであって、そこでは、ソフトウェア管理された変換索引バッファ(TLB)モジュールは、例えばフェッチ命令のような、超長命令語(VLIM)パケット内の命令により生成された仮想アドレスを受け取り、そして、さらに、その仮想アドレスを格納された各TLBエントリと比較する。

一致するものが存在する場合、TLBモジュールはその命令のために対応するマッピングされた物理アドレスを出力する。

そうでなければ、VLIMパケットが2ページにまたがる場合であって、ここで、1つのページがTLBモジュール内のTLBエントリとして存在し、別のページが格納されたTLBエントリに見当たらないとき、制御レジスタのデータフィールド内の表示ビットは、ソフトウェア管理ユニットにTLBミス例外を識別させるために、セットされる。

前記ソフトウェア管理ユニットは、レジスタから表示ビット情報を検索し、そして、さらに、ミッシングページ情報を検索するために表示ビット情報を使用して、ソフトウェア管理されたページテーブル内のページテーブル探索を実行する。

続いて、ミッシングページ情報は、命令のパケットの後の仮想アドレス変換および実行のために、TLBモジュール内の新しいTLBエントリに書き込まれる。  (もっと読む)

(もっと読む)

データ処理装置

【課題】単一仮想記憶と多重仮想記憶の双方をサポートする。

【解決手段】仮想記憶をサポートするデータ処理装置は、論理アドレス空間を論理ページと呼ばれる単位に分割して、そのページ単位で、論理アドレスを物理アドレスへアドレス変換を行うためのアドレス変換機構を備える。このアドレス変換機構は、複数のプロセスの夫々が論理空間の全域にわたるアドレス変換情報を有するとき、プロセス番号によって論理アドレスを修飾或いは拡張する多重仮想記憶と、複数のプロセスに論理アドレス空間の一部が排他的に割り当てられ、夫々のプロセスがそれに割り当てられた論理アドレス空間のアドレス変換情報を有するとき、プロセス番号によって論理アドレスを修飾或いは拡張しない単一仮想記憶とを有し、多重仮想記憶と単一仮想記憶とを選択することが可能にされる。何れを選択するかはレジスタMMUCRのビットMMUCR.SVの値によって指示される。

(もっと読む)

変換索引マニピェレーション

TLBおよびTLBコントローラを含むコントローラ多段パイプラインを有するプロセッサ。TLBミス信号に応じて、TLBコントローラはメモリあるいは高いレベルのTLBのいずれかからアドレス変換情報を要求するTLB再ロードを開始し、そしてその情報をTLBの中に配置する。プロセッサはミスしている仮想アドレスを有するインストラクションをフラッシュし、そしてインストラクションをリフェッチし、結果的にインストラクションを再挿入する。TLB再ロードの開始およびインストラクションのフラッシュ/リフェッチは、直ちにパイプラインをストールすることなしに、実質的に平行して行われる。リフェッチされたインストラクションはTLB再ロードが完了するまでTLBアクセスポイント上部のパイプラインのポイントに保持され、そしてリフェッチされたインストラクションが次のアクセスに際してTLB内に「ヒット」を発生する。  (もっと読む)

(もっと読む)

1 - 20 / 31

[ Back to top ]