Fターム[5B017CA03]の内容

Fターム[5B017CA03]に分類される特許

1 - 20 / 34

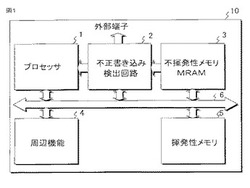

半導体集積回路およびその動作方法

【課題】半導体集積回路の内蔵メモリとしてのMRAMへの不正アクセスに対する保護を改善すること。

【解決手段】半導体集積回路(10)は、プロセッサ(1)と不揮発性メモリ(3)とを具備する。不揮発性メモリ(3)は、複数の磁気ランダムアクセスメモリセルと、複数の磁気リードオンリーメモリセルとを含む。複数の磁気ランダムアクセスメモリセルはプロセッサ(1)による通常書き込みによって書き換えが可能とされ、複数の磁気リードオンリーメモリセルはプロセッサ(1)による通常書き込みによって書き換えが不可能とされる。不揮発性メモリ(3)と接続された感知回路(2)は、不揮発性メモリ(3)の不正アクセスによる複数の磁気リードオンリーメモリセルの状態遷移を感知する。状態遷移に応答して、感知回路(2)は不正アクセスの検出結果をプロセッサ(1)に通知する。

(もっと読む)

プログラム実行装置及び情報保管装置及び情報処理方法及びコンピュータプログラム

【課題】OS状態情報が破壊された場合にもOSが復元されるようにする。

【解決手段】クライアント装置100は、OS状態情報をサーバ装置200に送信し、サーバ装置200にOS状態情報を保管させ、OS機能103の実行が再開される再開タイミングに先立ち、サーバ装置200に送信されたOS状態情報をサーバ装置200から受信し、再開タイミングに、サーバ装置200から受信されたOS状態情報を用いてOS機能103の状態を復元することができるため、OS状態情報が破壊された場合にも確実にOS機能103を復元することができる。

(もっと読む)

マイクロコンピュータ

【課題】第1の処理手段が第2の処理手段によって記憶手段に書き込まれたデータを用いて所定の処理を行うようになっているマイコンにおいて、処理効率を向上させると共に、第1の処理手段が上記データを誤って書き替えてしまうことを防止する。

【解決手段】2つのPE(プロセッサエレメント)1,2を備えるマイコン40では、PE2からPE1へ、記憶手段としてのRAM41を介してデータが供給されるが、そのRAM41は、PE1とPE2との各々から別々にアクセスされる2つのバンクを有した2バンク構成のRAMであり、更に、そのRAM41では、PE1からアクセスされるバンクとPE2からアクセスされるバンクとが、PE1からの選択信号によって切り替わるようになっていると共に、各バンクとも、PE1からはリードアクセスのみ可能で、PE2からはライトアクセス及びリードアクセスが可能になっている。

(もっと読む)

セキュア計算システム、セキュア計算方法およびセキュア計算用プログラム

【課題】マルチコアプロセッサを用いて計算処理を実行する際、プロセッサごとの動作を制御する特別なセキュリティ回路を備えていない場合であっても、セキュアに計算処理を実行できるセキュア計算システムを提供する。

【解決手段】一のコア80は、他のコア90からのアクセスが可能な状態で情報を記憶する他コアアクセス可能記憶手段81と、自コアからのみアクセスが可能な状態で情報を記憶する自コア内アクセス可能記憶手段82とを備える。復号手段83は、他のコアから受信した暗号化データを復号鍵を用いて復号した平文データを作成し、その平文データを平文データ記憶手段87に記憶させる。平文データ計算手段84は、平文データ記憶手段87に記憶された平文データに対して指定された計算処理を行い、その計算処理による計算結果を結果データ記憶手段86に記憶させる。

(もっと読む)

車載ネットワークシステム

【課題】各車載制御装置の処理負荷を抑えつつ車載ネットワークのセキュリティを向上させることのできる手法を提供する。

【解決手段】本発明に係る車載ネットワークシステムにおいて、車載制御装置が保持しているデータに対して読取要求または書込要求を発行する通信装置は、あらかじめ認証装置による認証許可を受ける。

(もっと読む)

通信システムおよびプログラム

【課題】個人情報の漏洩を効果的に防ぐことができる通信システム等を提供すること。

【解決手段】多機能機と複数のPCとが通信可能に接続されている。多機能機は、複数のPCの各々に関する固有情報と、複数のPCに共通する共有情報とをNVRAM40に記憶させる。PCは、PCへインストールされているドライバによって多機能機を制御する。PCは、ドライバのアンインストールが実行されることに応じて、複数のPCのうちからアンインストールが実行されたPCを特定する信号を含んだアンインストール実行信号を多機能機へ送信する。多機能機は、アンインストール実行信号を受信することに応じて、アンインストールが実行されたPCについての固有情報を固有情報テーブルから消去する。多機能機は、固有情報テーブルから全ての固有情報が削除されたことを検出することに応じて、共有情報を共有情報テーブルTから削除する。

(もっと読む)

安全性に関連したおよび安全性に関連していないソフトウェア・コンポーネントを1つのハードウェア・プラットフォーム上で実行する方法

本発明は、安全性に関連したおよび安全性に関連していないソフトウェア・コンポーネント(SAFET、STANT)を1つのハードウェア・プラットフォーム上で実行するための方法に関し、その際ハードウェア・プラットフォームは少なくとも1つの演算処理ユニット(CPU)および少なくとも1つのメモリ(SPE)を含み、その際少なくとも1つの安全性に関連していないソフトウェア・コンポーネント(STANT)が少なくとも1つの安全性に関連したソフトウェア・コンポーネント(SAFET)と共にこの1つの演算処理ユニット(CPU)上で実行され、その際ハードウェア・プラットフォームが監視コンポーネント(監視モジュール)(MOD)を備え、またはこれと接続されており、その際この監視コンポーネント(MOD)がハードウェア・プラットフォームの少なくとも1つの演算処理ユニット(CPU)とは無関係に働く。本発明によると、ハードウェア・プラットフォームはハードウェア・プラットフォームが書込み保護メカニズムを介して少なくとも1つのメモリ(SPE)の少なくとも1つの部分(SPE1、SPE2)を備えており、その際安全性に関連したソフトウェア・コンポーネント(SAFET)が全面的な書込みアクセスを特定の領域(SPE1〜SPE4)または全体のメモリ(SPE)に対して持っており、安全性に関連したソフトウェア・コンポーネント(SAFET)が安全性に関連していない機能のために備えられているメモリ領域から分離されているメモリの特定の領域上で、アクセス権を持ち、その際安全性に関連したソフトウェア・コンポーネント(SAFET)が安全性に関連していないソフトウェア・コンポーネント(STANT)の実行前に、安全性に関連していない機能(STANT)のアクセスに対して、安全性に関連した機能(SAFET)の少なくとも1つのメモリ領域(SPE1、SPE2)のメモリにメモリ保護を行い、その結果、安全性に関連していないソフトウェア・コンポーネント(STANT)は、メモリ(SPE)の制限された領域(SPE3、SPE4、SPE5)内でのみ書込みアクセス権を持ち、特に安全性に関連したコンポーネントのために切り離されたメモリ(SPE)の領域(SPE1、SPE2)へのアクセス権を持たず、その際安全性に関連していないコンポーネント(STANT)からの復帰後に、メモリ保護が再度停止され、その際、監視コンポーネント(MOD)が安全性関連機能をその決められたとおりの手順で監視する。 (もっと読む)

プログラマブルコントローラ、データ書き込み方法、及び受信モジュール

【課題】プログラマブルコントローラのモジュールが付け替えられた場合であっても、書き込みが禁止された領域への書き込みを防止することを目的とする。

【解決手段】制御対象となる装置に接続され、プログラムを実行することによって接続された装置を制御するプログラマブルコントローラにおいて、受け付けた書き込み要求が、制御モジュールへのデータの書き込み要求である場合には、制御アドレスポリシを参照し、書き込み先の制御アドレスへのデータの書き込みが許可されているか否かを判定し、受け付けた書き込み要求が接続モジュールへのデータの書き込み要求である場合には、制御アドレスポリシ及びモジュールアドレスポリシを参照し、書き込み先の制御アドレスへのデータの書き込みが許可されているか否かを判定することを特徴とする。

(もっと読む)

情報処理プログラム、情報処理装置および情報処理方法

【課題】データの完全性を維持しつつ、効率的なアクセス制御を実現することを課題とする。

【解決手段】情報処理装置200内で動作するメモリ管理プログラムは、一方のプログラム(例えば、プログラムA)による共有メモリへのアクセス制限依頼を他方のプログラム(例えば、プログラムB)から受け付けた場合に、アクセス制限依頼が正当なものであるか否かを判定する。判定の結果、アクセス制限依頼が正当なものである場合には、一方のプログラム(例えば、プログラムA)による共有メモリへのアクセス制限をする。このようなことから、情報処理装置200においてデータの完全性を維持しつつ、共有メモリへの効率的なアクセス制御を実現できる。

(もっと読む)

トリプル・バッファリングを使用するデータを処理する方法

【課題】トリプル・バッファリングを使用する双方向データ交換を提供する。

【解決手段】本発明は、データを処理する方法に関する。処理されるデータブロックは、第1の時間間隔(t1、t2、t3、...)においてメモリエリア(A、B、C)に書き込まれる。前記データブロックは、第2の時間間隔(t2、t3、t4...)において同一のメモリエリア(A、B、C)で処理される。処理されたデータブロックは、第3の時間間隔(t3、t4、t5...)において前記同一のメモリエリア(A、B、C)から返される。

(もっと読む)

ハードウェア・ベースの強制アクセス制御

【課題】 ハードウェア・ベースの強制アクセス制御の方法及び機構を提供する。

【解決手段】 ハードウェア・ベースの、データに対する命令のアクセス制御を行うためのハードウェア機構が提供される。これらのハードウェア機構は、プロセッサによって処理される命令に命令アクセス・ポリシー・ラベルを付随させ、プロセッサによって処理されるデータにオペランド・アクセス・ポリシー・ラベルを付随させる。命令アクセス・ポリシー・ラベルは命令と共に、プロセッサの1つ又は複数のハードウェア機能ユニットを介して伝えられる。オペランド・アクセス・ポリシー・ラベルはデータと共に、プロセッサの1つ又は複数のハードウェア機能ユニットを介して伝えられる。プロセッサの1つ又は複数のハードウェア機能ユニットに関連付けられた1つ又は複数のハードウェア実装ポリシー・エンジンが、命令アクセス・ポリシー・ラベル及びオペランド・アクセス・ポリシー・ラベルに基づいてデータへの命令によるアクセスを制御するのに用いられる。

(もっと読む)

複数のCPUコアを備えたFPGAを用いた暗号装置

【課題】最近は複数のCPUコアを内蔵するFPGAも現れており、これらのCPUコアをうまく連携させることで、少ない部品点数を維持したままで、FPGAに内蔵されたCPUコアの処理能力不足に伴う課題を解決する。すなわち、暗号処理を伴うトランザクション処理を効率的に実行する暗号装置を提供する。

【解決手段】FPGA100は、複数のCPUコアを備えている。アプリケーション用CPUコア110は、所定のアプリケーションプログラムから要求された暗号処理を伴う複数のトランザクション処理を並行処理する。暗号処理用CPU120は、アプリケーション用CPUコア110により並行処理される複数のトランザクション処理にともなって処理の実行が必要な暗号処理が発生すると、発生した暗号処理を実行する。

(もっと読む)

セキュア・ビデオ・カード方法およびシステム

【課題】ビデオまたはグラフィック・カード上で使用するように意図されたデ

ータ、および処理されたデータを保護するための方法およびシステムを提供する

こと。

【解決手段】様々な実施形態で、ビデオ・カードが使用するように意図された

データは、そのデータがビデオ・カードとコンピュータ・システムとの間のバス

(たとえばPCIまたはAGPバス)に提供されるときには常に、そのデータが

暗号化されるように、暗号化することが可能である。たとえば、データがビデオ

・カード上のメモリからシステムのメモリに移動される場合(たとえばシステム

物理メモリにマッピングされる場合)およびその逆の場合には、データは暗号化

形式であり、その結果、そのデータは保護される。

(もっと読む)

セキュアなデータ処理とデータ伝送とを行う方法および装置

【課題】ソフトウエア駆動型セキュリティモデルでは、その実行時にしばしば不安定になり、より多くの処理が必要になる。

【解決手段】処理ユニットを複数のモードのうち一つ以上のモードに設定する方法および装置を開示する。その装置は、ローカルメモリ104と、そのローカルメモリ104との間での情報の伝送を可能にするバスと、そのローカルメモリ104に動作可能に接続される一つ以上の演算処理ユニットと、その装置をその複数の動作モードに設定するセキュリティ回路とを備える。その複数の動作モードは、装置および外部装置がバスを介してメモリとの間での情報の転送を開始できる第1のモードと、装置および外部装置がバスを介してメモリとの間での情報の転送を開始できない第2のモードと、装置がバスを介してメモリとの間での情報の転送を開始できるが、外部装置はバスを介してメモリとの間での情報の転送を開始できない第3のモードとを含む。

(もっと読む)

キャッシュ共用処理間の情報漏洩削減

【課題】機密処理のセクションのキャッシュ・アクセス動作情報が信頼されていない処理へ漏洩するのを妨害する方法。

【解決手段】前記機密処理および信頼されていない処理はデータ処理装置内の一つのプロセッサにより遂行され、前記データ処理装置はさらに前記機密処理および信頼されていない処理を遂行中に前記プロセッサにより要求される情報を記憶するように動作可能な少なくとも1つのキャッシュを含み、前記方法は:

前記プロセッサにより前記機密処理の1セクションの処理を開始するのに先立って、前記少なくとも1つのキャッシュ内の前記機密処理の前記セクションにより要求され得る前記機密処理ローディング情報によりさもなければ立ち退かされる、前記少なくとも1つのキャッシュのロケーション内に記憶された情報を立ち退かせるステップを含む前記方法。

(もっと読む)

マルチプロセッサシステム及びマルチプロセッサシステムにおけるアクセス保護方法

【課題】従来のマルチプロセッサシステムでは、共有リソースに対するアクセス権を柔軟に変更することができなかった。

【解決手段】本発明にかかるマルチプロセッサシステムは、第1プロセッサエレメントPE−A、第2のプロセッサエレメントPE−Bを有し、それぞれが独立してプログラムを実行するマルチプロセッサシステムであって、第1のプロセッサエレメントPE−Aは、プログラムに基づき演算処理を行う中央演算装置CPUaと、第1のプロセッサエレメントPE−Aと第2のプロセッサエレメントPE−Bの間で共有される共有リソース18aと、中央演算装置CPUaが指定するアクセス保護範囲設定値に基づき第2のプロセッサエレメントPE−Bから共有リソース18aへのアクセス要求を制限するガードユニット16aと、を有するものである。

(もっと読む)

情報処理方法、情報処理装置、情報処理プログラムおよび該プログラムを記録した記録媒体

【課題】共有メモリの利用の最適化を図り、排他漏れが発生した場合のデバックの効率化を図ること。

【解決手段】MMU302によって、排他制御部306から割り当てられる排他制御の種類に応じた制御関数を用いて各処理単位301のアクセスの許可/禁止を設定する。また、メモリ制御部304によって、排他制御部306によって決定される処理単位301に対する排他制御の種類を用いて、メモリ管理DB305から実行メモリのアドレスを抽出する。アクセスの禁止が設定されている実行メモリに処理単位301がアクセスした場合は、アクセスエラー例外を出力し、アクセスエラー発生箇所を検出する。

(もっと読む)

アドレスオフセット制御回路

【課題】あるプロセッサが記憶したデータを他のプロセッサが破壊してしまう可能性があり、その原因となっているソフトウェア(プログラム)の不具合を特定するのに時間が掛かってしまう。

【解決手段】アドレスオフセット制御回路は、複数のアドレスオフセット加算回路21−1,21−2と、複数の選択回路22−1,22−2とを有している。アドレスオフセット加算回路21−1,21−2は、メモリ10に対するアクセスをそれぞれ行うプロセッサ(例えば、CPU)20−1,20−2からそれぞれ出力されるアドレスに、所定のオフセット値をそれぞれ加算して加算結果をそれぞれ出力する。すると、選択回路22−1,22−2は、各アドレスオフセット加算回路21−1,21−2の加算結果と各CPU20−1,20−2から出力されるアドレスとをそれぞれ選択してメモリ10に与える。

(もっと読む)

共有メモリシステム

【課題】 システムで異常が発生した場合に、共有メモリに格納されている正常なデータを保護する。

【解決手段】 共有メモリシステム1の異常判定部は、複数あるマザーボード10a〜10cのうち、何れかのマザーボードで異常が発生したか否かを判定する。何れかのマザーボードで異常が発生したと判定された場合に、共有メモリシステム1のスイッチ制御部は、スイッチ状態テーブルに格納されているアクセス許可パターンのうち、状態NOが“15”に対応するアクセス許可パターンを選択して保持するとともに、当該アクセス許可パターンに基づいて全てのスイッチをOFFに切り替える。

(もっと読む)

アクセス制御装置及びアクセス制御方法

【課題】 本発明は、コスト増を低減しつつマルチプロセッサシステムにおけるセキュリティを向上することを目的とする。

【解決手段】 複数のバスマスタから前記複数のバスマスタにより共有される少なくとも1の共有バススレーブへのアクセスについてアクセス可否判定を行うアクセス制御装置であって、前記バスマスタから前記共有バススレーブの所定領域へのアクセスを禁止するアクセス可否情報を格納するアクセス可否情報格納部と、前記バスマスタから前記共有バススレーブの所望の領域にアクセス要求が行われた場合、前記アクセス可否情報格納部のアクセス可否情報に基づいて、前記バスマスタが前記アクセス要求先の共有バススレーブの領域にアクセスが可能か否かを判定するアクセス可否判定部とを有するアクセス制御装置を提供する。

(もっと読む)

1 - 20 / 34

[ Back to top ]