Fターム[5B018HA40]の内容

記憶装置の信頼性向上技術 (13,264) | 手段 (2,627) | その他 (39)

Fターム[5B018HA40]に分類される特許

21 - 39 / 39

不揮発性メモリのデータチェック方法

【課題】不揮発性メモリが何等かの原因で破損してデータが変質していたり、不揮発性メモリが交換された後であっても、当該不揮発性メモリを搭載する特定機器の誤動作を防止できる不揮発性メモリのデータチェック方法を提供すること。

【解決手段】不揮発性メモリのデータチェック方法は、不揮発性メモリ20に予め記憶されたパスワードPW2aおよびPW2aを読み出すステップと、パスワードPW2aおよびPW2aに対応する操作入力パスワードPW1aおよびPW1bを入力するステップと、読み出されたパスワードPW2aおよびPW2bと操作入力されたパスワードPW1aおよびPW1bとを比較するステップと、これらの記憶されたパスワードPW2aおよびPW2bと操作入力パスワードPW1aおよびPW1bを比較した結果、一致したときに、不揮発性メモリ20から予め記憶されたデータDを読み出すステップとを具備する。

(もっと読む)

メモリコントローラ及び半導体装置

【課題】半導体記憶装置の動作信頼性を向上出来るメモリコントローラ及び半導体装置を提供すること。

【解決手段】複数のメモリセルMCを備えた半導体記憶装置10を制御するメモリコントローラ20であって、前記メモリセルMCに対して一括して書き込むべき第1データを元に複数の第2データを生成するデータ生成手段21と、各桁が前記メモリセルへの書き込み済みデータのビット毎の累積結果である累積値を保持し、前記第2データのうち、前記累積値の各桁と前記第2データの各々の各ビットとの加算結果の各桁の間でより平均化されるいずれかを選択する選択手段22とを具備し、前記選択手段22で選択された前記第2データとその選択情報とが前記メモリセルMCに書きこまれ、前記選択手段22は選択した前記第2データに関する前記加算結果を新たな前記累積値として保持する。

(もっと読む)

データ転送制御装置、データ転送制御プログラムおよびデータ転送制御方法

【課題】データ転送の処理能力の低下を回避しながら、バッファの容量を最小アクセス単位以下に抑えることを課題とする。

【解決手段】バッファは、記憶媒体との間および制御部との間で転送ビット数(電気的に同一のタイミングで転送されるデータのビット数)の整数倍の容量を有するものであって、バッファと記憶媒体との間で転送ビット数単位でデータ転送を行うことと並行して、制御部とバッファとの間で転送ビット数単位でデータ転送を行い、バッファにおけるデータの出力(入力)の回数をカウントし、回数が1セクタを転送ビット数で除算した数分カウントしたことを示した場合に、1セクタ分のデータが記憶媒体に向けて出力(入力)されたことをカウントし、カウントされたセクタ数と、記憶媒体においてバッファから入力(出力)されたセクタ数とを比較して、データ転送が正常に行われたか否かを判定する。

(もっと読む)

USBメモリ装置及びUSBメモリ装置制御方法

【課題】データ破損防止に有効なUSBメモリ装置及びUSBメモリ装置制御方法を提供する。

【解決手段】USBメモリ装置8は、PC等の外部装置のUSBポートに着脱自在に接続されるUSBコネクタ22と、制御手段としてのCPU31を内蔵した主制御チップ23等を有する。CPU31は、PC等とデータ転送中か否かを監視し、監視の結果に応じて音声発生手段を構成するスピーカ26による音声発生の動作を制御する。

(もっと読む)

記憶装置

【課題】データ化けの発生を防止でき、信頼性を向上できる記憶装置を提供する。

【解決手段】記憶装置は、複数のメモリセルMTを有する半導体メモリ15と、データを一時的に保持するバッファ23と、前記バッファに保持されたデータのうち隣接する複数のメモリセルに格納される所定のデータパターンをチェックし、このチェック結果に応じてアドレスを送信するデータパターンチェック回路27と、送信された前記アドレスのデータの値を補正して前記半導体メモリに送信するデータ補正回路28とを備えるコントローラ22とを具備する。

(もっと読む)

同時ステータスレジスタ読み取り

メモリアレイにおいて保存されていないデータを備えているステータス情報は、Nビットの異なるサブセットM上でステータス情報を駆動し、また、残りのN−Mビットをトライステートするように各メモリデバイスを構成することによって、Nビットデータバスを共有する複数のパラレルメモリデバイスから効率的に読み取られる。各メモリデバイスは、0、1、あるいは複数のサブセットMに関連づけられたストローブを駆動し、また、残りのデータストローブをトライステートするように、さらに構成される。メモリコントローラは、パラレルである2つ以上のメモリデバイスからステータス情報を同時に読み取ることができ、各メモリデバイスは、Nビットバスの個別のサブセットMを駆動する。各メモリデバイスは、ステータス情報をシリアル化し、また、バースト形態においてバスのサブセットM上でそれを駆動することができる。各メモリデバイスは、そのサブセットMを定義するためにメモリコントローラによって初期化された構成レジスタを含むことができる。  (もっと読む)

(もっと読む)

不揮発性メモリ制御装置、不揮発性メモリ制御方法、不揮発性メモリ制御プログラムおよび記録媒体

【課題】例えばフラッシュメモリなどの電気的に書き込みや消去が可能な不揮発性の半導体メモリにおいて、付加回路などハード的な対策を施さずに、誤書き込みを防止する。

【解決手段】光ディスク制御DSP2a上で実行されている制御プログラムが、メモリや他のブロックとのアクセスや内部演算などの動作を行っていないアイドル状態のときは、FlashMemory2dに対してFlashMemory2dを書き込みや消去以外の状態に遷移させるリセットコマンドを発行しつづける。

(もっと読む)

マルチランクメモリサブシステムにおいて共用バス割込みの共同シグナリングを可能にする方法および装置

メモリシステムが開示される。メモリシステムは第1および第2のメモリ装置と、メモリ装置のうちの1つを選択的にイネーブルにするよう構成されたメモリ制御装置を含み、メモリ制御装置は第1および第2のメモリ装置に結合された第1のラインと、第1および第2のメモリ装置に結合された第2のラインとを有する。第1のメモリ装置は第1のラインでメモリ制御装置に通知を供給するよう構成され、第2のメモリ装置は第2のラインでメモリ制御装置に通知を供給するように構成される。メモリ制御装置がイネーブルにされたメモリ装置に書き込みしているときは、第1のメモリ装置は第1のラインをロードしないように更に構成され、第2のメモリ装置は第2のラインをロードしないように更に構成される。  (もっと読む)

(もっと読む)

メモリモジュールの試験装置及び方法

【課題】本発明はメモリモジュールの端子の接触不良の試験装置及び方法に関し,簡単な構成でメモリモジュールの端子部のごみ等による接触不良を確実に検出することを目的とする。

【解決手段】各種のメモリモジュールについて各端子番号とそれぞれの種別が設定されたモジュール別配列表と,モジュール別配列表からモジュール名の入力部から入力されたモジュールについて各端子を種別に応じてグループ化してグループ別配列表に書き込む配列表生成部と,配列表生成部で生成されたモジュール別配列表に従って,グループ別に予め指定された試験方法によりそれぞれの端子について試験を行う試験部とを備える。試験部の試験により発生した出力から,接触不良の端子が検出されたかを判定し,一つの端子について不良であることが検出されると,当該メモリモジュールを接触不良とする判定を判定部により行うよう構成する。

(もっと読む)

ストレージシステム

【課題】本発明のストレージシステムは、フラッシュメモリデバイスのようなメモリデバイスを用いてデータを長期保存する。

【解決手段】ストレージ装置1のフラッシュメモリ搭載部5は、複数のフラッシュメモリデバイス5Aを備える。フラッシュメモリデバイス5Aの記憶領域に論理デバイスが設定される。起動スケジューラ3Aは、内部リフレッシュ処理4A及び外部リフレッシュ処理2Aの起動を制御する。リフレッシュ機能管理テーブル3Bは、フラッシュメモリデバイス5Aに記憶されているデータのリフレッシュ方法及びリフレッシュ時期を各論理デバイス毎にそれぞれ管理する。起動スケジューラ3Aは、リフレッシュ時期の到来した論理デバイスを発見すると、ストレージ装置1または外部装置2のいずれかに起動コマンドを送信し、内部リフレッシュ処理4Aまたは外部リフレッシュ処理2Aを起動させる。

(もっと読む)

記憶装置

【課題】記憶された情報の正否について信頼性に優れる判定機能を備えた記憶装置を提供することを目的とする。

【解決手段】複合機は、ASIC10、SDRAM20、電源回路40、バックアップ電源80、バックアップ電源監視用IC60などから構成される。電源回路40は図示しない電源コードを介して供給された主電源からの交流電圧を整流した後、所定の低い直流電圧に降圧して各装置に供給するためのものである。バックアップ電源80は、主電源を通じての電力供給が断たれたときに、SDRAM20に電源電圧を供給する。本実施形態では、バックアップ電源監視用ICを用いて、バックアップ電源80の電源電圧の変動を監視し、これに基づいて、バックアップ中の記憶情報の正否を判断することとした。電源電圧の変動は、SDRAM20ついて不具合(記憶不良)を生じさせる根本原因となるものであるので、これに基づいて記憶されたデータの正否を判定してやれば、必然的に信頼性の高い判定結果が得られる。

(もっと読む)

処理配列、メモリカード装置、並びに処理配列の動作方法及び製造方法

【課題】記憶ユニットから予期しないデータを処理ユニットが受信しても正常に動作できるようにする。

【解決手段】命令入力12から受けるデータ値に関連付けられ、一定のの動作を始めるように適合された少なくとも1つの予め定められた処理命令を有する予め定められた処理命令のセットを実行する処理ユニット3と、データ値を格納する複数のメモリセル5を有する記憶ユニット2と、上記メモリセル5のデータ値を検出する検出ユニット6と、上記命令入力12に連結され、検出が成功した場合には、上記メモリセル5の検出されたデータ値を供給すると共に、検出が不成功の場合には、予め定められたデータ値を供給するデータ出力7とを備え、上記予め定められたデータ値は、処理ユニット3を介して実行される上記一定の動作を始めるように適合された上記予め定められた処理命令に位置付けられる。

(もっと読む)

ICカード

【課題】 異なるアプリケーション間の境界での書き込みエラー時の波及範囲を小さくし、また、エリアの利用効率を上げることを可能にする。

【解決手段】 EEPROMが書き込み単位を有するICカードにおいて、コマンド受信手段と、ファイルエリア割当の種類の情報が設定されたファイル作成コマンドを受信したとき、前記ファイルエリア割当の種類の情報に基づいてファイルエリア割当の種類を判定する判定手段と、判定手段による判定結果に基づいてファイルエリアを割り当てる割当手段とを備え、前記判定手段が書き込み単位に依存すると判定したとき、既に割当られているファイルエリアの最後のアドレスを示しているポインタを書き込み単位の先頭まで増加させ、前記判定手段が書き込み単位に依存しないと判定したとき、ポインタはそのままとすることを特徴とする。

(もっと読む)

ビットレーン・フェイルオーバーのあるメモリ・チャネル

複数のビットレーンを利用するメモリ装置および方法はビットレーン上の信号の一つまたは複数の経路変更をしうる。メモリ・エージェントは、複数のビットレーンをもつ再駆動回路、メモリ素子またはインターフェース、前記複数のビットレーンと前記メモリ素子またはインターフェースとの間に結合されたフェイルオーバー回路を含みうる。  (もっと読む)

(もっと読む)

メモリコントローラ、不揮発性記憶装置及び不揮発性記憶システム

【課題】強誘電体メモリ等の不揮発性RAMの性能が、温度等の動作環境によって変化しても、安定して動作させるようにする。特に低温時に書き込まれたデータのリテンション特性の劣化を補償する。

【解決手段】温度検知部110が検知した温度などの動作環境値に応じてリフレッシュ部111が不揮発性の補助記憶メモリ109のリフレッシュ処理を行う。具体的にはリフレッシュ部111は、周囲温度が低温から常温に変化した際に、不揮発性の補助記憶メモリ109への再書き込みを行うことにより、不揮発性の補助記憶メモリ109に低温時に書き込まれた情報ビットの電位(低下している電位)を高電位に引き上げる。あるいは、常温に戻ることなく低温のままであっても、周期的にリフレッシュを行うことにより、低下した電位が異常電位(情報識別不能)まで低下することを防止する。

(もっと読む)

フラッシュEEPROMのデータ正否判定方法

【課題】データ検証領域の先頭位置および末尾位置に同一内容の識別情報を格納することにより、識別情報間に挟まれたデータ空間内のデータの正否を判定可能とする。

【解決手段】まず、データ検証領域の先頭位置の先頭識別情報が期待値であるかどうかを判定する(ステップS1)。先頭識別情報が期待値であれば、データ検証領域の末尾位置の末尾識別情報が期待値であるかどうかを判定する(ステップS2)。末尾識別情報も期待値であれば、先頭識別情報と末尾識別情報とが同一内容であるかどうかを判定する(ステップS3)。先頭識別情報と末尾識別情報とが同一内容であれば、先頭識別情報と末尾識別情報とに挟まれたデータ空間内のデータが正しいと判定する(ステップS4)。それ以外の場合には、先頭識別情報と末尾識別情報とに挟まれたデータ空間内のデータが正しくないと判定する(ステップS5)。

(もっと読む)

フラッシュメモリーのデータ管理方法

【課題】フラッシュメモリーの安定性、データの安全性、耐障害性の性能を向上できるフラッシュメモリーのデータ管理方法を提供する。

【解決手段】本発明のフラッシュメモリー内のデータ管理方法は、メモリブロックの操作過程で、ブロックのステータスフラグを末完了状態に設定し、操作完了後は、ステータスフラグを末完了状態から、完了状態に設定する。この方法を利用して、フラッシュメモリーにデータの書き込んでいるときに、突然の電源切れが発生した場合でも、フラッシュメモリー内にあった元のデータの消失を防ぐことが出来る。また、本発明は、上記のデータ管理方法を採用したフラッシュメモリーにデータを書き込む方法とデータリカバーの方法も提供する。  (もっと読む)

(もっと読む)

電子制御装置

【課題】 CPUがフラッシュメモリに記憶されたデータ書き換えを行う際には、不揮発性メモリに記憶されたデータの品質を保証することができる電子制御装置を提供すること。

【解決手段】 メモリ書換装置8との間で演算処理情報の送受信を行う通信回路9と、通信回路9によって受信された演算処理情報を記憶する書換え可能なフラッシュメモリ3と、フラッシュメモリ3を内蔵し演算処理情報に従って演算処理を行うCPU2と、フラッシュメモリ3の周囲温度を検知する温度検知回路7と、CPU2が正常に動作しているか否かを監視する監視回路4と、メモリ書換装置8と通信回路9との間の通信を遮断する遮断回路10とを備え、フラッシュメモリ3の周囲温度が正常範囲にある場合、かつCPU2が正常に動作している場合、通信回路9によって受信された演算処理情報に応じてフラッシュメモリ3に記憶されたデータを書換えるように構成する。

(もっと読む)

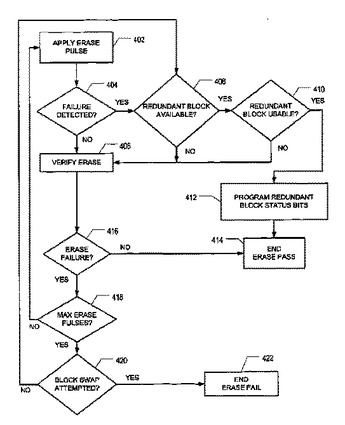

メモリ欠陥検出および自己修復技術

いくつかの実施例によれば、複数の記憶ユニットを有するメモリ・デバイスは、1つまたはそれ以上の予備記憶ユニットを含む。欠陥のある記憶ユニットを示す電気特性を検出すると、予備記憶ユニットの1つが欠陥記憶ユニットを交換するために用いられる。欠陥記憶ユニットの検出は、電流、電圧、および/または抵抗を監視することによって行われる。監視された電気特性が予め定められた閾値を越えたとき、記憶ユニットは欠陥があるとみなされる。欠陥記憶ユニットは、さらなる使用から除去される。予備記憶ユニットは、除去された記憶ユニットのメモリ・アドレスでアクセス可能になるようにプログラムされる。交換は、自動的に(すなわち、ユーザが介入することなしに)生じる。  (もっと読む)

(もっと読む)

21 - 39 / 39

[ Back to top ]