Fターム[5B018MA03]の内容

記憶装置の信頼性向上技術 (13,264) | 対象 (1,668) | バッファ記憶(キャッシュメモリ) (110)

Fターム[5B018MA03]に分類される特許

1 - 20 / 110

半導体記憶装置

不揮発性キャッシュメモリ、不揮発性キャッシュメモリの処理方法、コンピュータシステム

【課題】不揮発性メモリをキャッシュメモリとして使用する場合に、電力遮断状態での保持されているデータの信頼性を向上させる。

【解決手段】キャッシュデータの記憶に不揮発性メモリを用いる。この場合に、電力供給遮断の準備として、待機状態データを生成して不揮発性メモリ部上に記憶する待機準備処理を行う。また電力供給再開の際に、待機状態データを用いて不揮発性メモリ部に記憶されたキャッシュデータの復帰処理を行う。

(もっと読む)

故障位置判定回路、記憶装置、および情報処理装置

【課題】記憶装置で発生したエラーに対して、簡易かつ的確にエラーを解析し、エラーの状況を取得できるようにする。

【解決手段】故障解析回路は、故障がある記憶領域に記憶された故障データと交替レジスタのデータとを比較する比較回路と、比較回路による比較結果データからエラービット位置を特定する位置特定回路と、を備える。

(もっと読む)

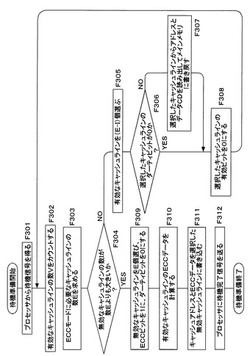

メモリ制御装置及びメモリ制御方法

【課題】メモリアクセスにおいてECCの方式変更を自動的に行う技術を提供する。

【解決手段】バッファメモリと、このバッファメモリを単位データ毎にキャッシュするキャッシュメモリと、この単位データにバイトECCを付加する付加手段とを備えたメモリ制御装置。また、バッファメモリを備えたメモリ制御装置におけるメモリ制御方法であって、このバッファメモリを単位データ毎にキャッシュし、この単位データにバイトECCを付加するメモリ制御方法。

(もっと読む)

記憶装置のデータ保護装置

【課題】キャッシュ領域に転送済みのデータが消失することを防止することが可能な記憶装置のデータ保護装置を提供すること。

【解決手段】制御装置10に備わった、データが格納される不揮発性データ記憶領域14と、不揮発性データ記憶領域14に格納されるデータを一時的に保存するキャッシュ領域15とを有する記憶装置13のデータ保護装置であって、入力電源から供給される電源の電圧を所定の電圧に変換する内部電源装置11と、入力電源から供給される電源の電圧を監視し該電圧の低下を検出した時に電圧低下信号を出力する電源監視回路12と、電圧低下信号を受信したときキャッシュ領域15に保存されたデータを不揮発性データ領域14に書き込む書き込み指令を出力する中央演算処理回路16と、前記書き込み指令が出力されたとき、キャッシュ領域15に保存されたデータを不揮発性データ記憶領域14に書き込むようにした記憶装置のデータ保護装置。

(もっと読む)

退避処理装置、及び、退避処理方法

【課題】複雑な処理を行わず、キャッシュメモリに蓄積中のデータの退避処理を可能とする。

【解決手段】キャッシュメモリの退避を行う第1の不揮発性メモリと、第2の不揮発性メモリと、キャッシュメモリ内のデータにおいて、第1の不揮発性メモリの書込が失敗した領域の情報の履歴を記録した管理テーブルを記憶する記憶部と、第1の不揮発性メモリへの退避処理を行う第1の制御部と、第1の制御部から送られてくる情報を、時間情報と共に、第2の不揮発性メモリへ書きこむ第2の制御部とを有し、第1の制御部は、停電発生時に、キャッシュメモリに記憶されているデータを不揮発性メモリに書き込む処理を実行し、前記退避処理に当たり、該書込が正常に行われたかを検証するとともに、該検証にて正常に書きこまれていない場合、前記不揮発性メモリの正常な書込ができなかった領域の情報を、記憶部に記憶する。

(もっと読む)

キャッシュコントローラ、キャッシュ制御方法及びデータ記憶装置

【課題】ハードエラーの発生に対する効率的な対処を実現し、キャッシュ動作の性能の劣化を抑制できるキャッシュコントローラを提供することにある。

【解決手段】実施形態によれば、キャッシュコントローラは、エラー検出訂正モジュールと、コントローラとを具備する。エラー検出訂正モジュールは、キャッシュメモリから読み出されたデータからエラーを検出し、当該エラーを訂正する。コントローラは、前記エラー検出訂正手段によるエラー訂正が不可能で前記エラーの種別がハードエラーの場合に、前記キャッシュメモリに対する電源遮断及び電源再投入の電源制御を実行する。

(もっと読む)

メモリ装置の診断方法及びメモリ装置の診断装置並びに情報処理装置

【課題】メモリ装置を備えた情報処理装置の、処理上のスループットを低下させることなく、かつ高い信頼性を維持して該メモリ装置の故障診断を行うこと。

【解決手段】

アドレス予測部11は、情報処理装置3を構成するCPU付属のメモリ装置に対し、メモリアクセスの状況(より具体的には、キャッシュラインが保持するキャッシュライン管理情報など)から判断して、近々に書き込みアクセスが発生することになると予測されるメモリのアドレス情報の特定を行う。次に、通達部12は、アドレス予測部11が特定した前記アドレス情報を、メモリ診断部に送出する。これにより、メモリ診断部は、CPU付属のメモリ装置(図示は省略)の、該特定されたアドレス情報が示す記憶領域のみを目下の診断対象とすることができる。

(もっと読む)

記憶装置及びその制御方法

【課題】バックアップ電源の疲弊に応じて機器の動作を変える技術を提供する。

【解決手段】記憶用メモリと、この記憶用メモリへのキャッシュを担うキャッシュメモリ

と、このキャッシュメモリへのキャッシュサイズを制御する制御手段と、電源断時のバッ

クアップを行うバックアップ手段とを備え、このバックアップ手段の疲弊に応じて前記制

御手段は前記キャッシュサイズを変える記憶装置。また、記憶用メモリと、この記憶用メ

モリのキャッシュを担うキャッシュメモリとを備え、電源断時のバックアップを行う記憶

装置の制御方法であって、この記憶装置にバックアップを行うバックアップ電源の疲弊を

予め測定し、この疲弊に応じて前記キャッシュメモリへのキャッシュサイズを調整する制

御方法。

(もっと読む)

ストレージ制御装置及びストレージ制御装置のキャッシュデータ退避方法

【課題】不揮発性メモリにキャッシュデータを退避させるために必要な電力を減少させること。

【解決手段】キャッシュデータの退避指示に基づいて、CPU11はキャッシュメモリ13に保存するキャッシュデータを読み出して圧縮し、当該圧縮キャッシュデータを生成する。また、不揮発性メモリコントローラ14は、CPU11で生成した圧縮キャッシュデータを不揮発性メモリ15に書き込む。

(もっと読む)

メモリ・バックアップのための電力分離

【課題】電力分離およびバックアップ・システムを開示すること。

【解決手段】電源異常状態が検出される時に、一時ストレージをSDRAMにフラッシュする。フラッシュの後に、インターフェースを停止し、電力を、SDRAMサブシステムを除くチップの大半から除去する。SDRAMサブシステムは、データをSDRAMからフラッシュ・メモリにコピーする。その途中で、データを暗号化し、かつ/またはデータ完全性署名を計算することができる。データを復元するために、SDRAMサブシステムは、データをフラッシュ・メモリからSDRAMにコピーする。その途中で、復元されるデータを暗号化解除し、かつ/またはデータ完全性署名をチェックすることができる。

(もっと読む)

メモリシステム

【課題】ブートプログラムの正確な転送動作を実現する。

【解決手段】メモリシステム1は、ブートプログラムを格納する不揮発性の第1のメモリ10と、揮発性の第2のメモリ11と、電源電圧のレベルを検知し、電源電圧が第1のレベルより低くなった場合に割込みを発生する検知回路13と、電源投入時に、第1のメモリ10からブートプログラムを読み出す読み出し動作と、上記読み出されたブートプログラムを第2のメモリ11に転送する転送動作とを含むシーケンスを実行するステートマシン12とを含む。ステートマシン12は、読み出し動作中、又は転送動作中に割込みが活性化された場合に、割込みが非活性化されるまで待機する待機ステートを含む。

(もっと読む)

キャッシュメモリシステム

【課題】よりソフトエラーの影響を抑えることのできるキャッシュメモリシステムを提供する。

【解決手段】キャッシュメモリをライトスルー方式で動作させると共に、キャッシュミス発生時の動作を、キャッシュメモリに対応するデータが無い場合か、データがあってもエラーが発生している場合に行なうようにする。そして、キャッシュメモリに、以前にソフトエラーが発生したことを示すビットを立てておき、このビットが”1”のときに、再び、エラーが発生した場合には、ハードウェアのエラーが発生していると判断して、CPUに割り込みをかけるようにする。このビットは、ソフトエラーが発生すると考えられる頻度よりも十分短い時間間隔でリセットされるようにする

(もっと読む)

データ障害処理装置、及びデータ障害処理方法

【課題】繰り返しの障害発生を回避してプロセッサリリーフを実現するデータ障害処理装置、及びデータ障害処理方法を提供すること

【解決手段】データ障害処理装置は、誤り訂正機能を持つ記憶装置に格納されたデータにアクセスするプロセッサ3を備える。記憶装置は、データ供給時にデータに対して誤り訂正符号を付与する。障害識別部302は、誤り訂正符号に基づいて、前記記憶装置から供給されたデータに障害が発生しているか否かを識別する。事前評価部305は、訂正不可能障害が生じたデータが格納されたアドレスに再度アクセスする事前評価リクエストを発行する。救済可否判定部306は、前記事前評価リクエストの発行結果に応じてプロセッサリリーフが実行可能かを判定する。障害処理部307は、救済可否判定部の判定に応じて障害対応処理を行う。

(もっと読む)

情報処理装置及びキャッシュ制御方法

【課題】 停電等の異常終了が発生した際にも、ダーティデータを外部記憶装置に書き込むことができる情報処理装置及びキャッシュ制御方法を提供すること。

【解決手段】 実施形態によれば、第1外部記憶装置をアクセス可能な情報処理装置は、ホストシステム、第2外部記憶装置、揮発性メモリ、第1キャッシュ制御手段、終了処理手段及び初期化手段を具備する。第2外部記憶装置は前記第1外部記憶装置に対する二次キャッシュとして機能する。揮発性メモリは前記第1外部記憶装置に対する一次キャッシュとして機能し、停電時にバッテリを用いて電力が供給される。第1キャッシュ制御手段は前記第1外部記憶装置に書き込むべきライトデータを前記揮発性メモリ内のキャッシュ領域に格納する。初期化手段は前記情報処理装置が異常終了した後に起動されたとき、前記揮発性メモリ内のキャッシュ領域に格納されたダーティデータを前記第1外部記憶装置に書き込む。

(もっと読む)

計算機および計算機システム

【課題】フラッシュメモリを有する記憶装置をキャッシュデバイスとして用い、仮想マシンが動作する環境において、記憶装置の寿命を減らすことを抑制すること。

【解決手段】実施形態によれば、仮想マシンモニタ上で仮想マシンが稼働する計算機は、第1の記憶装置と、フラッシュメモリを有する第2の記憶装置とを具備する。前記仮想マシンモニタは、前記第1の記憶装置の一部の領域を第3の記憶装置として前記仮想マシンに割り当て、前記第2の記憶装置の一部の領域を第4の記憶装置として前記仮想マシンに割り当る。前記仮想マシンは、前記第4の記憶装置を前記第3の記憶装置のリードキャッシュとして用いる第1のキャッシュ制御手段を有する。

(もっと読む)

擬似エラー発生装置

【課題】半導体メモリに擬似的にエラーを発生させる擬似エラー発生装置を提供する。

【解決手段】乱数によって決定されるメモリのアドレスのデータの情報ビットと冗長ビットの両方を、エラー検出やエラー訂正しないで読み取り、同じく乱数によって決定されるビット位置のビットを反転させ、同じメモリの同じアドレスにビット反転させたデータを書き込む。反転させるビット数は、どのようなエラーを擬似的に発生させたいかによって、1ビット、2ビット以上など、適切に設定する。

(もっと読む)

記憶装置、電子機器、および記憶装置の制御方法

【課題】記憶装置全体のデータにアクセスできなくなることを防止し、かつデータのデータ化けも防止する。

【解決手段】実施形態の記憶装置は、揮発性メモリと、補助電源と、不揮発性メモリと、書込手段と、禁止手段と、を備える。書込手段は、揮発性メモリに対する主電源からの電源が遮断された場合に、前記補助電源からの電源の投入を受けて、揮発性メモリに保持されるユーザデータを表す書込未完了情報を不揮発性メモリに書き込み、書込未完了情報の書込後、揮発性メモリに保持されるユーザデータを不揮発性メモリに書き込み、ユーザデータの書込後、主電源からの電源の遮断を表す電源遮断情報を不揮発性メモリに書き込む。禁止手段は、主電源から揮発性メモリに電源が投入された際に不揮発性メモリに電源遮断情報が書き込まれていなかった場合、書込未完了情報が表すユーザデータの不揮発性メモリからの読み出しを禁止する。

(もっと読む)

ストレージ装置、制御部およびストレージ装置制御方法

【課題】データのバックアップ処理に要する時間を短縮する。

【解決手段】制御部1aでは、制御情報生成部1a1は、記憶部1a3におけるデータの記憶状態を示す制御情報を生成する。転送制御部1a2は、制御部に対する電力の供給が停止した場合に、制御情報生成部1a1で生成された制御情報に基づいて記憶部1a3に記憶されているデータの記憶部1a4への転送を制御する。記憶部1a3は、記憶媒体1bに記憶されるデータを記憶する。記憶部1a4は、制御部1aに対する電力の供給が停止した場合に、記憶部1a3に記憶されているデータを記憶する。記憶媒体1bは、データを記憶する。

(もっと読む)

退避処理装置、退避処理方法および退避処理プログラム

【課題】キャッシュデータのバックアップ処理に要する処理時間を短縮する。

【解決手段】 記憶装置とのアクセス時に取得したデータを記憶するキャッシュメモリと、不揮発性メモリと、キャッシュメモリ内に記憶されているデータにおいて、退避の優先順位を決定するための情報を記憶する管理テーブルと、キャッシュメモリへのデータ記憶に際し、データの種別に応じて、退避の優先順位を決定するための情報を管理テーブルに記憶させる管理手段と、停電発生時に、管理テーブルに記憶されている退避の優先順位を決定するための情報に基づき、キャッシュメモリに記憶されているデータを不揮発性メモリに書き込む処理を実行する停電処理部とを有する。

(もっと読む)

1 - 20 / 110

[ Back to top ]