Fターム[5B022AA02]の内容

Fターム[5B022AA02]に分類される特許

1 - 12 / 12

データをシャッフルするための方法及び装置

【課題】効果的にデータをシャッフルするための方法及び装置を提供すること。

【解決手段】一実施例の方法は、L個のデータ要素を有する第1オペランドとL個の制御要素を有する第2オペランドとを受け取ることからなる。各制御要素に対して、当該制御要素により指定された第1オペランドデータ要素からのデータは、それのゼロクリアフィールドが設定されていない場合に関連付けされた結果のデータ要素位置にシャッフルされ、それのゼロクリアフィールドが設定されていない場合、関連付けされた結果のデータ要素位置にゼロが配置される。

(もっと読む)

ベクトル乗算処理装置および方法ならびにプログラム

【課題】オペランドのシフトを要することなく消費電力の削減をはかる。

【解決手段】高速化回路(固定小数点オーバーフロー先見回路5、スティッキービット先見回路6)を備え、乗算命令に基づき入力される第1オペランドと第2オペランドの積を算出するベクトル乗算処理装置であって、高速化回路を使用し、入力される第1オペランドと第2オペランドとの部分積を生成し、乗算命令とデータ形式とに応じて、部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止する乗算回路4(部分積生成回路41、部分積制御回路42)、を備える。

(もっと読む)

信号処理

【課題】信号を処理する方法を提供すること。

【解決手段】信号データ値および畳み込みフィルタ係数値を、畳み込み値を計算するために使用される一組のプロセッサ(cutil)中の対象プロセッサ(ct)にロードするためのプロセス。係数値はcutilにマッピング(150)される。データ値と係数値のインターリーブ(160)がctについて決定される。係数値がctにロードされ、データ値がctにロードされ、それによって畳み込み値の計算(170)に参加するようctを準備する。

(もっと読む)

ベクトル演算装置及びその方法

【課題】 一つのベクトル命令のみで、最大値や最小値を、要素毎に算出可能とすると共に、長時間ベクトルデータレジスタ内要素の保持を不要としたベクトル演算装置を提供する。

【解決手段】 複数のベクトルデータの要素の各々A,Bを、比較に要する時間だけ保持するベクトルデータ保持回路30を設け、要素A,Bの減算処理による比較回路20の比較結果に基いて、このベクトルデータ保持回路30のうち最も大きい要素または最も小さい要素を選択して演算結果Cとして導出する。これにより、一つの命令で、要素毎に最大値または最小値を求めることが可能となり、この演算が行われ次第、ベクトルデータレジスタ41〜43には要素の保持が必要なくなり、次の要素の書込みが可能となる。

(もっと読む)

リコンフィギュラブルSIMDベクトル処理システム

【課題】リコンフィギュラブルSIMDベクトル処理システムを提供する。

【解決手段】システムであって、冗長形式で表される2Nビットの積をM個出力するM個のNビット×Nビット乗算器と、M個の2Nビットの積を受け取り、M個の2Nビットの積に基づいて冗長形式で表されるMNビットの積を生成するコンプレッサと、M個の2Nビットの積およびMNビットの積を受け取り、M個の2Nビットの積およびMNビットの積のうちいずれかを選択し、選択した積を非冗長形式に変換する加算器ブロックとを備えるシステムを提供する。

(もっと読む)

埋め込み型マスキングを備える高速ローテータ及びその方法

オペランド・ローテータ(100)及びオペランドを回転させる方法が開示される。オペランド・ローテータ(100)は、オペランド・サイズのうちの1つを指示するオペランド・サイズを受け取る第1の入力と、回転量信号を受け取る第2の入力と、複数の制御信号を与える制御出力とを含む。オペランド・ローテータ(100)はまた、第1のデコーダ(102)の制御出力に結合された第1の入力と、データ・エレメントを受け取る第2の入力と、回転されたデータを与える出力とを有するローテータ(104)を含む。ローテータ(104)は、複数の制御信号に応答して、複数のオペランド・サイズのうちの1つに対応するデータ・エレメントの一部を、回転量信号に対応する量だけ回転させる。  (もっと読む)

(もっと読む)

浮動小数点数のベクトル演算方法

【課題】 浮動小数点数のベクトル積演算に必要な処理が軽減され、固定小数点型DSPによる演算処理が適用できるようにした浮動小数点数のベクトル演算方法を提供すること。

【解決手段】 N次の行ベクトルXとN次の列ベクトルYからなるベクトル積XYを求める浮動小数点数のベクトル演算方法において、入力端子1のバッファに格納するベクトルXの成分である各データx1〜xN の仮数部m1〜mN に対して、その指数部については予め各データx1〜xN で共通の指数eにしておき、ベクトルYの成分である各データy1〜yN の仮数部l1〜lN に対しても、その指数部については予め各データy1〜yN でこれも共通の指数e′にしておいてベクトル積XYを演算するようにしたもの。

予めベクトルの指数部を共通化しておくと演算処理量が軽減される。

(もっと読む)

飽和あり、または飽和なしで、オペランドの積和を実行するプロセッサ簡約ユニット

毎回加算後に飽和するか、または毎回加算の結果をラップ・アラウンドするかを選択して、m個の入力オペランドにアキュムレータ値を加えた総和をとる簡約ユニットを備えるプロセッサを提供すること。簡約ユニットは、さらに、入力オペランドのビットを単純に反転し、複数の簡約加算器のそれぞれへのキャリーを1に設定することにより複数のm個の入力オペランドをアキュムレータ値から引くことができる。簡約ユニットをm個の並列乗算器と併用し、ドット積および他のベクトル演算を飽和算術演算またラップアラウンド算術演算とともに高速実行することができる。

(もっと読む)

(もっと読む)

コードを組み合わせる装置及び方法

コンフィギュレーション可能なベクトルプロセッサは、コード生成器を備えることができ、この結果、該コンフィギュレーション可能なベクトルプロセッサは、種々の規格及びコードを取り扱うことができる。更に、これらは、巡回冗長検査(CRC)のような関連付けられている機能をサポートするように配されることができる。この場合、コンフィギュレーション可能なベクトルプロセッサは、ベクトル形式で基本コードを生成する複数の生成器を備え得る。しかしながら、前記のようなコンフィギュレーション可能なベクトルプロセッサの欠点は、前記基本コードに依存する複合コードを供給することができないことにある。このことは、前記コンフィギュレーション可能なベクトルプロセッサが、様々なCDMA様の規格をサポートするのに十分に柔軟でなくてはならない場合、必要である。本発明による装置は、コンフィギュレーション・ワードの制御の下で、加重和演算によって複数の到来する基本コードベクトルからの選択を行うことができる少なくとも2つの加重和ユニットを備えている。このコンフィギュレーション・ワードの成分は、基本コードベクトルを選択する及び選択解除するのに使用される重み係数を表わしている。選択された基本コードベクトルは一緒に加算され、次いで、加重和演算の結果が中間コードベクトルとして出力される。後続して、前記中間コードベクトルは、加算ユニットによって一緒に加算され、複合コードベクトルとして出力される。複数の到来する基本コードベクトルからの選択を行い、中間コードベクトルを加算して複合コードベクトルにするための機能は、コンフィギュレーション・ワードによって前記装置の機能ユニットの演算をコンフィギュレーションするための機能と共に、前記装置の柔軟性を著しく向上させる。この柔軟性は、様々な伝送規格をサポートするのに必要とされる。  (もっと読む)

(もっと読む)

演算処理装置および演算処理プログラム

【課題】ベクトルプロセッサにおいて、回路規模の増大を抑制しつつ、飽和機能を持つ命令を高速に処理する。

【解決手段】 加減算/シフトユニットA25または加減算/シフトユニットB26で加算処理がそれぞれ行われる時に、飽和処理部25a、26aは、ステータスレジスタ22のSビットを参照し、Sビットが“1”の時、加減算/シフトユニットA25または加減算/シフトユニットB26にて得られた加算結果がオーバーフローまたはアンダーフローしているかどうかをそれぞれ判断し、加減算/シフトユニットA25または加減算/シフトユニットB26にて得られた加算結果がオーバーフローしている場合、その加算結果として“0x7FFFFFFF”を出力するとともに、加減算/シフトユニットA25または加減算/シフトユニットB26にて得られた加算結果がアンダーフローしている場合、その加算結果として“0x80000000”を出力する。

(もっと読む)

シャッフル演算のためのマイクロプロセッサデバイス及び方法

本発明は、複数のインデックスベクトルを記憶するための第1のメモリ手段と処理手段とを備える少なくとも一つの機能的なベクトルプロセッサユニットを有するベクトルプロセッサアーキテクチャを備えるマイクロプロセッサデバイスであって、上記機能的なベクトルプロセッサユニットは、処理命令と処理されるべき少なくとも一つの入力ベクトルとを受け取るように構成されており、上記第1のメモリ手段は、上記処理命令に従って上記複数のインデックスベクトルのうちの一つを上記処理手段に対して与えるように構成されており、上記処理手段は、与えられた一つのインデックスベクトルに従って再配置される少なくとも一つの入力ベクトルの要素を有する少なくとも一つの出力ベクトルを上記命令に応じて生成するように構成されている、マイクロプロセッサデバイスに関する。上記機能的なベクトルプロセッサユニットは、処理された上記インデックスベクトルに従って上記少なくとも一つの出力ベクトルを生成する前にパラメータを受け取るとともに上記パラメータに応じて上記一つのインデックスベクトルの要素を処理するように構成されている前処理手段を更に備えている。本発明は、さらに、そのような機能的なベクトルプロセッサユニットによりベクトルを処理する方法に関する。  (もっと読む)

(もっと読む)

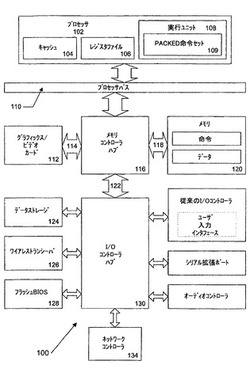

データ処理システムとその方法

【課題】ファジー論理,ニューラル・ネットワークやその他の並行なアレイ準拠アプリケーションに関しては、ベクタ命令およびスケーラ命令の両方に関してデータのコヒーレンシを確認するデータ・コヒーレンシ技術およびメカニズムが必要になり、それにはソフトウェア経費が最小限で済み、最小限の回路構成を用いて実現できることが必要とされる。

【解決手段】

データ処理システムおよびその方法は、1つ以上のデータ・プロセッサを含む。データ・プロセッサは、ベクトル動作とスカラー動作の両方を行うことができる。1台のマイクロシーケンサ22を用いて、データ・プロセッサ10はベクトル命令とスカラー命令の両方を実行することができる。またデータ・プロセッサはベクトル・オペランドとスカラー・オペランドの両方を記憶することのできるメモリ回路を有する。

(もっと読む)

1 - 12 / 12

[ Back to top ]