Fターム[5B033BA03]の内容

Fターム[5B033BA03]に分類される特許

1 - 20 / 59

情報処理装置、情報処理方法、プログラム及び情報記憶媒体

【課題】他種プロセッサで実行可能なコマンドの設定を行うにあたって、他種プロセッサでの処理の実行に影響を与えることなく、処理実行主体装置のプロセッサでの処理の実行を制御するような設定を行えるようにする。

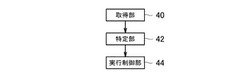

【解決手段】取得部40は、処理実行主体装置のプロセッサとは異なる種類のプロセッサである他種プロセッサで実行可能なコマンドを取得する。特定部42は、取得部40により取得されるコマンドに対応付けられる、処理実行主体装置のプロセッサで実行可能な処理を特定する。実行制御部44は、設定されているパラメータの値が他種プロセッサでの処理の実行に影響を与えない他種プロセッサにおける特定のコマンドに設定されているパラメータの値に応じて処理実行主体装置のプロセッサによる処理の実行を制御する。

(もっと読む)

可変長命令のプリデコーディング

【課題】プロセッサにおける可変長命令をプリデコーディングする方法を提供する。

【解決手段】可変命令長プロセッサにおけるプリデコーダは、命令と共に命令キャッシュに格納されたプリデコードビットで命令の属性を表示する。1の長さ命令と関連付けられたプリデコードビットPD0、PD1の全符号化が定義されるとき、その長さの命令の属性は、異なる長さの命令をエミュレートするために命令を変更し、異なる長さの命令と関連付けられたプリデコードビットの属性を符号化することによって表示される。そのように表示される属性の1つの例は未定義命令である。

(もっと読む)

コンピュータのメモリを参照する方法およびコンピュータ

【課題】新しいアーキテクチャのコンピュータにおいて、新しいバイナリと同じアドレス空間を共有して、古いバイナリをいかなる修正を伴わずに実行する。

【解決手段】第1のコンピュータ命令ストリームをプロファイルし、前記第1のコンピュータ命令ストリームのプロファイルを分析し、前記第1のコンピュータ命令ストリームの周波数実行セクションのみを第2のコンピュータ命令ストリームへ変換し、前記第1のコンピュータ命令ストリームにおけるそれぞれの命令に対応するビットを含むビットベクトルを保存し、前記第1のコンピュータ命令ストリームの実行を監視し、前記第1のコンピュータ命令ストリームから前記第2のコンピュータ命令ストリームへ前記実行を移動し、前記周波数実行セクションの実行が完了した時に、前記第1のコンピュータ命令ストリームの実行に復帰する。

(もっと読む)

仮想マシン環境におけるアプリケーション・プログラム・インタフェースの最適化の方法および装置

【課題】仮想マシン(VM)環境におけるマネージド・ランタイム・アプリケーションの性能を最適化するために、下層のプロセッサの機能を使用可能にする。

【解決手段】1つ以上のプロセッサ命令に関連するプロセッサ命令スタブ(PIPS)が生成される。この「スタブ」は、プログラムの実行時に種々のタスクを実行するために提供される、動的に生成されるコードの一部を指す。そして、生成されたPIPSに基づいて、1つ以上のプロセッサ命令を実行するために最適化アプリケーション・プログラム・インタフェースが生成される。

(もっと読む)

情報処理装置および割込み制御プログラム

【課題】割込み処理の処理時間を短縮することを課題とする。

【解決手段】チェック用CPUは、割込み処理に対応する新PSWに異常があるか否かを判定する。そして、チェック用CPUは、異常があるか否かが判定された新PSWと判定結果とを対応付けて、新PSW記憶領域に格納する。また、命令実行用CPUは、割込み処理が発生した場合に、当該割込み処理に対応する新PSWの判定結果を新PSW記憶領域から取得する。そして、命令実行用CPUは、取得された判定結果が正常である場合に、当該判定結果に対応付けられた新PSWの命令アドレスを用いて、割込み処理を実行する。

(もっと読む)

情報処理装置およびプログラム

【課題】既存のプログラムをVLIW型プロセッサで実行可能であり、処理オーバーヘッドを低減した情報処理装置等を提供すること。

【解決手段】VLIW型プロセッサを備える情報処理装置は、メモリ内に保存されたプログラムをVLIW型命令に変換する命令変換プロセッサを有し、プログラムに応じてレジスタで命令変換プロセッサの制御ソフトウェアを設定することで、制御ソフトウェアを切り替える。

(もっと読む)

効率的な動的バイナリ変換のためのレジスタマッピング技術を用いた方法、物品及びシステム

【課題】動的バイナリ変換の課題はオーバーヘッドであり、効率的なレジスタマッピングを用いて、レジスタのエミュレーションオーバーヘッドを減らすことを目的とする。

【解決手段】本開示書は、より多くのレジスタを備えるシステムからより少ないレジスタを備えるシステムへとレジスタをマッピングするためのシステム及び方法を提供する。リージョンは、一つ以上の相対的に頻度の高いレジスタアクセスを行うコードブロックを含むように構成される。前記最も頻繁にアクセスされるソースレジスタは、ターゲットレジスタへマッピングされる。リージョン内の各ブロックは、プロローグ及び少なくとも一つのエピローグによって境界される。プロローグは、レジスタマッピングを実装するよう構成され、エピローグは、リージョン内のブロックからリージョン内又はリージョン内でない別のブロックへのプログラムフローを管理するよう構成される。

(もっと読む)

エミュレーションにおけるベース・レジスタ相対アドレス指定を有する命令を変換する方法

【課題】元のプロセッサ及び目標プロセッサの異なるサイズのアドレス空間を正しく考慮し、できる限り、少ない命令によりベースレジスタ相対命令を変換する方法を規定し、効果的なエミュレーションを提供する。

【解決手段】元のプロセッサがアドレス指定のためにnビットの長さを有するアドレスを使用し、目標プロセッサはmビットの長さを有するアドレスを使用し、mはnよりも大きい。目標プロセッサ上の投影されたアドレスは、ベースレジスタ相対命令の第1のオフセット(D1)以上であり、差(max−min)未満のオフセット(D)及びベースレジスタ(R)の内容の和を形成し、nビットの長さを有するアドレスで巡回アドレス空間に和を投影する。ベースレジスタ相対命令を変換するためのアドレスは、算出された投影アドレス及び命令のそれぞれの距離値(D1.D2)からオフセットDを引いた値によって求められる。

(もっと読む)

マシン状態に基づいた命令の分割

【課題】 マシン状態に基づいて命令の実行を管理するための方法、情報処理システム、コンピュータ・プログラム製品、及びコンピュータ・プログラムを提供する。

【解決手段】 方法、情報処理システム、及びコンピュータ・プログラム製品が、マシン状態に基づいて命令の実行を管理する。少なくとも1つの命令を受信する。少なくとも1つの命令をデコードする。デコードに応答して、現在のマシン状態を判断する。判断された現在のマシン状態に基づいて、少なくとも1つの命令を1組の操作単位に編成する。操作単位の組を実行する。

(もっと読む)

独立ロード/ストア機構およびそのための命令を実行するための方法、システム、およびコンピュータ・プログラム

【課題】

【解決手段】独立ロード/ストア命令は、CPUによって実行された場合、2つの独立メモリ位置からのオペランドにアクセスし、2つのオペランドが、他のCPUからのオペランドへの介入ストアなしに、ブロック同時インターロック・フェッチを使用してアトミックにアクセスされたように見えるか否かを示すように、条件コード・インジケータを設定する。独立ペア・ロード形式の命令では、アクセスはロードであり、独立データは汎用レジスタに格納される。

(もっと読む)

情報処理装置、情報処理装置の制御方法、及び記録媒体

【課題】ゲストOSを修正することなくパフォーマンスを向上させることが可能な情報処理装置、情報処理装置の制御方法、及びプラグラムを提供する。

【解決手段】本発明に係る情報処理装置は、ゲストOSが動作する仮想マシンと、仮想マシンモニタと、CPUと、を備え、CPUが、ゲストOSが実行することができない所定の命令を検出した場合に、仮想マシンモニタは、所定の命令のエミュレーションコードを生成して、そのエミュレーションコードを仮想マシンへと追加して記憶させるとともに、所定の命令を記憶したエミュレーションコードへのジャンプ命令へと書き換え、ゲストOSは、記憶されたエミュレーションコードを実行することを特徴とする。

(もっと読む)

アライメントまたはブロードキャスト命令を含むマルチメディア・コプロセッサの制御メカニズム

【課題】複数コプロセッサへの命令のビット空間をよりよい方法にする。

【解決手段】プロセッサに基づくシステム22はメイン・プロセッサ24および複数のコプロセッサ26を含む。コプロセッサ26によって実行されるデータ処理動作を指定するメイン・プロセッサ24のコプロセッサ命令は、ターゲット・コプロセッサを識別するためのコプロセッサ識別フィールドを含む。データ要素はソース・レジスタからデスティネーション・レジスタへブロードキャストされる。データ要素のサイズ指定は、2つのビットがバイト(8ビット),ハーフ・ワード(16ビット),ワード(32ビット)およびダブル・ワード(64ビット)を含む4つのデータ・サイズのうちの1つを示し、他の2ビットは飽和タイプを示す。

(もっと読む)

ホストデータ処理装置内におけるデバイスエミュレーションのサポート

メモリ管理装置24を備えたデータ処理装置12が提供される。メモリ管理装置24は、メモリ停止をトリガする。メモリ停止が発生すると、前記メモリ停止を特徴付けるデータがフォールトステータスレジスタ28(メモリ停止レジスタ)に書き込まれる。前記メモリ停止を特徴付けるデータは、前記メモリ停止の発生源となったメモリアクセスと関連付けられたレジスタ番号を特定するデータを含む。このレジスタ特定データを用いて、前記メモリ停止に繋がるプログラム命令を読み出す必要無く、メモリアクセス命令のアクションをエミュレートする。これは、仮想データ処理装置2のための仮想化サポートを提供する際に、有用である。  (もっと読む)

(もっと読む)

処理装置、そのプログラムおよびコンピュータシステム

【課題】メモリの一部を一時的にゲストハードウエアのレジスタによって代行させる際に、ソースコード上での区別を不要にし、設計や検証の効率化を図る。

【解決手段】プロセッサとメモリとゲストハードウエアからなるシステムに組み込む転送機構と、プロセッサの実行する命令列を再構成するリアセンブラとを備える。リアセンブラは、ソースコードおよび該ソースコードからコンパイルされた第1のバイナリコードを取り込んで、転送機構の動作の手がかりとなり且つプロセッサの処理に影響を与えない標識命令を書き込んだ第2のバイナリコードを再構成してメモリにロードする。転送機構は、プロセッサが実行するメモリとの間の読み書き処理のうち、ゲストハードウエアが実行すべき処理で参照/代入される変数の読み書き処理を検出し、当該検出した読み書き処理について、ゲストハードウエアと所定のレジスタとの間で読み書きを実行させる。

(もっと読む)

X86の仮想機をサポートするRISCプロセッサ装置及び方法

X86の仮想機をサポートするRISCプロセッサ装置及び方法は開示される。RISCプロセッサは命令モジュール、デコーダ、固定小数点演算部分と浮動小数点演算部分を含んでいる。命令モジュールはX86の仮想機をサポートする命令セットを保存することに使われる;デコーダは仮想機の命令セットの命令をデコーディングするとき、命令の仮想機命令セットのモードを区別し、命令を区別された仮想機命令セットのモードに基づいて、デコーディングした後固定小数点演算部分または浮動小数点演算部分に出力することに使われる;固定小数点演算部分はデコーダの出力に基づき、仮想機命令セットの固定小数点命令について処理し、実行した結果を出力することに使われる;浮動小数点演算部分はデコーダの出力に基づき、仮想機命令セットの浮動小数点命令について処理し、実行した結果を出力することに使われる。  (もっと読む)

(もっと読む)

プロセッサ、メモリ装置、処理装置及び命令の処理方法

【課題】ゲストの命令をプロセッサで直接実行する場合、命令のトラップと特権モードの切り替えが頻繁に生じ、切り替えに伴うオーバーヘッドの増加によって、プロセッサの性能が低下する。

【解決手段】本発明の処理装置は、ゲストからの命令であるゲスト命令を取得し、トラップの判定処理及びVM環境の退出処理を行うVMトラップロジック122と、ゲスト命令を取得し、バッファリングの判定処理と命令保存処理を行うバッファリングロジック123とを備えるプロセッサ120と、構造体に、バッファリングロジック123が用いる、ゲスト命令のバッファリングを判定する条件であるバッファリング条件を記憶するメモリ130とを備えることとした。

(もっと読む)

RISCプロセッサ装置及び浮動小数点のスタック操作をシミュレートする方法

RISCプロセッサ装置及び浮動小数点のスタック操作をシミュレートする方法が開示される。該プロセッサ装置は、複数の浮動小数点レジスタを含む浮動小数点レジスタヒープと、該RISCプロセッサの操作命令をデコードすることに使われるデコーダと、該デコーダと接続する浮動小数点演算部分と、該浮動小数点レジスタの状態を制御し、デコーダと浮動小数点演算部分が該浮動小数点レジスタヒープを利用して浮動小数点レジスタスタックをシミュレートすることを制御することに使われる制御レジスタとを含む。前記のデコーダはポインタレジスタを含み、該ポインタレジスタは、スタックの操作ポインタを維持し、スタック操作ポインタの値を保存することに使われる。浮動小数点演算部分はポインタ操作モジュールを含み、該ポインタ操作モジュールは該ポインタレジスタを操作し、浮動小数点レジスタスタック操作をシミュレートするとき、ポインタレジスタのスタックポインタのスタック操作をシミュレートし、スタックポインタの状態を変更かつ監視することに使われる。  (もっと読む)

(もっと読む)

データの順列演算を実行するための装置および方法

順列演算を実行するための順列回路を有する処理回路と、データを格納するための複数のレジスタを有するレジスタバンクと、プログラム命令に応答して処理回路を制御し、データ処理演算を実行する制御回路と、を含む処理データのための装置が提供される。制御回路は、制御生成命令に応答して、ビットマスクに基づいて制御信号を生成し、入力オペランドに対して順列演算を実行するための順列回路を構成するように構成される。ビットマスクは、第1の順序を有する第1のグループのデータ要素と第2の順序を有する第2のグループのデータ要素とを前記入力オペランド内で特定し、順列演算は、前記第1の順序と前記第2の順序とのうちの一方を保存するが、前記第1の順序と前記第2の順序とのうちの他方を変える。  (もっと読む)

(もっと読む)

演算処理装置及び命令の拡張方法

【課題】本発明は、固定長のまま命令を拡張する演算処理装置を提供することを課題とする。

【解決手段】命令拡張情報を格納するXARレジスタ1を設ける。実行演算器5は、XARレジスタ1に情報を設定する命令に続く命令を、XARレジスタ1内の命令拡張情報に基づいて命令拡張する。

(もっと読む)

構成の仮想トポロジの変化

【課題】 休止状態のコンピュータ・ハードウェア・リソースのサブセットを有効にするための方法、システム、及びコンピュータ・プログラム製品を提供する。

【解決手段】 ゲスト構成の複数のゲスト・プロセッサ (ゲストCPU)にパーティション化されたホスト・プロセッサ(ホストCPU)を含む論理パーティション化されたホスト・コンピュータ・システムにおいて、perform topology function命令が、ゲスト構成のトポロジ変化を特定するゲスト・プロセッサによって実行される。トポロジ変化は、好ましくはゲストCPUの極性を変化させ、ホストCPUリソースの量に関連する極性がゲストCPUに与えられる。

(もっと読む)

1 - 20 / 59

[ Back to top ]