Fターム[5B033BE05]の内容

Fターム[5B033BE05]に分類される特許

1 - 20 / 51

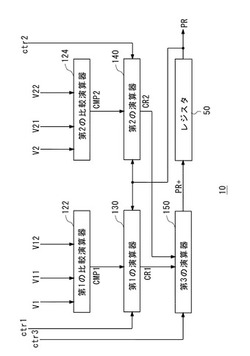

VLIWプロセッサと命令構造と命令実行方法

【課題】VLIWプロセッサにおいて、小さな回路規模で複雑な条件判定処理を効率良く実行する。

【解決手段】第1の演算器130は、第1の制御信号ctr1に応じて、第1の比較演算器122の出力、該出力とレジスタ50が既に保持している値の論理積、論理和のうちの1つを第1の演算結果CR1として出力する。第2の演算器140は、第2の制御信号ctr2に応じて、第2の比較演算器124の出力と、該出力とレジスタ50が既に保持している値の論理積、論理和の3つのうちの1つを第2の演算結果CR2として出力する。第3の演算器150は、第3の制御信号ctr3に応じて、第1の演算結果CR1、第1の演算結果CR1と第2の演算結果CR2の論理積、論理和のうちの1つを実行結果としてレジスタ50に出力する。レジスタ50は、第3の演算器150からの実行結果を新たに保持し、出力する。

(もっと読む)

ハードウェアエンドループ情報の命令へのコード化

【課題】パケットのセットのハードウェアループに関する情報をコード化するための方法と装置を提供する。

【解決手段】パケットの各々は複数命令を含む。ハードウェアループに関する情報はパケットのセットの少なくとも1つの命令の1つ以上のビットにコード化される。前記情報は、パケットがループのエンドパケットあるか否かを示す。2つのハードウェアループに関する情報がコード化される。すなわち第1のループに関する情報は各パケットの第1の予め定められた位置における命令内にコード化され、第2のループに関する情報は各パケットの第2の予め定められた位置における命令内にコード化される。エンド命令情報は、コード化されたループ情報のために予約された同じビット位置にコード化されたループ情報を有しない命令内にコード化される。このエンド命令情報は命令がパケットの最後の命令であるかどうか、およびパケットの長さを示す。

(もっと読む)

命令語圧縮装置、命令語圧縮方法及びコンピュータで読み取り可能な記録媒体

【課題】命令語圧縮装置、命令語圧縮方法及びコンピュータで読み取り可能な記録媒体を提供する。

【解決手段】命令語圧縮装置100は、有効命令語バンドルの間に存在する無演算命令語バンドルの個数に対応した命令語圧縮ビットを生成させる生成部120、生成された命令語圧縮ビットを有効命令語バンドルに挿入する挿入部130、無演算命令語バンドルを削除する削除部140、とを備えることによって、命令語を効率的に圧縮することができる。したがって、プロセッサ内で並列処理されうる命令語の個数が増加する。

(もっと読む)

情報処理装置、情報処理方法

【課題】各プロセッサ間で効率的に演算結果を共有可能な情報処理装置を提供する。

【解決手段】プログラムを記憶するプログラム記憶手段11と、コア毎の演算結果を記憶する演算結果記憶手段45と、コア数分の命令の命令セットを実行順にプログラム記憶手段から読み出し一次記憶部に記憶する命令読み出し手段21と、命令セットに含まれる命令を各コアの命令キューに記憶する命令配信手段32と、一次記憶部に記憶された第一の命令セットに含まれる命令を第一のコアが演算した演算結果を演算対象とする命令が第一の命令セットよりも後に実行される第二の命令セットに含まれ第一のコアと異なる第二のコアが実行するか否かを判定する命令依存関係判定手段33と、命令依存関係判定手段が第二のコアが第二の命令セットに含まれる命令を実行すると判定した場合第一のコアの演算結果記憶手段の値を第二のコアの演算結果記憶手段に複写する複写手段34と、を有する。

(もっと読む)

情報処理装置

【課題】従来の情報処理装置は、同時発行命令数により並列演算数に制限があった。

【解決手段】本発明の情報処理装置は、命令キャッシュと、データキャッシュと、並列動作可能な複数の演算器を備える第1、第2の演算器群22a、22bと、第1の演算器群22aに対する1以上の演算命令を生成する第1の演算制御回路10と、固定命令レジスタ31の命令コードに基づき第2の演算器群22bに対する1以上の演算命令を生成する第2の演算制御回路30と、を有し、第1の演算器群22aは、第1の演算制御回路10が第1の特定命令コードに基づき生成した演算命令に応じて固定命令レジスタ31に命令コードを設定し、第1の演算制御回路10が第2の特定命令コードに基づき生成した演算命令に応じて第2の演算器群22bに処理データを与え、第2の演算器群22bは、第2の演算制御回路30が生成した演算命令に基づく演算を繰り返し実行する。

(もっと読む)

マルチスレッドプロセッサ

【課題】従来のマルチスレッドプロセッサは、処理能力を十分に引き出すことができない問題があった。

【解決手段】本発明のマルチスレッドプロセッサは、第1の命令コードを格納する第1の命令バッファ231と、第2の命令コードを格納する第2の命令バッファ232〜23mと、を備える命令供給部10と、第1、第2の命令バッファから発行される命令コード選択する命令セレクタ11と、命令セレクタ11が選択した命令コードをデコードする命令デコーダ12と、デコード結果に基づく情報処理を行う命令実行部13と、を有する。命令供給部10は、優先的に第1の命令バッファに第1の命令コードを格納し、第1の命令バッファに格納される第1の命令コードの数が命令供給部10が並列して発行可能な命令コード数の最大値の2倍以上となった場合に第2の命令バッファに第2の命令コードを格納するスレッド制御部24を有する。

(もっと読む)

プロセッサ

【課題】逐次実行部(RISCプロセッサ100)の処理と並列実行部(VLIWコプロセッサ200)の処理とを効率良く融合させる。

【解決手段】RISCプロセッサ100において同時にフェッチされた4つの命令のうち第2番目と第4番目の命令の特定フィールドが命令プリデコーダ170によってプリデコードされる。この特定フィールドはオペコードフィールドと同時発行命令数フィールドを含む。オペコードフィールドがVLIWコプロセッサ命令を示す場合、プログラムカウンタ管理部110は同時発行命令数フィールドに応じてプログラムカウンタの増分値を制御する。VLIWコプロセッサ200では同時発行命令数フィールドに応じた並列度によりVLIWコプロセッサ命令が実行される。

(もっと読む)

サブワード実行を用いるVLIWベースのアレイプロセッサで条件付き実行をサポートする方法及び装置

【課題】複合条件に基づくサブワード並列実行をサポートする。

【解決手段】汎用フラグ(ACF)は階層を使用して定義され、エンコードされる。加えられた各ビットは、前の機能性のスーパーセットを提供する。条件の組合せを用いて、複合条件に基づく条件付き分岐の順次シリーズを回避することができ、次いで複合条件を条件付き実行のために使用することができる。フラグの数を変えることによって、条件付きオペレーションの並列性は、例えばVLIW実行での単一の処理からオクタル処理まで、かつ処理要素のアレイにわたって広範に変化することができる。異なるプロセッサ中で生成された条件に基づいて1つのプロセッサ中の条件付き実行を指定することを可能にして、多数のPEは、条件情報を同時に生成することができる。多数のプロセッサアレイ中の各プロセッサは、異なるユニットをそれらのACFに基づいて条件付きで独立に動作させることができる。

(もっと読む)

情報処理装置

【課題】所定の命令実行により参照したデータの条件に応じて、その後の処理の切り替えを効率良く行う。

【解決手段】CPU(130)は、命令セットを構成する命令を実行する。上記命令セットには、メモリ空間上のデータを読み込むロード命令が含まれ、上記ロード命令で読み込まれたデータには、データリード分岐発生ビット領域を有するフォーマットタイプのデータが含まれる。上記CPUには、データリード分岐制御レジスタ(300,310)と、データリード分岐アドレスレジスタ(320,330)と、リードデータ解析部(60)とを含む。上記データリード分岐発生ビット領域に、データリード分岐発生を示すビット値が設定され、上記データリード分岐制御レジスタに、データリード分岐発生ビットが有効であることを示す値が設定されている場合に、上記データリード分岐アドレスレジスタに記憶されたアドレス値に分岐することで処理の切り替えが行われる。

(もっと読む)

命令フェッチ装置、命令パケット生成装置、プロセッサ、および、命令フェッチ方法

【課題】分岐命令に関する情報を利用することにより命令プリフェッチを制御する。

【解決手段】プログラムを固定長の命令ペイロードに分けて命令ヘッダを付与した命令パケットにより管理する。命令パケットには分岐予測フラグを設けて、これが「1」を示している場合にはネクストラインプリフェッチ部150からシステムメモリ140に対するネクストラインの命令プリフェッチを抑止する。分岐予測フラグは、対応する命令ペイロード内に分岐命令が存在し、かつ、その分岐先としてその命令ペイロード内または次の命令ペイロード以外に分岐する可能性が高いことを示すフィールドである。また、連続する命令パケットにおいて分岐予測フラグが「1」になることを回避するために、命令辞書テーブル192を用いた圧縮を行って分岐命令の配置を変更できるようになっている。

(もっと読む)

プロセッサ及びその制御方法

【課題】面積削減と動作周波数削減を図ることができるプロセッサ及びその制御方法を提供する。

【解決手段】プロセッサは、第1命令乃至第4命令と、第5命令乃至第8命令のうち最大で8個の命令を並列実行するプロセッサであり、第1乃至第8命令のいずれかが入力され実行する第1乃至第m演算ユニット142〜148と、第1乃至第m演算ユニット142=148にそれぞれ対応して設けられ、第1乃至第m命令のいずれかの命令を選択して第1乃至第m演算ユニット142〜148に入力する選択器とを有する。第1乃至第4命令は、第1乃至8選択器のそれぞれに入力され、第5乃至第8命令は、それぞれ第5乃至第8以降の選択器に入力される。

(もっと読む)

階層型の超長命令パケットを処理するシステムおよび方法

階層型の超長命令語(VLIW)パケットを処理するシステムおよび方法が開示される。特定の一実施形態では、命令を処理する方法が開示される。この方法は、命令の階層型VLIWパケットを受信するステップと、命令が単一の命令であるか、または、命令が複数のサブ命令を含むサブパケットを含むかを決定するために、パケットから命令を復号するステップとを含む。この方法は、命令がサブパケットを含むことを決定したことに応答して、サブ命令の各々を実行するステップも含む。  (もっと読む)

(もっと読む)

VLIW型プロセッサ用コンパイラ、VLIW型プロセッサ用プログラム開発システムおよび方法

【課題】連続して使用しない演算器を低消費電力モードに設定する電力制御を効率的に行えるVLIW型プロセッサ用プログラムを容易に開発できる開発システムの実現。

【解決手段】複数の演算器36AA,36AB,36AC,36BA,36BB,36BCをそれぞれ有する複数のスロット35A,35Bを備え、演算器の少なくとも一部は低消費電力モードに設定可能であるVLIW型プロセッサ用プログラムの開発システムであって、VLIW型プロセッサ用コンパイラ21と、コンパイラが出力したプログラムを実行する時に使用する演算器の使用情報を生成する演算器使用情報生成部38と、使用情報に基づいて電力制御コンパイルオプションを生成して出力する演算器使用情報出力部72と、を備え、コンパイラ21は、各スロットで使用する演算器の変更を指示する電力制御コンパイルオプションが入力されるインターフェースを備える。

(もっと読む)

効率的プロセッサおよび関連する方法

装置は、プロセッサを含む。プロセッサは、2つのメモリを含む。第1のメモリは、一式の命令を格納する。第2のメモリは、第1のメモリにおける一式の命令より長い別の一式の命令を格納する。第1のメモリおける一式の命令おける命令は、第2のメモリおける一式の命令おける対応する命令に対するポインタとして使用される。一実施形態において、集積回路(IC)は、プロセッサを含み、プロセッサは、第2の一式の命令をアドレス指定する第1の一式の命令を格納する第1のメモリと、第2の一式の命令を格納する第2のメモリとを含み、第2のメモリは、経時的に、命令のスケジューリングを可能にするために、サイクルオフセットを含む。  (もっと読む)

(もっと読む)

情報処理装置

【課題】複数の命令語で構成される超長命令を実行する情報処理装置において、同時実行可能な命令数を低コストで増やすことができるようにすること。

【解決手段】メモリからプログラムをフェッチする命令フェッチ部1と、命令デコーダ部2と、組合せ指示フィールドと命令語グループ内の命令の並びに基づいて演算器の組合せを指示する組合せ制御部3と、命令の指示に基づいて演算器へソースオペランドを供給するレジスタファイル部4と、組合せ制御部3の指示に基づいてレジスタファイル部4からのソースオペランド若しくは命令語グループ内の演算器の演算結果を、命令語グループ内の他の演算器のソースオペランドとして供給する入力セレクタ部5及び入力セレクタ部6と、命令の指示に基づく演算を実施し、該演算結果をレジスタファイル部4と、入力セレクタ部5及び入力セレクタ部6へ供給する演算器A〜Fと、を備えて構成されている。

(もっと読む)

3個のソースオペランドを加算する加算命令

【課題】3個のソースオペランドを加算する新たな命令を設ける。

【解決手段】方法は加算命令の受信が含まれうる。加算命令は、第1のソースオペランド、第2のソースオペランド、および第3のソースオペランドを示すことができる。第1、第2、および第3のソースオペランドの和を、加算命令の結果として格納する。この和は、一部分が、加算命令が示すデスティネーションオペランドに格納され、一部分が、複数のフラグに格納されてよい。他の方法、装置、システム、および機械可読媒体上の命令も含む。

(もっと読む)

複数のデータ・エレメントの収集及び分散

【課題】 本発明は、複数のデータ・エレメントの収集及び分散に関する。

【解決手段】 第1の態様によると、効率的なデータ転送処理は、単一の命令が複数のデータ・エレメントに対する第1の記憶域と第2の記憶域との間の転送処理を指定し、プロセッサ装置によりデコードする段階、前記プロセッサ内の演算実行部による実行のために単一の命令を発行する段階、単一の命令の実行中に例外の発生を検出する段階、及び該例外に応答して、該例外を分配する前に、未解決のトラップ又は割り込みを例外ハンドラに分配する段階、により達成されうる。

(もっと読む)

乗累算演算を実行するための装置および方法

【課題】乗累算演算を実行するデータ処理装置及び方法を提供する。

【解決手段】該データ処理装置は、制御信号に応答して、入力データ要素において、データ処理演算を実行するデータ処理回路を含む。命令デコーダ回路は、入力オペランドとして、第1入力データ要素、第2入力データ要素及び述語値を指定する述語化された乗累算命令に応答して、データ処理回路を制御するように制御信号を生成し、第1入力データ要素および前記第2入力データ要素を乗算し、乗算データ要素を生成し、該述語値が第1の値を有する場合、該乗算データ要素を初期累算データ要素に加算して結果累算データ要素を生成し、該述語値が第2の値を有する場合、該初期累算データ要素から該乗算データ要素を減算して、該結果累算データ要素を生成することで、乗累算演算を実行する。本発明は、パフォーマンス、エネルギー消費及びコード密度を改善する。

(もっと読む)

分散型プロセッサシステムにおけるデータマルチキャスティング

一般に、分散型プロセッサアーキテクチャにおけるデータマルチキャスティングに関する方法、手順、装置、コンピュータプログラム、コンピュータアクセス可能媒体、処理構成、およびシステムが説明される。様々な実装形態は、ソースから第1のメッセージを受信するように構成された複数のターゲット命令を識別することと、ターゲット命令によって一般に共有される選択された情報を含めて、ターゲット命令のそれぞれに関して第1のメッセージにターゲットルーティング命令を提供することと、識別されたターゲット命令のうちの2つがルータに対して互いに異なる方向に配置されているとき、第1のメッセージを複製して、複製されたメッセージを、識別されたターゲット命令のそれぞれに対して異なる方向にルーティングすることを含むことが可能である。ターゲットルーティング命令を提供することは、ターゲット命令によって一般に共有され、左オペランド、右オペランド、またはプレディケートオペランドとして識別されているビットのサブセットを利用する、選択された情報をさらに含むことが可能であり、ターゲット命令の複数の複数命令サブセットのうちの1つの選択を含むことが可能である。 (もっと読む)

固定幅命令エンコード内のプロセッサ操作の拡張された機能性

【課題】システムの固定幅サイズ制限内で送出された単一の命令でもって複数の互換性のある命令を呼び出す。

【解決手段】多重実行システム内で固定幅命令を実行するための装置は、メモリから命令をフェッチする手段(24)と、各々のフェッチ命令を順番にデコードするためのデコーダ(26)とを備え、各々の命令がテンプレートテーブル(28)から局所格納命令をフェッチするための部分を含むか否かが決定される。その部分を含む場合、局所格納命令はフェッチされ、デコードされた局所格納命令部が複数の処理ユニット上で実行される(30)。

(もっと読む)

1 - 20 / 51

[ Back to top ]