Fターム[5B034AA02]の内容

ハードウェアの冗長性 (4,130) | 受動的冗長 (313) | 二重化 (222) | 照合 (145)

Fターム[5B034AA02]の下位に属するFターム

圧縮照合 (4)

Fターム[5B034AA02]に分類される特許

1 - 20 / 141

高完全性処理を提供する方法

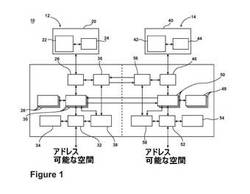

【課題】高集積度マイクロプロセッサにおいて、ロックステップで動作できる機能を提供する。

【解決手段】高完全性処理を提供する方法として、各レーン12、14がアプリケーションプロセッサ20、40を有し、それらのアプリケーションプロセッサが非ロックステップ構成において同じアプリケーションソフトウェアを実行する少なくとも2つの冗長処理レーンを有し、アドレス可能な空間へのアクセスを必要とするトランザクションを出力する高完全性処理システムにおいて、同期および完全性検査を提供する方法。

(もっと読む)

高整合性処理を提供する方法

【課題】マイクロプロセッサにて、ロックステップで走る能力を実現する。

【解決手段】非ロックステップ構成での少なくとも2つの冗長なアプリケーションプロセッサ(12および14)を有する高整合性処理システム10において高整合性通信を提供する。それらの冗長なアプリケーションプロセッサ(12および14)は同じアプリケーションを走らせていて、それらの冗長なアプリケーションプロセッサ(12および14)は、通信チャネル18によって少なくとも1つの入出力プロセッサ16に接続される。

(もっと読む)

電子制御装置

【課題】第1のマイコンの異常を第2のマイコンにより確実に監視することが出来る電子制御装置を提供する。

【解決手段】少なくとも2個のマイクロコンピュータを有し、第1のマイクロコンピュータ(3)が主に制御対象の制御を司り、第2のマイクロコンピュータ(4)が、主に第1のマイクロコンピュータ(3)の異常の監視を行なうように構成された電子制御装置であって、第1マイクロコンピュータ(3)は、自身が制御量の演算に用いるデータの少なくとも一部を、自身の演算リソースを用いずに第2のマイクロコンピュータ(4)に送信するように構成され、第2のマイクロコンピュータ(4)は、送信されたデータに基づいて第1のマイクロコンピュータ(3)の異常の有無を判断するように構成されている。

(もっと読む)

フェイルセーフマイコン

【課題】同一の処理を同期して行う2系統の処理装置を含むフェイルセーフマイコンにおいて、ノイズなどの外乱によって動作が誤って停止されてしまうことを抑制して、制御対象機器の稼動率を高める。

【解決手段】自系の照合データを他系に出力し(S101)、他系の照合データを入力し(S102)、自系の照合データと他系の照合データとを照合する(S103)。次いで、自系の照合結果を他系に出力し(S104)、他系の照合結果を入力し(S105)、これら照合結果の組み合わせの正常・異常を判定する(S106)。正常であれば、自系の照合結果をそのまま出力するが(S107)、異常である場合には、エラーカウンタの値をインクリメントし(S109)、エラーカウンタの値と閾値とを比較する(S110)。そして、エラーカウンタの値が閾値を超えるまでは、S101〜S106の照合動作を再度実行させ、閾値を超えると異常処理を実行する(S111)。

(もっと読む)

情報処理装置

【課題】ロックステップ方式で動作する情報処理装置において、エラー情報の出力による処理負荷を低減し、演算処理の停止や遅延を抑制する。

【解決手段】プロセッサコア1A、1Bがエンジン制御用の演算処理を実行している期間は通知不要フラグ33をオフに設定し、補助的な処理や空のループ処理等を実行している期間は通知不要フラグ33をオンに設定する。比較手段2は、2つのプロセッサコア1A、1Bによる演算処理結果が不一致であった場合に通知不要フラグ33の設定を参照し、通知不要フラグ33がオフに設定されている期間にはエラー情報を出力し、エラー処理手段32がエラー処理を実行するようにし、通知不要フラグ33がオンに設定されている期間には、エラー情報を出力しない。これにより、エラー処理の必要性の低いエラー情報の出力処理が抑制され、プロセッサコア1A、1Bの処理負荷が低減される。

(もっと読む)

二重化情報処理システム

【課題】二重化運転を速やかに開始することができないこと。

【解決手段】動作系情報処理システム1aに待機系情報処理システム1bを同期化させる際、キャッシュコピー手段5が動作系のキャッシュメモリ3aの内容を待機系のキャッシュメモリ3bにコピーすると共に、主記憶コピー手段6が動作系の主記憶装置2aの内容を待機系の主記憶装置2bにコピーする。主記憶アービタ手段7は、主記憶コピー手段6によるコピーが完了するまでの間、動作系のCPU4aおよび待機系のCPU4bからのリードおよびライトを動作系の主記憶装置2aに対するリードおよびライトとして処理する。動作系のCPU4aと待機系のCPU4bは、キャッシュコピー手段5によるコピーの完了時、主記憶コピー手段6によるコピーの完了を待たずに、同一タイミングで同一の処理の実行を開始する。

(もっと読む)

車載電子制御装置

【課題】マイクロコンピュータの異常の詳細を適切に診断することができる車載電子制御装置を提供する。

【解決手段】マイクロコンピュータ(MCU2)の内部に、ハードウェア部21の主機能22の入出力を監視することで故障を検出する監視機能23と、ソフトウェア部24の主機能25の演算結果を監視することで異常を検出する監視機能26とを設ける。監視機能23は、ハードウェア部21の主機能22とは演算処理の特性が等しく且つ異なる実装とし、監視機能26は、ソフトウェア部24の主機能25とは演算処理の特性が等しく且つ異なる実装とする。

(もっと読む)

データ比較回路の故障診断装置

【課題】 2つのデータ列を比較して一致・不一致を判定するデータ比較回路10について、一致側への固定故障を診断可能とする。

【解決手段】 データ比較回路10は、比較するデータ列がそれぞれ所定ビット数ずつ複数のデータに分けられて入力される複数の排他的論理和回路(XOR回路)11−1、11−2、・・・と、これらの出力が入力されて比較結果を出力する論理和回路(OR回路)12とから構成される。ここにおいて、データ比較回路10の入力側で1つのデータ列をそのまま入力させるモードと、ビット反転処理などにより他のデータ列と不一致となるように変化させて入力させるモードとを切替え可能な切替回路13a−1、13a−2、・・・を設ける。そして、前記切替回路により1つのデータ列を変化させて入力させたときのデータ比較回路10の比較結果に基づいて、故障の有無を診断する。

(もっと読む)

2重系演算処理装置の監視装置

【課題】 2重系演算処理装置の信頼性及び実用性を向上する。

【解決手段】 照合タイミング生成回路10A、10Bは、A系CPU及びB系CPUのバス制御信号により照合タイミングを生成する他、1回のアクセスに所定クロック以上を要するアクセス条件では、タイマに基づいて一定時間(カウントアップ時間)の間、照合タイミング信号を生成する。照合回路20は、照合タイミング信号に基づく照合タイミングで、2つのCPUのデータバス上のデータを照合して、一致しているときに交番信号を出力し、不一致のときにその交番信号の出力を停止する。異常検出回路30は、照合回路20からの交番信号を監視し交番信号の出力が停止されたときに異常を検出して、監視リレー40を落下させる。

(もっと読む)

二重化回路、半導体装置およびテスト方法

【課題】比較回路の故障検出が可能な二重化回路、半導体装置およびテスト方法を提供する。

【解決手段】実施形態の二重化回路は、本体回路1と、本体回路1と同じ回路機能を有する監視用回路2と、本体回路1の出力信号OUTと監視用回路2の出力信号MNTを比較し、比較結果が不一致であるときに故障検出信号ERRを出力する比較回路3と、を備える。また、この二重化回路は切り替え回路4を備えている。切り替え回路4は、通常動作モードとテストモードの切り替えを制御するテスト信号がテストモードを示すときは、監視用回路2への入力信号ITを、本体回路1への入力信号INとは異なる信号とする。

(もっと読む)

プロセッサおよびそれを用いた画像処理システム

【課題】演算結果の信頼性と並列度との最適化を図ることが可能なプロセッサを提供すること。

【解決手段】通常モードが設定されている場合に、PE群11〜26のデータレジスタに別個の演算対象のデータが書き込まれ、エラー検出モードが設定されている場合に、PE群11〜18のデータレジスタと、PE群19〜26のデータレジスタとに同じ演算対象のデータが書き込まれる。通常モードが設定されている場合に、マルチプレクサ40〜42が、PE群11〜26から出力される演算結果を別個の演算結果として選択的に出力し、エラー検出モードが設定されている場合に、判定回路43がPE群11〜18と、PE群19〜26とから出力される演算結果を比較し、一致するときにマルチプレクサ40〜42がその演算結果を出力し、一致しないときに判定回路43が外部にエラー検出を通知する。したがって、演算結果の信頼性と並列度との最適化を図ることが可能となる。

(もっと読む)

2重系演算処理装置の監視装置

【課題】2重系演算処理装置の安全性、信頼性を向上する。

【解決手段】第1の照合回路ユニット10(照合回路11)は、同期して動作する2個のCPUのバス上のデータを照合して、一致しているときに交番信号を出力し、不一致のときにその交番信号の出力を停止する。第2の照合回路ユニット20(照合回路21)は、2重系として設けられる。選択器としてのオア回路30は、照合回路ユニット10、20のうち一方から交番信号が入力されているときに、その交番信号を選択して出力する。異常検出回路40は、オア回路30からの交番信号を監視し交番信号の出力が停止されたときに異常を検出する。

(もっと読む)

入力バイパス型のフェイルセーフ装置及びフェイルセーフ用プログラム

【課題】従来の照合型フェイルセーフ装置は、入力データと出力データ共に、比較器を介した経路を通り、比較部で照合を行いながら入出力処理を実行する。データ入力、データ出力ともに性能ネックである比較部の処理時間を影響を受け、汎用高速な演算処理部A,Bの性能を十分に発揮できていない。

【解決手段】この発明によるフェイルセーフ装置は、入力データは比較部を介さず直接論理演算部へ入力し、論理演算部からの出力データのみを比較部で照合を行う。また、入力データで安全性の確保が必要なものについては、入力データのハッシュ値のみを比較部で照合を行い安全性を確保する。本方式によれば、入力データ受信のスループットを向上させ、フェイルセーフ装置全体の性能向上を行うことができる。

(もっと読む)

制御装置および原子力発電プラント制御システム

【課題】高い信頼性を有する制御装置および原子力発電プラント制御システムを提供すること。

【解決手段】本発明に係る原子力発電プラント制御システムは、原子力発電プラントの安全保護系統を制御する原子力発電プラント制御システムであり、原子力発電プラントに生じる特定の事象を検出する検出部10a〜10dと、事象に対処する現場機器50と、それぞれが独立して動作する複数の制御装置である多数決判定装置20aおよび20bと現場機器制御装置40aおよび40bと含む。制御装置のそれぞれは、検出部10a〜10dの検出結果に基づいて演算処理を独立して並列に実行し、演算処理の演算結果に応じて、現場機器50を制御するための信号を出力する複数の演算部備え複数の演算部は、制御装置の起動時に各演算部の演算処理の進行状況を一致させる合わせ込み処理を実行し、合わせ込み処理の完了後は、それぞれに独立して並列に演算処理を実行する。

(もっと読む)

情報処理装置、異常検出方法

【課題】異常のあるCPUコアを特定できない場合でも適切なフェールセーフ処理が可能な情報処理装置を提供すること。

【解決手段】プログラム記憶手段12と、ロックステップモードから非同期モードに切り替えるモード切り替え手段30と、を備えた情報処理装置100であって、ロックステップモードの第1の演算手段と第2の演算手段の演算結果を比較する比較手段32と、演算結果が一致しない場合、モード切り替え手段がロックステップモードから非同期モードに切り替えた後、第1の演算手段と第2の演算手段にそれぞれ自己診断ソフトを実行させるソフト制御手段31と、を有し、2つの演算手段の自己診断の結果がいずれも正常な場合、モード切り替え手段が非同期モードからロックステップモードに切り替えた後、ソフト制御手段が、自己診断ソフトの実行により動作が保証されたフェールセーフソフトを第1の演算手段と第2の演算手段にそれぞれ実行させる。

(もっと読む)

冗長化制御システム、及びその演算データの伝送方法

【課題】受信側で伝送誤り検出と、冗長系毎の演算データの誤りと故障診断とを可能とした冗長化制御システムの演算データの伝送方法を提供することを目的とする。

【解決手段】第1の演算データを生成し、返信時の誤り検出用の第1の生成アルゴリズムを使用して第1の生成データを生成するステップと、第2の演算データを生成し、誤り検出用の第2の生成アルゴリズムを使用して第2の生成データを生成するステップと、相互に第1/第2の演算データとを比較照合するステップと、一致した演算データと、第1/第2の生成データとを含む伝送データを送信するステップと、受信装置では、演算データと予め設定された第1/第2の生成アルゴリズムとから第3/第4の生成データとを生成するステップと、第1/第3の生成データとを、また、第1/第3の生成データとを比較照合して、受信した演算データの誤りを検出するステップとを備えた演算データの伝送方法。

(もっと読む)

2重化演算装置

【課題】システムの安全性を確保しつつ、システムの稼動率を向上させることができる2重化演算装置を提供することを目的とする。

【解決手段】2重化演算装置は、A系演算処理回路2と、B系演算処理回路3と、照合回路4と、リセット回路(リセット手段)6とを含む。そして、A系演算処理回路2とB系演算処理回路3との間でデータの受け渡しを行い、系間でのデータの一致・不一致を判断すると共に、データ照合の結果(CMPa,CMPb)が系間で一致しているか否かを判断する。ここで、データ照合の結果が不一致となった回数が閾値SLに達するまでは、データ照合の結果が異なることを示す信号(CMPa,CMPb)の照合回路への出力を停止した上で、A系演算処理回路2及びB系演算処理回路3をリセットし、前記回数が閾値SLに達すると、データ照合の結果が異なることを示す信号を照合回路へ出力させると共にリセットを停止し、照合回路4の出力をハイレベル又はローレベルに維持させることで、安全リレーを落下させる。

(もっと読む)

2重系演算処理装置および2重系演算処理方法

【課題】メモリ照合コントローラリトライ機能を利用して、一時的な外乱による両系比較不一致が生じた際に、直前の正常な演算データを用いて自動復旧させることを可能にする2重系演算処理装置及び2重系演算処理方法を提供する。

【解決手段】2重系演算処理装置は、2重系を構成するCPU21,22と、各系のCPU21,22の演算データをバス周期に基づいて伝送するバス29a,29bと、各系の演算データを記憶する2重系の記憶装置24,25と、両系の演算データを比較する照合論理部23とを備えている。各系の記憶装置24,25は、演算データを記憶する常用エリアと、両系比較一致を確認した演算データを常用エリアから受信して記憶する退避エリアとを有している。照合論理部23は、両系比較不一致が発生した場合に、各系において、退避エリアから演算データを読み出して、CPU21,22で再演算をさせるリトライ機能を備えている。

(もっと読む)

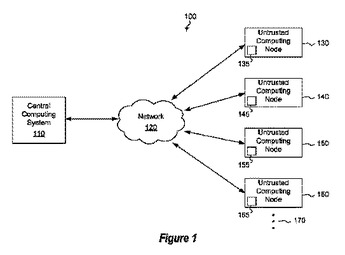

信頼されないコンピューティングノードによって実行された作業の検証

信頼されないコンピューティングノードによって実行された作業を検証する技法を提供する。中央コンピューティングシステムは、第1の信頼されないコンピューティングノードによって少なくとも部分的に実行されるべき第1計算を決定する。中央コンピューティングシステムは、第2の信頼されないコンピューティングノードによって少なくとも部分的に実行されるべき同等の第2計算を作るために第1計算に適用される変換関数をも決定する。中央コンピューティングシステムは、第1の信頼されないコンピューティングノードに第1計算を割り当て、変換関数を秘密に保ちながら、第2の信頼されないコンピューティングノードに第2計算を割り当てる。中央コンピューティングシステムは、第1計算の第1結果および第2計算の第2結果を受け取る。中央コンピューティングシステムは、第1の信頼されないコンピューティングノードおよび第2の信頼されないコンピューティングノードによって実行された作業を検証するために第1結果および第2結果を分析する。  (もっと読む)

(もっと読む)

プロセッサ二重化コントローラ

【課題】2個のプロセッサに異なる機能の処理を実行させることで独立処理の自由度を持たせ、且つ、信頼性を従来と同等とするプロセッサ二重化コントローラを実現する。

【解決手段】入力データを、二重化したプロセッサにより演算し、各プロセッサの演算結果が等値である場合に、その演算結果を出力インターフェースに渡すプロセッサ二重化コントローラにおいて、第1プロセッサと第2プロセッサとが互いに独立したタイミングで、それぞれ入力データを取得して演算し、演算結果を共有メモリに保持し、両方の演算が完了した時点で、第1プロセッサと第2プロセッサとがそれぞれ、両演算結果の照合を行い、いずれの照合においても演算結果が等値である場合に、演算結果の一方を出力インターフェースに渡す。

(もっと読む)

1 - 20 / 141

[ Back to top ]