Fターム[5B042GA11]の内容

デバッグ、監視 (27,428) | 対象プログラム、装置 (3,643) | 対象システム、対象装置 (2,500) | マルチプロセッサシステム、多重系 (365)

Fターム[5B042GA11]に分類される特許

1 - 20 / 365

電子制御装置、および、これを用いた電動パワーステアリング装置

マルチプロセッサ装置及びマルチプロセッサ装置の制御方法

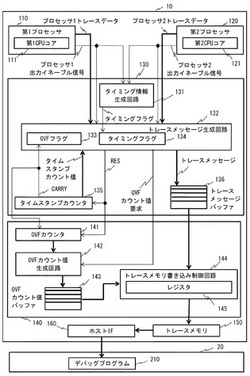

インサーキットエミュレータ、トレースメモリ制御装置、トレースメッセージ生成装置及びトレースメッセージ処理方法

【課題】トレース対象の命令の実行が同時に生じた場合に、正確な命令発生タイミングを把握すること

【解決手段】タイミング情報生成回路131は、第1CPUコア111、第2CPUコア121の各々からのトレースデータの出力と同期して出力されるプロセッサ1(2)出力イネーブル信号に基づき、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報を出力する。トレースメッセージ生成回路132は、各トレースデータと、各トレースデータ取得時のタイムスタンプと、タイミング情報と、を対応付けたトレースメッセージを生成する。トレースメモリ書き込み制御回路144は、トレースメッセージ生成回路132が生成したトレースメッセージをトレースメモリ150に書き込む。

(もっと読む)

通信システム及び方法、ハートビート代行サーバ

【課題】 送受信するデータ量を削減し、ネットワーク負荷低減の手段を提供すること。

【解決手段】 ハートビート代行サーバA10、B20が、データセンターサイト100、200の入口で各物理サーバA、B(仮想マシンVM)が送受信するハートビート信号を監視し、データセンター100、200内の複数物理サーバA、B(仮想マシンVM)のハートビート有無情報を一元管理し、収集した各物理サーバA、B(仮想マシンVM)のハートビート情報をまとめてサイト間で送受信する。

(もっと読む)

高完全性処理を提供する方法

【課題】高集積度マイクロプロセッサにおいて、ロックステップで動作できる機能を提供する。

【解決手段】高完全性処理を提供する方法として、各レーン12、14がアプリケーションプロセッサ20、40を有し、それらのアプリケーションプロセッサが非ロックステップ構成において同じアプリケーションソフトウェアを実行する少なくとも2つの冗長処理レーンを有し、アドレス可能な空間へのアクセスを必要とするトランザクションを出力する高完全性処理システムにおいて、同期および完全性検査を提供する方法。

(もっと読む)

生存監視システム

【課題】稼働中の主サーバが行う処理の遅延を引き起こすことなく、主サーバの生存監視を行うことができる生存監視システムを提供する。

【解決手段】スイッチ10は、各主サーバ100a,100bから信号が送られたときに、その信号をコピーして所定のポートから第一管理サーバ20に送出する。第一管理サーバ20は、スイッチ10からそのコピーされた信号を受信したときに、その送信元である主サーバが生存していると判定し、その判定結果及びその信号を受信した日時を示す日時情報に基づいて作成される当該主サーバの生存状況を示す情報を記憶部に記憶して管理する。第一管理サーバ20は、その管理する主サーバの生存状況を示す情報に基づいて当該主サーバからの信号が前回受信したときから所定時間送られてきていないと判断したときに、当該主サーバが生存していないと判定する。

(もっと読む)

フォールトトレラントシステム

【課題】可用性と信頼性を向上させるために必要なテスト機能を備えるフォールトトレラントシステムを提供する。

【解決手段】保守用計算機102は、指定した演算用計算機103に対し、演算用計算機103に組み込まれている擬似故障処理部302を実行させる命令を、プログラム起動制御部204から送信する。入出力制御部203は、同期検出部205が演算用計算機103の同期が外れたことを確認したことを受けて、演算用計算機103の再組み込み処理部303に再組み込みを指示する。その後、入出力制御部203は、同期検出部205が演算用計算機103の再組み込み処理が失敗したことを確認したら、ログ記録部305を通じてログファイル307からエラーログを収集する。以上の一連の動作は、テスト機能制御テーブル206に記載された内容に従って、各演算用計算機103に対して繰り返し実行される。このため、効率よくエラーログを収集できる。

(もっと読む)

半導体装置

【課題】部分的な経年劣化の予兆を早期に発見することができる半導体装置を提供する。

【解決手段】LSI1は、複数のモジュールと、複数の遅延モニタを含む遅延モニタ群15とを備える。各遅延モニタは、複数段のゲート素子を有するリングオシレータを含む。各遅延モニタは、ゲート素子の遅延時間を測定する。CPU#0は、遅延モニタによって測定された遅延時間に基づいて、遅延モニタの近傍のモジュールの経年劣化を判定する。

(もっと読む)

多重系制御装置

【課題】雷などの影響を受け、2重系の片系が、誤動作により動作停止した場合には、他系に切り替わり、1重系動作状態となるため、早急に復旧させなければ、当該系まで停止した場合システムダウンし、列車の運行を停止させることになる。こうなると、従来にあっては、片系装置の停止原因が、一過性の事象による影響によるものであっても、保安装置(例えば信号機など)の保安者が現場に出向いて異常原因の確認と復旧を行っており、その時間や労力の負担が大きかった。

【解決手段】本発明は、上記課題を解決するために、多重系構成において、制御装置の状態を相互に監視し、停止した系に対し再起動の要求がなされ、停止した系を再起動させる手段を設けたものである。

(もっと読む)

コア監視装置、情報処理装置

【課題】マルチコアマイコンにおいて、異常の生じたコアをソフト的な負荷増大を抑制して判別可能なコア監視装置を提供すること。

【解決手段】複数のコアから共通の周期で通知を受け付けるコア監視装置17であって、 コアから通知を受け付けた際、各コアに固有のコア識別数値(例えば、カウンタ値×ID)をコア毎に生成するコア識別数値生成手段31と、複数のコアのコア識別数値を合計した合計値を算出する合計値算出手段32と、最後に算出された合計値を記憶する合計値記憶手段36と、合計値算出手段が算出した合計値と、合計値記憶手段に記憶された合計値との差である第一の差を算出する第一の差算出手段33と、第一の差を記憶する第一の差記憶手段37と、第一の差算出手段が算出した第一の差と第一の差記憶手段に記憶された第一の差との差である第二の差を算出する第二の差算出手段34と、を有する。

(もっと読む)

複数のデータ・エレメントの収集及び分散

【課題】複数のデータ・エレメントの収集及び分散におけるオーバーヘッドを低減するプロセッサを提供する。

【解決手段】効率的なデータ転送処理は、単一の命令が複数のデータ・エレメントに対する第1の記憶域と第2の記憶域との間の転送処理を指定し、プロセッサ装置140,160によりデコードする段階、前記プロセッサ内の演算実行部による実行のために単一の命令を発行する段階、単一の命令の実行中に例外の発生を検出する段階、及び該例外に応答して、該例外を分配する前に、未解決のトラップ又は割り込みを例外ハンドラに分配する段階、により達成されうる。

(もっと読む)

多重化システム、データ通信カード、状態異常検出方法、及びプログラム

【課題】一般的なIAサーバでソフトウェア(SW)方式のフォールトトレラントシステムやクラスターシステムを構築するために利用されるデータ通信カードに、自系装置のメモリやチップ等の状態監視機能と、他系装置への状態通知機能及び電源制御機能を追加する。

【解決手段】データ通信カードは、複数の物理マシンの各々に搭載され、通信回線を介して自系の物理マシンと他系の物理マシンとを接続し、相互にデータの送受信を行うために用いられる。データ通信カードは、第1のLSIと、第2のLSIとを備える。第1のLSIは、メイン電源の給電により駆動し、自律的に、自他の物理マシンの内部状態を監視し、状態異常を検出する。第2のLSIは、スタンバイ電源の給電により駆動し、自律的に、自他の物理マシンの電源状態を監視し、状態異常を検出し、自系の物理マシンから電源の給電を受けられない場合、他系の物理マシンから電源の給電を受ける。

(もっと読む)

マルチコア・プロセッサ

【課題】信頼性を維持しつつ、各コアが十分な性能を発揮することが可能なマルチコア・プロセッサを提供すること。

【解決手段】プログラムカウンタの示す値に従ってプログラムを実行する第1のプロセッサコアと、第1のプロセッサコアが正常に作動しているか否かを監視する第2のプロセッサコアと、第2のプロセッサコアにより参照可能なデータテーブルと、を備え、第1のプロセッサコアは、所定のチェックタイミングにおいて、少なくともプログラムカウンタの示す値を第2のプロセッサコアに通知し、第2のプロセッサコアは、第1のプロセッサコアから通知されたプログラムカウンタの示す値とデータテーブルに格納された値を比較して、第1のプロセッサコアが正常に作動しているか否かを監視することを特徴とする、マルチコア・プロセッサ。

(もっと読む)

制御装置

【課題】CPUの暴走を検知して正常な状態に復帰させるためにWDT回路は有効であるが、複数のCPUを備えた制御装置では、全てのCPUに各々WDT回路を設けたのではコストが高くなると共に制御装置が大型化するという問題が生じる。

【解決手段】メインCPUが暴走した場合にメインCPUをリセットして正常化するウォッチドッグタイマ装置をメインCPUに対して設けると共に、メインCPUがサブCPUの作動状態を監視し、サブCPUが暴走した場合にはメインCPUがサブCPUをリセットする。

(もっと読む)

半導体集積回路装置

【課題】部品点数を増加させることなく、低コストでかつ効率的に半導体集積回路装置の高信頼性化を実現させる。

【解決手段】ユーザプログラムの実行時において、周期タイマ2からタイマカウンタ信号が出力されると、CPUコア6,7はASEメモリ3に格納されたテスト用プログラムを実行し、そのチェック結果をトレースメモリ11に格納する。デバッグ回路10は、トレースメモリ11に格納されたチェック結果のコンペア処理を行い、CPUコア6,7が正常か否かを判定する。正常の場合、CPUコア6,7は、再びユーザプログラムを実行する。異常の場合、デバッグ回路10は、状態信号をシステム停止回路12に出力する。この状態信号を受けると、システム停止回路12は、動作制御信号をCPUコア6,7にそれぞれ出力し、半導体集積回路装置1の再起動処理が行われる。

(もっと読む)

情報処理装置および障害処理方法

【課題】X86アーキテクチャのCPUを複数備える情報処理装置において、CPUに致命的なエラーが発生して動作不能になった場合に、動作不能になったCPU以外のCPUのエラーログを取得する。

【解決手段】プロセッサがチップセットから所定の割込を受信し、プロセッサ毎に設けられた状態レジスタに所定の値をそれぞれ書き込み、プロセッサが、前記プロセッサ毎に設けられた前記複数の状態レジスタの値が前記所定の値で一致したか否かに応じて、前記複数のプロセッサの何れかに障害が発生したか否かを判定し、複数の状態レジスタの値が一致しないときには、複数のプロセッサの何れかに障害が発生したと判定し、自プロセッサのログを取得して前記BMCに送信する。

(もっと読む)

電子制御ユニット

【課題】消費電流を抑制しつつ、ロックステップ処理を用いて高い安全性を実現でき所望の車両制御を実現できるようにした電子制御ユニットを提供する。

【解決手段】サブマイコン6はロックステップ処理によって第1命令実行部6aおよび第2命令実行部6bの演算結果を互いに比較する。サブマイコン6は、仮想CPUによるロックステップ処理によって第1メインマイコン3の制御状態を監視し、第1メインマイコン3の制御状態が正常でないと判断した場合、第1メインマイコン3をリセットする。したがって、サブマイコン6は、その内部に仮想的に構築された仮想CPU(A)によってロックステップ処理して第1メインマイコン3を監視できる。

(もっと読む)

二重化システムにおける予備装置の障害通知方法

【課題】ホストと予備装置を常時接続することなく、予備装置の障害をホストに通知する二重化システムにおける予備装置の切り替え方法が、望まれる。

【解決手段】

二重化システムにおける予備装置の切り替え方法は、ホストと、ホストと接続されている稼働装置と、稼働装置と接続され、ホストとは接続されていない予備装置と、を含む二重化システムを適用の対象とする。二重化装置の切り替え方法は、予備装置が、自らの障害を検出する第1の工程と、予備装置が、自らの障害を検出した場合には、稼働装置との通信状態を変更する第2の工程と、稼働装置が、予備装置との通信状態に基づいて、予備装置の障害を検出する第3の工程と、予備装置の障害を、稼働装置からホストに通知する第4の工程と、を含んでいる。

(もっと読む)

マルチコアプロセッサのすべてのプロセッサコアの実行トレースダンプが可能なSOCデバイス

【課題】高価な外部ICEなしでターゲット端末のデバッグとトレースダンプが可能になるマルチコアプロセッサ及びデバッグ方法を提供する。

【解決手段】デバッグコントロールユニットを内蔵したターゲットマルチコアプロセッサSOCにおけるEJTAGデバッグ機能、すなわち、プログラム停止・再開、レジスタダンプ、メモリダンプなどと全てのプロセッサのトレースダンプ機能をFIFOで構成し、ターゲットに内蔵のUSBデバイスコントローラのオプションデバイスとして実装する。

(もっと読む)

車載電子制御装置

【課題】マイクロコンピュータの異常の詳細を適切に診断することができる車載電子制御装置を提供する。

【解決手段】マイクロコンピュータ(MCU2)の内部に、ハードウェア部21の主機能22の入出力を監視することで故障を検出する監視機能23と、ソフトウェア部24の主機能25の演算結果を監視することで異常を検出する監視機能26とを設ける。監視機能23は、ハードウェア部21の主機能22とは演算処理の特性が等しく且つ異なる実装とし、監視機能26は、ソフトウェア部24の主機能25とは演算処理の特性が等しく且つ異なる実装とする。

(もっと読む)

1 - 20 / 365

[ Back to top ]