Fターム[5B042GA25]の内容

デバッグ、監視 (27,428) | 対象プログラム、装置 (3,643) | 対象システム、対象装置 (2,500) | OSを用いるもの (574) | 仮想記憶、ページング (15)

Fターム[5B042GA25]に分類される特許

1 - 15 / 15

メモリ管理方法、プログラム及びシステム

【課題】 コンピュータのメモリ上にあるデータに対する、読み取りや書き込みなどの特性を、低いオーバーヘッドで検出する技法を提供すること。

【解決手段】 メモリ分別プロファイラは、対象プロセスのページを間欠的に、すなわち、定期的または一時的にアクセス禁止、または書き込み禁止にする。このとき、メモリ分別プロファイラは、対象アドレスのページフォールト・ハンドラの機能を果たす。ページフォールトを検出すると、そのアドレスとアクセス種別を対象プロセスに通知し、ページを元の状態に戻す。このとき、読み出しアクセスだった場合は、ページをまず、読み出しのみ(書き込み禁止)に変更してもよい。対象プロセスは、通知された情報から、データを、(ある時点以降は)全くアクセスされない(N)、読み出しアクセスのみしか行われない(R)、読み書き両方が行われる(W)に分別する。調査結果に基づき、対象プロセスのメモリ割り当て機構が、RやWのデータをそれぞれ別ページに再配置し、測定を継続する。

(もっと読む)

共有メモリデバッグ装置及びプログラム

【課題】仮想アドレスが指定されるとメモリのアクセスを捕捉するCPUを用いて、人手を介さず、アプリケーションプログラムにも手を加えることなく、共有メモリの特定部分へのデータ書き込みを検出する。

【解決手段】マッピング管理部102は、プロセスごとに共有メモリ内の記憶領域と仮想アドレスとのマッピング関係を管理するデータをメモリ192に記憶する。プロセス検索部105は、マッピング管理部102で記憶されたデータを検索して、記憶領域指定部104で指定された記憶領域を仮想アドレスにマップしているプロセス及び当該仮想アドレスを抽出する。アドレス指定部106は、プロセス検索部105で抽出されたプロセス及び仮想アドレスを、仮想アドレスが指定されるとメモリ192のアクセスを捕捉するCPU191に対して指定する。

(もっと読む)

記憶手段の管理方法、仮想計算機システムおよびプログラム

【課題】仮想環境において、システムがダウンした場合などに、ダンプ情報を出力可能としながら、迅速にシステムの再起動を行うことを課題とする。

【解決手段】本発明は、複数の業務アプリケーションが並行して動作する仮想計算機システムであって、前記複数の業務アプリケーション22a、22bが動作する動作領域と、予備領域と、を備える記憶手段(主記憶装置12)と、所定の業務アプリケーションについて、それまで使用していた前記動作領域のデータを保存したまま、前記予備領域で再起動し、前記使用していた動作領域から前記所定の業務アプリケーションで使用したデータを取得し、前記取得ステップの完了後に、前記使用していた動作領域を新たな予備領域として管理する処理手段(CPU11)と、を備える。

(もっと読む)

メモリ検査システム、メモリ検査方法、メモリ検査用プログラム、記憶媒体、及び集積回路。

【課題】メモリリークや異常データ書き込みなどの、CPUが管理するメモリ領域に発生する異常状態を検知することができるメモリ検査システムを提供する。

【解決手段】メモリ領域を管理するために用いるメモリ管理情報がメモリ領域内のデータの更新を許容する旨を表す属性を含んでいるにも関わらず、メモリ領域に記憶されているデータのハッシュ値の時間変化がない場合、メモリ領域の利用に異常が発生している可能性があると判定する。

(もっと読む)

メモリアクセス調査装置、メモリアクセス調査方法、及びプログラム

【課題】少ない負荷で、高速に、プログラムによるメモリへのアクセス状況を調査する。

【解決手段】仮想記憶方式に対応したオペレーティングシステムと、当該オペレーティングシステムにより所定のブロック単位で分割して管理されるメモリとを有するメモリアクセス調査装置において、実行される対象プログラムから前記メモリにアクセスがあったか否かを示すフラグ情報を、ブロック毎に保持するテーブル情報を格納するメモリ情報格納手段と、前記テーブル情報におけるフラグ情報を、所定のブロック毎に参照することにより、前記メモリへのアクセス状況を表す情報を取得し、当該情報を記憶手段に格納するメモリアクセス調査手段とを備える。

(もっと読む)

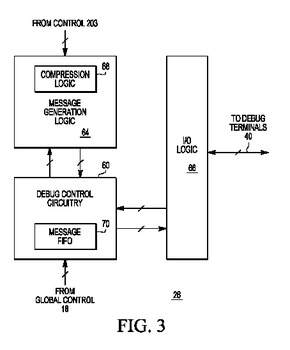

デバッグ用のアドレス変換トレースメッセージ生成

データ処理システム(10)及び方法は、外部デバッグツールをリアルタイムトレース機能を有するように許可することによってデバッグメッセージを生成する。データプロセッサ(20、22、24)は複数のデータ命令を実行し、情報記憶のためにメモリ(30)を使用する。デバッグ回路26はアドレス変換トレースメッセージを含むデバッグメッセージを生成する。仮想形態及び物理形態との間にアドレスを変換するようにアドレス変換を実行するために、メモリ管理ユニット(16)はアドレス変換論理(205)を有する。デバッグ回路(26)は、1つ以上のアドレス変換マッピングは変更される時に通信を受信するためにメモリ管理ユニット(16)に接続されるメッセージ生成回路(64)を含む。メッセージ生成回路(64)は、アドレスマッピングの変更を検出したことに応答してアドレス変換トレースメッセージを生成し、デバッグ回路(26)の外部にアドレス変換トレースメッセージを与える。  (もっと読む)

(もっと読む)

マルチコアチップ用の正式に検証された並列ソフトウェアを構築するためのTICCパラダイム

本発明は、分散および共有メモリマルチコアチップ内で効果的に実行(run)される正式に検証された超並列プログラムを実装する方法を教示する。それはセルと呼ばれる並列ソフトウェアコンポーネント間の相互動作の初期のアブストラクトなステートメントからのプログラムの開発とそれらの最終的な実装への漸進的なリファインとを可能にする。リファインの各段階において、計算におけるイベントのパターンの正式な記述が実装から自動的に導出される。この正式な記述は2つの目的に使用される。1つ目は正しさ、タイミング、プログレス、排他、デッドロック/ライブロックが無いことなどを証明することである。2つ目は性能、保留中のエラー、および重要な振る舞いのパターンを識別し報告するために、自動的に各アプリケーションにそのタイミングに干渉せずにアプリケーションを並列に常に監視する自己監視システム(SMS)を組み込むことである。本発明は、メモリ干渉を最小にし、データを保護し、実行効率を高くする、マルチプロセッサ用に共有メモリを構成する方法も教示する。 (もっと読む)

メモリパトロール障害検出システム、メモリパトロール検出障害報告抑止方法、BMC、及び集積回路

【課題】 OSが切り離したページにおけるメモリパトロールで検出された障害による障害通報/通知を抑止する。

【解決手段】 訂正可能障害が発生したページに対するアクセスが、通常アクセスであるか否かを検出する検出手段と、該ページが、OSにより切り離されたものであるか否かの判定を、検出手段による検出結果にもとづいて行う切り離し判定手段と、障害が発生したことを保守部門における情報処理装置へ通報し、及び/又は、OSへ通知する報知手段とを有し、切り離し判定手段が、該障害が発生したときに、該ページがOSにより既に切り離されたページであるか否かの第一の判定を行い、該障害がメモリパトロールにより検出された障害であるか否かの第二の判定を行い、該ページがOSにより既に切り離されたページであり、かつ、該障害がメモリパトロールにより検出された障害の場合、報知手段が、障害が発生したことの通報及び通知を抑止する。

(もっと読む)

システム解析装置、メモリダンプ取得方法、及びメモリダンプ取得プログラム

【課題】計算機を停止させることなくメモリダンプを取得する。

【解決手段】主記憶装置に記憶領域を管理するためのメモリ管理情報が格納されたシステム解析装置であって、システム解析装置は、メモリダンプが取得されている記憶領域に対して書き込み要求を受け付けた場合には、メモリダンプが取得されている記憶領域と異なる記憶領域を新たに割り当て、新たに割り当てられた記憶領域に対応するメモリ管理情報を追加し、メモリダンプの取得要求を受け付けた場合には、メモリ管理情報に基づいて、メモリダンプが取得される記憶領域に対応する、新たに割り当てられた記憶領域が存在するか否かを判定し、メモリダンプが取得される記憶領域に対応する、新たに割り当てられた記憶領域が存在する場合には、新たに割り当てられた記憶領域に記憶された情報をメモリダンプとして取得する。

(もっと読む)

情報処理装置の障害処理システム

【課題】複数のプロセッサコアが、多数アプリケーションソフトウェア(以下APと称す)を同時並列実行するCPUで、特定プロセッサコアに特定処理を割り当てる場合、障害発生プロセッサコアで、次のAPの迅速動作が出来ない。

【解決手段】複数のプロセッサコアの1つを障害処理プロセッサコアとし、他プロセッサコア上のOSは初期化時に自障害処理手段を障害処理プロセッサコアに登録し、動作中のAPに障害が起きた時、最低限のハードウェア情報保存後、障害発生APを停止、障害処理用プロセッサコアに障害を通知、次動作APをスケジューリング対象とし、障害処理用プロセッサコアは障害情報の収集/記録、障害の対処決定後、障害発生プロセッサコアに障害処理完了を通知、障害発生プロセッサは障害発生AP動作状態を削除し、次APの動作迅速化、複数OS構成での1つの構成による障害処理が可能。

(もっと読む)

クラッシュダンプ用のメモリアロケーション

【課題】クラッシュダンプルーチンを実行するメモリがクラッシュ時にアロケートされるデータ処理装置においてクラッシュダンプを実行できるようにする。

【解決手段】この方法は、第2のルーチンによって使用されるメモリロケーションを特定する第1のルーチンを実行し、特定されたメモリロケーションを含まないメモリ範囲から第2のルーチンを実行するためのメモリをアロケートし、アロケートされたメモリを使用して第2のルーチンを実行することとを含む。第1のルーチンは、より小さなデータサイズを使用することができ、ダンプされるデータの不揮発性ストレージに対する入出力を行わない。再利用に安全なメモリ範囲が特定されると、そのメモリ範囲に記憶されたデータをダンプし、次に、第2のルーチンを実行するためのメモリをそのメモリ範囲からアロケートして、第2のルーチンの実行に再利用する。

(もっと読む)

カバレッジ測定方法及び装置、モジュールのトレース方法及び装置

【課題】仮想記憶方式の主記憶管理をする電子計算機において、ソフトウェアコード(プログラム)のテストの進捗度を測るにあたって、プログラムの動作に全く影響を与えず、また、解析すべきデータ量を低減する。

【解決手段】中央演算装置(CPU101)が仮想記憶方式によって主記憶を参照する際に生じる可能性のある、メモリ管理ユニット(MMU103)のページウォーク処理を、ページ要求記録手段104によって外部へログ出力することにより、プログラムの動作には全く影響を与えずに、おおよそのカバレッジ(テストの進捗度)が測定可能である。また、高速変換バッファ(TLB102)のサイズを限定することにより、ページ単位でのトレース機能が実現する。

(もっと読む)

ヒープダンプ取得方法

【課題】

プログラム実行環境において、メモリリークの検出および原因究明のために取得されるヒープダンプのファイルサイズを削減する。大規模システムにおいても利用可能なメモリリーク調査手段を提供する。

【解決手段】

ヒープダンプを取得する際、ヒープメモリ内のオブジェクトのうち、次の条件に適合するものだけを出力する。(1)指定期間内に新規生成されたオブジェクトで、生存しているもの。(2)ルートセットから(1)のオブジェクトへ至る参照パス上にあるオブジェクト。

(もっと読む)

CPUメモリアクセス解析装置

【課題】システムLSIにおいて、CPUメモリアクセス解析によるソフトウェアの処理速度面での最適化を行うため、システムの振舞いに影響を与えず、低いバンド幅でCPUメモリアクセス状態を出力すること。

【解決手段】システムLSI内に、キャッシュミスヒット信号を検出するキャッシュアクセス検出手段と、プロセス切替を検出するプロセス切替検出手段と、前記プロセス切替信号を受信した場合にはプロセス切替情報を、前記キャッシュミスヒット信号を受信した場合にはキャッシュミスヒット情報をシステムLSI外部に出力するように制御する出力制御手段と、前記出力制御手段に従ってプロセス切替情報、あるいは、キャッシュミスヒット情報を生成しシステムLSI外部に出力する出力選択手段を有し、キャッシュミスヒット時のメモリアクセス状態をプロセスIDに対応付けられた仮想アドレスとして出力することを特徴とする。

(もっと読む)

プログラム実行装置、プログラム実行方法およびサービス提供プログラム

【課題】任意の時点におけるスナップショットを効率よく取得すること。

【解決手段】サーバ100は、ディスクドライバ部130がOSカーネル部120からスナップショット要求を受付けた場合に、OSスナップショットを作成し、作成したOSスナップショットをサーバ200に転送すると共に、記憶部140に記憶されたデータを仮想RAMディスクにスワップアウトし、記憶部140に対するアクセスを凍結する。そして、サーバ200からページ要求を受信した場合には、要求されたページを仮想RAMディスク150から検索し、検索したページをサーバ200に転送する。また、スナップショット保存処理部160は、仮想RAMディスクに記憶されたデータのスナップショット150bと凍結された記憶部140のデータをスナップショット記憶部170に保存する。

(もっと読む)

1 - 15 / 15

[ Back to top ]