Fターム[5B042GA32]の内容

デバッグ、監視 (27,428) | 対象プログラム、装置 (3,643) | コンピュータの構成要素 (774) | バス (76)

Fターム[5B042GA32]に分類される特許

1 - 20 / 76

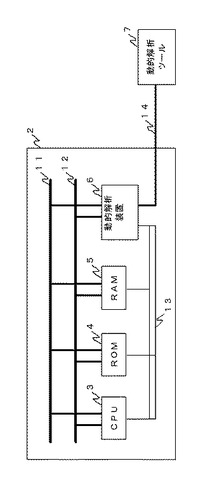

動的解析装置、動的解析システム、動的解析方法、及びプログラム

【課題】簡便に正確に制御装置等の動作を解析可能とする。

【解決手段】動的解析装置6は、解析対象のCPU3が接続される、アドレスバス11、データバス12、制御信号線13に接続される。動的解析装置6は、アドレスバス11上のアドレスの値から処理内容、例えば、実行中の関数や変数を特定し、データバス12上のデータから処理データ、例えば、変数の値を特定するデータ解析部と、データ解析部により解析された処理内容と処理データの履歴を含む履歴情報を記憶する記憶部と、動的解析ツール7からのアクセスに応答して、記憶部に記憶した履歴情報を提供する履歴情報提供手段と、を備える。

(もっと読む)

マルチコアLSI

【課題】動作の安定性を向上できるマルチコアLSIを提供する。

【解決手段】このマルチコアLSI1は、第1の共有バスb1に接続された複数のCPU#0,#1と、第2の共有バスb2に接続された1個以上のモジュールm1〜mnと、第1の共有バスb1と第2の共有バスb2との間に接続され、複数のCPU#0,#1のモジュールへのアクセスを調停する共有バス制御部3と、アクセス先のモジュールから、CPU#0,#1のアクセス要求信号に対する応答信号が出力されたか否かを監視するシステムコントローラ9とを備え、システムコントローラ9は、共有バス制御部3から第2の共有バスb2にアクセス要求信号が出力されてから所定時間経過するまでに、アクセス先のモジュールから応答信号が出力されない場合は、共有バス制御部3を介して第1の共有バスb1に疑似応答信号を出力して、アクセス中のCPUの当該アクセスを終了させる。

(もっと読む)

故障解析支援用の二重系コントローラ

【課題】異常検知時の前後で、CPUがどのようなプログラム処理を実行していたかを記憶し、後でそのときの状態を知ることにより、故障解析の効率向上を図る。

【解決手段】故障解析支援用の二重系コントローラの二重化したバスのそれぞれに、バスの動作履歴を記憶(トレース)する手段を設置して異常検知時の前後一定時間のバス状態を保持し、保持された二重化バスの情報を比較検証することにより、故障解析の効率向上に貢献する。

(もっと読む)

プログラムの動作推測方法及びプログラム

【課題】アプリケーション・レベルの振る舞いを、イベント・ドリブンのシミュレーションで表現するとともに、より粒度の小さいメモリ・アクセス・タイミングを統計的に近似して、ステップ実行時間予測を得る。

【解決手段】参照組込みシステム310において、メモリ・アクセス検出モジュール316は、アプリケーション312の、プラットフォーム314のメモリへのアクセスを検出する。計測モジュール330は、メモリ・アクセス検出モジュール316によって検出され、ステップの開始/終了検出モジュール318によって開始と終了を区切られたデータを、実行トレースの形にして、モデリング/シミュレーション・システム320に転送する。計算モジュール324は、計測モジュール330から渡されたデータを用いて、実行時間やメモリ帯域利用率などの値を推測する。

(もっと読む)

デバッグ装置、デバッグ方法

【課題】デバッグ効率を向上させるデバッグ装置、デバッグ方法を提供する。

【解決手段】デバッグ装置は、命令実行部(32)と、レジスタ(24)と、トレースメモリ(22)と、バス制御部(38)とを具備する。命令実行部(32)は、プログラムコードを実行してアクセスするアドレスをバス(IBUS/PBUS)に出力する。このプログラムコードはデバッグに使用される専用のデバッグコードを含み、命令実行部(32)はデバッグコードを実行していることを示す制御信号(ダミーリード実行信号)を出力する。レジスタ(24)は、ホスト装置(10)によって設定されるアドレスを保持する。トレースメモリ(22)は、バス(PBUS)の状態を示すデータを蓄積する。バス制御部(38)は、制御信号(DSTB)がアクティブのときに、レジスタ(24)に設定されるアドレスを命令実行部(32)が出力するアドレスの代わりに前記バスに出力する。

(もっと読む)

バスシステムおよびバスシステムと接続機器とを接続するブリッジ回路

【課題】バスシステムにおいてスプリットトランザクション実行中の接続機器を、誤動作させることなくバスシステムから切断する。

【解決手段】M台のマスタ100がマスタ切断ブリッジ400を介してインターコネクト300に接続される。S台のスレーブ200がスレーブ切断ブリッジ500を介してインターコネクト300に接続される。マスタ切断信号409により切断が示されると、対応するマスタ100に代わってマスタプロトコル整合部401がスレーブ200とのプロトコル上のやりとりを行う。スレーブ切断信号509により切断が示されると、対応するスレーブ200に代わってスレーブプロトコル整合部501がマスタ100とのプロトコル上のやりとりを行う。マスタ100またはスレーブ200は任意のタイミングで切断および再接続される。

(もっと読む)

情報処理装置

【課題】CPUの命令実行解析情報とメモリアクセスの情報を的確に取得する。

【解決手段】オペランドバス(105,205)に結合された実行部(103,203)と、制御部(101,201)とを含む中央処理装置(CPU#0,#1)と、デバッグ回路(35)とを設ける。上記制御部は、上記中央処理装置での命令実行解析情報を収集するデバッグ機能部を含む。上記デバッグ回路は、上記命令実行解析情報と上記オペランドバスから得られる情報とをそれぞれ専用の論理回路(112,114,212,214)を介して取り込むトレース取得回路(110,210)と、トレース出力回路(111,211)とを含む。上記トレース取得回路には、上記命令実行解析情報と上記オペランドバスから得られる情報とを並べ替える並べ替え論理部(115,215)を設け、的確なトレースを可能にする。

(もっと読む)

情報処理装置

【課題】エラーのアドレス情報の記憶回路のビット数を減らす。

【解決手段】情報処理装置1は、エラーアドレス判別部29によって第1のエラーアドレス空間に属すると判別されたアドレス情報の上位ビットをログとして記憶する上位ビット記憶部31と、エラーアドレス判別部29によって第1のエラーアドレス空間に属すると判別されたアドレス情報が第2のエラーアドレス空間に属するようにそのアドレス情報の上位ビットを変換するアドレス変換部33と、アドレス変換部33で変換されたアドレス情報の上位ビットをデコードし、そのアドレス情報を第2のアドレスバス7へ伝送するデコーダ41と、アドレス情報が第2のエラーアドレス空間に属するかを判別するエラーアドレス判別部87と、エラーアドレス判別部87によって第2のエラーアドレス空間に属すると判別されたアドレス情報をログとして記憶するエラーアドレス記憶部89と、を備える。

(もっと読む)

電子部品及びデバッグ方法

【課題】電子部品のオンチップデバッグを実現するとともに、デバッグ対象となる電子部品の小型化を図る。

【解決手段】電子部品10を構成するCPU11から出力されるアドレスA、データD、及び読書き指示Cの内容が、所定の条件を満たすか否かを判断する第1比較器21a、第2比較器21b、及び第3比較器21cを、電子部品10に設ける。そして、第1比較器21a、第2比較器21b、及び第3比較器21cの判断結果に基づいて、トレース記録信号を生成する。

(もっと読む)

シミュレーション装置

【課題】並列化されていないソフトウェアを用いて、マルチコアプロセッサを有する情報処理システムで並列化したソフトウェアを動作させたときの性能を評価する。

【解決手段】並列化前のソフトウェア109を命令セットシミュレータ102で動作させながら、命令セットシミュレータでのシミュレーションにより要求されたバスアクセスを分割条件に従って分割し、バスシミュレータ103にて、バスの各ポートに対して分割されたバスアクセスについてバスモデルに対するバスアクセスを生成させバスモデルに供給するようにして、ソフトウェアの並列化を行うことなく、マルチコアプロセッサを有する情報処理システムで並列化したソフトウェアを動作させたときのバスアクセスを再現する。

(もっと読む)

トレースデータの優先度の選択

【課題】トレースデータの容量が大きい場合でも、処理すべきデータの優先度に応じ、重要な情報が失われることを回避する。

【解決手段】集積回路2は、バス相互接続16を経由して、トレース出力デバイス8へ接続される、データソース6としてのプロセッサを備える。トレース出力デバイス8にマップされた異なるメモリアドレスは、異なる優先度レベルに関連付けられる。少なくとも1つのメモリアドレスに書き込まれたトレースデータは、これが受け入れられた、またはトレース出力デバイス8によってデータが処理可能になるまで、伝送がストールされた、第1の優先度レベルを有する。異なるメモリアドレスに関連付けられた別の優先度レベルは、トレース出力デバイス8が、処理する能力を有さない場合、例えば、その時点でそのデータを格納する能力を有さない場合に、データが常に受け入れられるが、破棄される。

(もっと読む)

マイクロコントローラ及びマイクロコントローラの試験方法

【課題】デバッグ機能等の複雑な機能を搭載することなく、自動的に短時間で異常原因を検出可能なMPUを提供する。

【解決手段】マイクロコントローラは、処理ユニットによるプログラムの実行開始を起点として、レジスタの格納情報が指定する期間が経過すると、処理ユニットにプログラムの実行を停止させるとともに、バッファにバス上の情報を格納させる制御ユニットと、バッファに格納した情報を外部に送信可能であると共に外部からの情報を受信可能である通信ユニットとを含み、処理ユニットは、通信ユニットにより外部から受信した情報とバッファに格納した情報とを比較し、該比較の結果に応じて、レジスタの格納情報を異なる期間を指定する情報に書き換えてプログラムの先頭からの実行を再度開始する動作、或いは、少なくともレジスタの格納情報を外部に出力する動作、の何れかを選択し実行する。

(もっと読む)

組込系コントローラ

【課題】コストや処理性能の制限が厳しい組込系コントローラへの組込みが容易で、CPU処理性能に影響を与えないように故障解析用のログ収集を可能にしたモニタリング装置を有する組込系コントローラの提供。

【解決手段】CPUを有する組込系コントローラにおいて、PLD(Programmable Logic Device)で構成されたモニタリング装置を設けることにより、CPUに余計な負荷をかけないようにしながらCPUの外部からCPUのメモリへのリードアクセスの際のアドレスのログとNMI発生時の割込要因のログとのうち少なくとも一方、望ましくは両方をモニタリング装置に設けた履歴レジスタに蓄積する。

(もっと読む)

集積回路、システム検証方法、及び携帯端末装置

【課題】 JTAG−ICEやロジックアナライザ等の測定器を用いることなく、ソフトウェアプログラムの介在を極力排除し、LSI内部のモードを極力変化させることなく、ソフトウェアプログラム及びハードウェアにおける問題発生条件の特定、及び問題解析を可能とする。

【解決手段】 バスコントローラから供給される各イニシエータとの間で送受信されたデータ、及び当該データに対応する上記イニシエータ識別番号を、バスイニシエータモニタの内蔵メモリに記憶する。そして、所定のアボート、或いはシステムリセットが発生した際に、上記内蔵メモリをライトプロテクト状態とし、このライトプロテクト状態とされた内蔵メモリに記憶されている上記データ及び上記イニシエータ識別番号を、シリアルデータラインを介して外部に出力して問題発生条件の特定及び問題解析を行う。

(もっと読む)

半導体装置及び異常検出方法

【課題】CPUに負荷を掛けることなく、ソフトウェアが実行する処理タスクの異常を確実に検出することができる半導体装置を提供する。

【解決手段】CPU2が実行するソフトウェアの処理タスクの実行状態を記憶し、処理タスクの実行状態を示す実行状態信号202を出力するタスク状態記憶部10と、CPU2の制御に基づいて出力される処理タスクに対する割り込み信号201と、実行状態信号202とを取得し、処理タスクが正常に実行されている場合、正常動作中信号203を出力するタスク正常判定部21と、正常動作中信号203に基づいて、クリア信号204を出力するクリア出力部22と、所定の時間以内にクリア信号204を取得した場合、タイマカウント値をクリアし、所定の時間が経過してもクリア信号204を取得できない場合、リセット信号205をCPU2へ出力するウォッチドッグタイマ30とを具備する。

(もっと読む)

デバッグシステム

【課題】ボード実装レベルにおいても、容易に内部信号を外部で観測してデバッグを行なうことのできるデバッグシステムを提供する。

【解決手段】半導体情報処理装置においてデバッグサポートユニット(2a)からのCPU動作トレース情報とバスマスタ(7)のメモリアクセス時に出力される内部バス(3)上の内部アクセス情報をデバッグ指示信号に従って選択して外部へ伝達するマルチプレクサ(8,8A)を設けるとともに装置外部にこれらのアクセス情報を格納するメモリ領域を設ける。

(もっと読む)

集積回路、デバッグ回路、デバッグコマンド制御方法

【課題】、内蔵するデバッグ回路からメモリ等の内部リソースに直接にアクセスできる構成において、バスを効率的に使用可能なようにバス権獲得要求及び承認を制御する集積回路を提供する。

【解決手段】集積回路は、バスと、ユーザプログラムを実行する処理ユニットと、処理ユニットからの命令転送要求に応答して処理ユニットにバスを介して命令レジスタ内の命令を転送する、バスに接続されたデバッグ回路とを含み、処理ユニットがユーザプログラムの実行を中断して命令転送要求をデバッグ回路に対して行なうと、デバッグ回路は、命令転送要求と命令転送動作との間の期間においてバスの使用権を前記処理ユニットから解放させる応答を行なう。

(もっと読む)

制御回路、情報処理装置及び情報処理装置の制御方法

【課題】 データ送受信の履歴情報を通知する制御回路、情報処理装置及び制御方法を提供する。

【解決手段】 複数のシステムボードを有する情報処理装置において、各システムボードが有するチップ61の制御回路は、他のチップ61が送信したデータを受信する受信回路部611と、受信データが、データ送受信の履歴取得の指示が設定された履歴取得情報を含むトリガーパケット71であるかを判断し、受信データがトリガーパケット71である場合に履歴取得情報を読み取るトリガーパケット判定部612と、読み取った履歴取得情報に従って履歴情報の取得を開始又は停止する履歴取得実行部615と、トリガーパケット71又はこれ以外のパケットをデータとしてデータ受信回路に送信する送信回路部618とを有する。

(もっと読む)

ソースコードトレーサ

【課題】プログラムのデバッグをより効率的に行なうことができるソースコードトレーサを実現する。

【解決手段】プログラム方式の電子情報処理装置であるターゲットデバイス30と、そのプログラムであるソースコードをコンパイルし、コンパイル時にデバッグ行を挿入するコンピュータ7と、ターゲットデバイスのアドレスバス、データバス、またはインストラクションバスからデータを選択的に収集し記憶するデータ収集器10と、データ収集器から収集データを外部のコンピュータに伝送する通信路6と、を備える。特に、デバッグ行は、デバッグ行のソースコード上の位置情報を含むデバッグ情報を、予定のアドレス向けにデバッグデータとして出力する。この際、通過した時刻情報も出力してよい。また、上記データ収集器10は、設定した少なくとも1つのアドレスに一致する場合に、外部バスからデータを選択的に収集し記憶する。

(もっと読む)

コンピュータシステム及び異常検出回路

【課題】コンピュータシステム全体に対する初期化を行うことなく、ハングアップしたモジュールを初期化し再起動できるようにする。

【解決手段】バスを介して通信を行うマスターモジュール及びスレーブモジュールを有するコンピュータシステムにて、バスの信号を監視し通信に係るハングアップを検出するバスハングアップ防止モジュールをスレーブモジュール毎に配置し、ハングアップを検出した場合には、対応するスレーブモジュールのみの再起動を指示する信号を出力するようにして、コンピュータシステム全体に対する初期化を行わずに、ハングアップしたスレーブモジュールのみを初期化し再起動できるようにする。

(もっと読む)

1 - 20 / 76

[ Back to top ]