Fターム[5B042MC02]の内容

デバッグ、監視 (27,428) | 表示又は記録する内容 (5,146) | 内部状態情報 (289) | 命令 (40)

Fターム[5B042MC02]に分類される特許

1 - 20 / 40

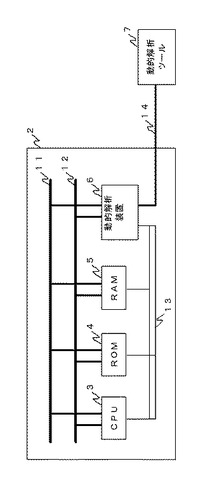

動的解析装置、動的解析システム、動的解析方法、及びプログラム

【課題】簡便に正確に制御装置等の動作を解析可能とする。

【解決手段】動的解析装置6は、解析対象のCPU3が接続される、アドレスバス11、データバス12、制御信号線13に接続される。動的解析装置6は、アドレスバス11上のアドレスの値から処理内容、例えば、実行中の関数や変数を特定し、データバス12上のデータから処理データ、例えば、変数の値を特定するデータ解析部と、データ解析部により解析された処理内容と処理データの履歴を含む履歴情報を記憶する記憶部と、動的解析ツール7からのアクセスに応答して、記憶部に記憶した履歴情報を提供する履歴情報提供手段と、を備える。

(もっと読む)

情報処理装置、およびその情報処理方法、プログラム、記録媒体

【課題】使い捨てできるテスト設定を作成し、代替え実行することで、本番用の設定・環境を変更することなくテストを実施する。

【解決手段】定められた処理の流れを実行するために複数のコマンドを用いて定義されたジョブをテーブルに管理し、管理されるジョブに含まれるコマンドのうち、仮想的に処理を実行するコマンドが定義された場合、テーブルに、仮想コマンドが設定された対応するコマンドのモードを仮想モードに変更すると共に、定義された仮想コマンドを、仮想コマンドテーブルに管理しておき、管理されるテーブルに含まれるジョブを実行する際に、実行対象となるコマンドが仮想モードであるかを判定して、判定の結果、仮想モードであると判定された場合、実行対象となるコマンドに対応する仮想コマンドを実行する。

(もっと読む)

マルチコアLSI

【課題】動作の安定性を向上できるマルチコアLSIを提供する。

【解決手段】このマルチコアLSI1は、第1の共有バスb1に接続された複数のCPU#0,#1と、第2の共有バスb2に接続された1個以上のモジュールm1〜mnと、第1の共有バスb1と第2の共有バスb2との間に接続され、複数のCPU#0,#1のモジュールへのアクセスを調停する共有バス制御部3と、アクセス先のモジュールから、CPU#0,#1のアクセス要求信号に対する応答信号が出力されたか否かを監視するシステムコントローラ9とを備え、システムコントローラ9は、共有バス制御部3から第2の共有バスb2にアクセス要求信号が出力されてから所定時間経過するまでに、アクセス先のモジュールから応答信号が出力されない場合は、共有バス制御部3を介して第1の共有バスb1に疑似応答信号を出力して、アクセス中のCPUの当該アクセスを終了させる。

(もっと読む)

情報処理装置、記録方法、及びプログラム

【課題】本発明が解決しようとする課題は、上記問題点を解決することであり、CPUの動作履歴記録用メモリーの容量を少量化することである。

【解決手段】上記課題を解決するための本発明は、記録装置であって、監視対象である情報処理装置のCPUの動作履歴が、ウォッチドッグタイマーのカウンター値がクリアされる周期に対応付けられて記録されている動作履歴記録部と、前記動作履歴を前記動作履歴記録部に記録し、前記クリア後に新たに前記CPUの動作を記録する際、前記CPUに障害が発生しなかった周期の動作履歴に上書きする記録手段とを有することを特徴とする。

(もっと読む)

コンピュータシステム、試験装置、試験方法、及び試験プログラム

【課題】追い越し機能が正常に動作しているか否かを信頼性よく試験することができる、コンピュータシステム、試験装置、試験方法、及び試験プログラムを提供する。

【解決手段】試験装置2と、先行命令のアクセス先仮想メモリアドレスが、後続命令のアクセス先仮想メモリアドレスと重複するか否かを判定し、重複しない場合に、前記後続命令が前記先行命令を追い越して実行されるように、処理装置によるメモリへのアクセス動作を制御する、命令追い越し回路12と、前記後続命令の追い越しが発生した場合に、前記後続命令を特定する情報を生成し、追い越し結果情報として保存する、追い越しトレーサ回路13とを具備する。前記試験装置2は、設定変更部5と、試験命令列生成部6と、追い越し判別部7と、試験命令列変更部8と、SWシミュレータ実行部9と、実行結果判定部10とを備える。

(もっと読む)

解析方法、解析装置及び解析プログラム

【課題】所望の位置でプログラムの動作を停止することができる解析方法、解析装置及び解析プログラムを提供すること。

【解決手段】コンピュータが、コンピュータで実行されるプログラムのプロセスに割り当てられるプロセスメモリ空間に対応するブレークメモリ空間に、プロセスを停止させるか否かを示すブレークポイント情報を記憶する。そして、プロセスにおいて命令が実行された場合に、命令が記憶されているプロセスメモリ空間に対応するブレークメモリ空間のブレークポイント情報に基づいて、プロセスを停止させるか否かを判定する。また、実行された命令がプロセスメモリ空間内でデータを代入する代入命令である場合に、データの代入先となるプロセスメモリ空間に対応するブレークメモリ空間の情報を、データが記憶されているプロセスメモリ空間に対応するブレークメモリ空間のブレークポイント情報に更新する。

(もっと読む)

ソフトウェア開発システム

【課題】エンディアン形式が異なる2つのプロセッサコアを備えるシステムを対象としたプログラムからエンディアン依存コードを検出すること。

【解決手段】実施形態によれば、2つのプロセッサコアモデルと、メモリモデルと、エンディアン依存コード検出部と、を備える。2つのプロセッサコアモデルは、エンディアン形式が夫々異なる2つのプロセッサコアと、2つのプロセッサコア間の転送データを一時記憶するバッファメモリと、を備えるシステムのターゲットプログラムを実行して2つのプロセッサコアの動作を夫々模擬する。メモリモデルは、バッファメモリを模擬する。エンディアン依存コード検出部は、データ転送先のプロセッサコアモデルがメモリモデルから転送データを読み出すロード命令を実行したとき、リードサイズに基づいてロード命令がエンディアン依存コードであるか否かを判定する。

(もっと読む)

相関トレースデータストリーム

【課題】データ処理システムの挙動とデバッギングとの診断を支援する目的で生成および分析されるトレースストリームを処理する方法および装置を提供する。

【解決手段】命令トレースストリーム10とデータトレースストリーム12とを含む複数のトレースストリームを生成するためのトレース回路を備えたデータ処理装置が提供される。データ要素と対応命令要素との間で一致が成立するように、命令トレースストリーム内の命令要素およびデータトレースストリーム内のデータ要素がキー値KVでマークされる。所定の条件が満たされると、データがその後分析されるときに命令要素とデータ要素との間で正確な相関が成立できるようにするために、同期マーカー66が命令トレースストリーム10とデータトレースストリーム12との両方で挿入される。

(もっと読む)

情報処理装置、デバッグ情報取得方法、およびデバッグ情報取得プログラム

【課題】少ないメモリ容量でメモリアクセスに関する情報を適切に保存し、異常解析を容易にすることが可能な情報処理装置、デバッグ情報取得方法、およびデバッグ情報取得プログラムを提供する。

【解決手段】情報処理装置201は、記憶部3のアドレスを指定し、記憶部3から指定アドレスにおけるデータを読み出すかまたは記憶部3の指定アドレスにデータを書き込むためのアクセス命令を少なくとも実行するための命令実行部1と、記憶部3において命令実行部1が読み出しまたは書き込みを行なう単位の領域ごとに、アクセス命令に対応するアクセス情報を記録するためのトレース領域をアクセス情報記録部4に設け、アクセス情報を取得して対応のトレース領域に保存するためのアクセス情報取得部2と、トレース領域に保存されたアクセス情報を出力するためのアクセス情報出力部5とを備える。

(もっと読む)

デバッグ方法、デバッグ装置、及びトランスレータプログラム

【課題】暗号化されていないCPU用のデバッガを用いて、ターゲットCPU上で動作する暗号化された命令列を含むプログラムのデバッグを容易に行う。

【解決手段】暗号化された命令列を復号化して実行するターゲットCPU(208)と、デバッガ(202)とを含むデバッグ装置を用いてデバッグを行う。上記ターゲットCPUと上記デバッガとの間にトランスレータ(204)を介在する。上記トランスレータは、上記デバッガから伝達された通信内容を上記トランスレータで上記ターゲットCPUに対応する内容に変換し、上記ターゲットCPUから伝達された通信内容を上記トランスレータで上記デバッガに対応する内容に変換する。このような変換を行うことで、ターゲットCPU上で動作する暗号化された命令列を含むプログラムのデバッグの容易化を図る。

(もっと読む)

ソフトウエアデバッグ装置及び方法

【課題】ソフトウェアのデバッグ中にブレークポイントを使用して関数呼び出し毎に実行を中断することなく、末尾呼び出しの最適化が行われた場合のコールスタックを正しく表示することができるソフトウエアデバッグ装置及び方法を提供する。

【解決手段】 ソースプログラムをコンパイル処理によって実行イメージプログラムと共に得られたデバッグ情報に応じて実行イメージプログラム中の関数毎の関数名及びアドレス情報をシンボルテーブルとして作成し、実行イメージプログラムのプログラムコード順にプログラムコードの命令を実行し、その実行命令が分岐命令である場合にその分岐命令のプログラムコードをオペラントを含めてトレースメモリに記憶させ、トレースメモリのオペラントとシンボルテーブルのアドレス情報との対応関係に応じて関数呼び出しの階層を示すコールスタックを作成してそれを表示する。

(もっと読む)

デバッグ支援装置およびデバッグ支援方法

【課題】デバッグ作業の効率化および工数の削減を図ること。

【解決手段】デバッグ支援装置1は、履歴情報格納部5と、制御部6とを有している。デバッガ2は、デバッグ用のプログラムをCPU4に転送する。命令処理部3は、デバッガ2がCPU4に転送したデバッグ用のプログラムに基づいてCPU4が発行したデバッグ対象の命令を処理する。処理命令格納部9は、キュー構造をなしており、命令処理部3に処理させる命令を一時記憶する。履歴情報格納部5は、処理命令格納部9に記憶される命令に関する情報を格納する。制御部6は、処理命令格納部9に記憶される命令に関する情報を履歴情報格納部5に格納する。このようにして履歴情報格納部5に格納された命令処理部3の動作に関する情報は、デバッガ2によって取得される。

(もっと読む)

プロファイリング方法およびプロファイリングプログラム

【課題】OS環境下で命令単位での細かいプロファイル情報を取得すること。仮想記憶機構を備えたOS環境下でプロファイリング対象プログラム(共用ライブラリを含む)のプロファイル情報のみを取得すること。

【解決手段】コンピュータシステムは、プロファイリング対象プログラム1、OS2およびプロセッサ3を備えている。プロファイリング対象のアプリケーションプログラム11と、サンプリング情報を収集するプロファイル取得関数ライブラリ12とを同一プロセスで起動する。プロセッサ3の内蔵タイマ15から割り込みが発生するたびに、OS2に予め組み込まれたプロファイル取得ドライバ13により、プログラムカウンタ16の値やハードウェアカウンタ17の値を収集する。仮想記憶システム上で複数のプロセスが実行される場合には、割り込みの発生時にプロファイリング対象プロセスが実行されているときにサンプリング情報を収集する。

(もっと読む)

プロセッサおよびデバッグ装置

【課題】低コストにプロセッサ間通信と、それに対応するプログラムの遷移前後の関連性に係る情報をトレースする。

【解決手段】マルチプロセッサシステムのトレースにおいて、プロセッサ間通信の発行数を発生順にカウントするカウンタを備え、プロセッサ間通信のプログラム実行履歴をメモリへ格納する際に、プログラム実行履歴のアドレスの一部を前記カウンタのカウント値に置き換え、メモリの未使用領域を示すアドレスにし、改変後プログラム実行履歴として格納する。メモリから取り出した改変後プログラム実行履歴のアドレスがメモリの未使用領域を示す場合、置き換えられたカウンタのカウント値を取り出すとともに置き換える前のアドレスに復元する。

(もっと読む)

プログラム診断装置及びプログラム診断方法ならびにそのプログラム

【課題】プログラムのソースコードの記述を改変することなく、また精度良く、競合状態を発生させる命令コードの検出および修正をプログラムの製作者が容易に行うことが可能となるプログラム診断装置を提供する。

【解決手段】上述の処理によれば、Java(登録商標)言語のソースコードから中間コードを生成し、その中間コードから、メモリ参照/書き込みを示す命令コードを検出する。そして、その命令コードの仮実行において、操作する変数がアンロック状態で実行される命令コードであると判定した場合には、その命令コードが記述されているソースコードの位置を画面に表示する。

(もっと読む)

演算回路及び演算回路の異常解析方法

【課題】商用運用中の機器であっても現状の動作に影響を及ぼすことなく、プログラムの状態を把握し、異常状態に至る過程も含めた解析を可能にする。

【解決手段】履歴メモリ30に蓄積された履歴情報を、コマンド制御装置50からの読み出しコマンドを用いて、履歴制御部20経由で履歴情報300として履歴メモリ30から読み出す。これにより、プログラム動作中の何度も異常が発生する状況に陥った場合でも、異常発生毎に履歴メモリ30上の異なる領域に履歴データを格納しているので、複数回の異常情報を過去に遡り得ることができ、異常になるまでの経緯を知ることができ、プログラムの障害解析の時間を短縮することが可能となる。また、プログラムが動作する生の監視情報102を予め決められた条件で取得するため、たとえ商用運用中の機器であっても現状の動作に影響を及ぼすこと無く、プログラムの状態が把握できる。

(もっと読む)

データベース・アクセス遅延の解析情報採取装置、解析情報採取方法およびプログラム

【課題】 データベース・アクセス遅延の解析を容易にすると共にデータベースの運用への影響を最小限に抑える。

【解決手段】 解析情報採取装置1は、データベース・アクセスにおける遅延条件に基づいてデータベース・アクセスを監視する手段3と、データベース・アクセスが上記遅延条件を満たしているときに、対象のデータベースに該データベース・アクセスを実行して、その解析情報を採取する手段4を備える。

(もっと読む)

計算機及び障害再現方法並びにプログラム

【課題】OSを起動できないような障害が発生した場合であっても、障害再現プログラムを用いて障害を再現できるようにする。

【解決手段】外部記憶装置6には、計算機1において発生した障害を再現するための、障害再現プログラム5aと、この障害再現プログラム5aを計算機1に読み込むためのブートローダ7とが格納されている。外部記憶装置6を計算機1に接続し(S803)、計算機を再起動すると(S804)、計算機1は、先ず、ブートローダ7を読み込んで実行し(S805)、その後、ブートローダ7により障害再現プログラム5aを読み込んで実行する(S806)。

(もっと読む)

解析装置及び解析方法及びプログラム

【課題】プログラムの実行状況を示す情報から、レジスタ値の変遷を再現する。

【解決手段】変更履歴エントリ追加部102が、プログラム実行環境200でのプログラムの実行中にプロセッサが実行した命令と命令実行によるメモリアクセスの内容が示される命令実行トレースデータ300を特定の時点から遡りながらひとつずつ取出し、取出したトレースデータの命令がレジスタを参照する命令の場合、レジスタ変更履歴データ107に履歴エントリを追加する。演算実行部105が、履歴エントリを見渡して、レジスタ間演算命令に示される演算を実行し、代入先レジスタの値を演算結果の値で確定し、レジスタ値確定部104が、履歴エントリに示されるレジスタ、命令の種類、メモリアクセスの内容、演算実行部105の演算実行結果をもとに、命令実行時の各レジスタの値を確定し、プログラム実行環境200でのプログラム実行中のレジスタ値の変遷を再現する。

(もっと読む)

半導体装置、及び半導体装置のデバッグ方法

【課題】プロセッサが実行していた異常終了直前の命令データを特定することができる。

【解決手段】LSI10は、バス13を介してプロセッサ12に入力された命令データを処理するパイプライン15、及びパイプラインに15よって処理された命令データが入力され、命令データに従って演算処理を行う演算実行回路16を有するプロセッサ12と、パイプライン15から演算実行回路16に入力される命令データを格納する記憶回路14と、を有するものである。

(もっと読む)

1 - 20 / 40

[ Back to top ]