Fターム[5B048AA02]の内容

デジタル計算機の試験診断 (4,118) | 被試験装置 (1,129) | 論理回路 (93) | 演算回路 (23)

Fターム[5B048AA02]の下位に属するFターム

パイプライン演算回路 (8)

Fターム[5B048AA02]に分類される特許

1 - 15 / 15

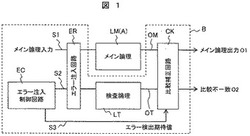

自己診断機能付き装置

【課題】自己診断する論理の範囲を比較回路以外の検査論理、更にはメイン論理に広げ、検査論理、メイン論理に異常がある場合、比較回路が不一致を発生する前に検出し装置の交換ができるようにする。

【解決手段】同じ入力が与えられ、同じ論理演算を実施する第1と第2の論理部、第1と第2の論理部のいずれかにエラー信号を与えるエラー注入回路、第1と第2の論理部の出力を入力し選択した信号を与える選択回路と第1と第2の論理部の出力を比較し、比較不一致信号を与える比較回路とを備えた比較補正回路から構成され、比較補正回路は、第1と第2の論理部のいずれかにエラー信号を与えた時、第1と第2の論理部の出力が不一致にならない場合、または、第1と第2の論理部にエラー信号を与えないときに、第1と第2の論理部の出力が不一致になる場合に異常があると判断する。

(もっと読む)

コンピュータシステム、試験装置、試験方法、及び試験プログラム

【課題】追い越し機能が正常に動作しているか否かを信頼性よく試験することができる、コンピュータシステム、試験装置、試験方法、及び試験プログラムを提供する。

【解決手段】試験装置2と、先行命令のアクセス先仮想メモリアドレスが、後続命令のアクセス先仮想メモリアドレスと重複するか否かを判定し、重複しない場合に、前記後続命令が前記先行命令を追い越して実行されるように、処理装置によるメモリへのアクセス動作を制御する、命令追い越し回路12と、前記後続命令の追い越しが発生した場合に、前記後続命令を特定する情報を生成し、追い越し結果情報として保存する、追い越しトレーサ回路13とを具備する。前記試験装置2は、設定変更部5と、試験命令列生成部6と、追い越し判別部7と、試験命令列変更部8と、SWシミュレータ実行部9と、実行結果判定部10とを備える。

(もっと読む)

情報処理装置、ウォッチドッグタイマ、異常検出方法

【課題】高い故障検出率を低コストで実現する情報処理装置、ウォッチドッグタイマ及び異常検出方法を提供する。

【解決手段】複数の演算器を有するプロセッサ11と、各演算器を選択的に作動させる1つ以上の関数が記述されたプログラムを記憶するプログラム記憶手段と、演算器が関数を実行した演算結果を記憶する第一の記憶手段41と、演算器が関数を正常に実行して得られる期待値を記憶する第二の記憶手段42と、演算結果と期待値を比較して演算器の異常を検出する第一の異常検出手段32と、演算結果と期待値の比較結果を記憶する演算器に関連付けられた第三の記憶手段43と、を有する。

(もっと読む)

故障制御装置、プロセッサコア、演算処理装置、情報処理装置および擬似故障制御方法

【課題】擬似故障の発生にかかる信号の伝播遅延を考慮した故障制御装置、プロセッサコアおよび擬似故障制御方法を得ること。

【解決手段】故障発生対象回路40_1〜40_nの近傍に、擬似故障を発生させる擬似故障発生装置30_1〜30_nを配置する。擬似故障制御装置20は、擬似故障発生装置30_1〜30_nのいずれかを選択してローカル故障モードレジスタ31に故障の内容をセットする。擬似故障発生装置30_1〜30_nは、故障の内容に対応するイベントの発生を監視して擬似故障制御装置20に通知し、擬似故障制御装置20は、イベントの発生回数に基づいて擬似故障発生装置30_1〜30_nに故障の発生を指示する。

(もっと読む)

回路動作検証方法及び装置

【課題】設計者の負担を削減しつつ消費電力削減用に加えた回路変更の動作検証を行う。

【解決手段】動作抑制のための制御信号によって信号値が固定された信号の伝播範囲が所定の範囲内に収まることを確認するために、論理シミュレーションの結果によって動作抑制モードになったことを検出した場合には、検出時刻及び信号値が固定されたネットを含む動作率抑制情報リストを信号値が固定されたネットに設定し、論理シミュレーションの結果に従って当該動作率抑制情報リストを次のネットに伝播する。回路変更が適切に行われていれば、論理シミュレーションの結果が動作率抑制情報リストの伝播条件を満たさないようになるので、所定の範囲以上には動作率抑制情報リストは伝播されず、問題ないと判断される。

(もっと読む)

誤り検出装置

【課題】デジタル演算処理装置におけるフリップフロップの遅延エラーを、回路占有面積を増大させることなく確実に検出する。

【解決手段】特定のフリップフロップ(FF(i))の入力および出力を受ける誤り判定回路(EDK)を設ける。この特定のフリップフロップ前段のフリップフロップ(FF(i−1))をラッチ状態に設定して、直後のサイクルで、誤り判定回路において、特定フリップフロップの入出力データの論理レベルの一致/判定を行ない、判定結果指示信号(Err)を生成する。

(もっと読む)

リコンフィグラブルデバイス搭載ボードのセルフテスト装置および方法

【課題】運用中にもセルフテストを実行でき、故障検出率を向上できること。

【解決手段】セルフテスト装置は、コンフィグレーションにより機能を変更自在なリコンフィグラブルデバイスを搭載したボード301の運用時の運用パラメータに基づいて、ボード301のデバイス310,320内にて運用に用いられる運用エレメント312,322と、非運用エレメントとをそれぞれ算出する運用メント決定部331と、運用メント決定部331によって算出された非運用エレメントのなかからセルフテスト対象のエレメント313,323,314,324を割り当てるエレメント割当決定部332と、エレメント割当決定部332によって割り当てられたエレメントを通過するテスト経路に対してテスト信号を通過させてエレメント313,323,314,324のテストを行うテスト手段とを備える。

(もっと読む)

中央演算処理装置のテスト回路装置

【課題】 この発明は、実体に近いプログラム処理のテストが行える回路を提供することを目的とする。

【解決手段】 比較値を格納する比較値レジスタ11と、比較値レジスタ11の内容とCPU本体の出力するアドレス値101とを比較する比較器12と、比較器12の比較結果を伝える比較結果信号22と、比較器11の比較結果とCPUに対するひとつの入力信号102のうちどちらか一方を選択し選択した方をCPUのロジック100に与える選択器13と、選択器13の選択内容を記憶する選択レジスタ14と、選択レジスタ14の内容を選択器13に伝える選択信号23を持つ。

(もっと読む)

データ処理システムを試験するための方法および装置

プロセッサ(12)の少なくとも1つの論理ブロックを試験するための方法は、プロセッサによるユーザ・アプリケーションの実行の間において、停止および試験指示子(24)を生成し、停止および試験指示子の生成に応じてユーザ・アプリケーションの実行を停止すること、および、必要に応じてプロセッサの少なくとも1つの論理ブロックの状態を保存することを含む。方法は、プロセッサの少なくとも1つの論理ロジックの試験に試験刺激を適用することをさらに含む。試験刺激は、ユーザ・アプリケーションの実行の間など、通常の動作の間、プロセッサのスキャン試験を実行するために、スキャン・チェーン内にシフトされる。  (もっと読む)

(もっと読む)

プロセッサの動作を検証する動作検証方法及び動作検証プログラム

【課題】計算機での動作検証を行うのに大量のデータパターンでの動作検証を可能とする動作検証方法及び動作検証プログラムを提供する。

【解決手段】検証プログラムの検証パターン数などのパラメタを設定する(S1)。検証対象である浮動小数点加算命令を作成する(S2)。この加算で使用するオペランドをランダムに作成する(S3)。作成した浮動小数点加算命令を固定小数点命令のみでエミュレートしプロセッサの固定小数点演算器のみを使用して処理し期待値を作成する(S4)。作成した浮動小数点加算命令を検証対象の浮動小数点加減算器を用いて演算する(S5)。固定小数点演算器のみを使用し作成した期待値と処理した結果との比較を行う(S6)。比較一致なら設定した演算パターン数をチェックし規定値に到達したなら正常終了と報告しプログラムを終了する(S8)。また比較が不一致となった原因を解析して出力しプログラムを終了する(S7)。

(もっと読む)

負荷検証要件特定装置、負荷検証要件特定方法及び負荷検証要件特定プログラム

【課題】 アプリケーションが正常に動作するかどうかを検証するテストの精度を向上すること。

【解決手段】 検証用アプリケーション11が利用される業務に関する検証用業務特性が入力される業務特性入力部23と、検証用アプリケーション11が実行するシナリオが入力される負荷検証シナリオ入力部24と、検証用アプリケーション11がそのシナリオを多重度が1であるという条件で実行したときの1アクセス当たりの実行時間を収集する実行時間収集部25と、複数業務特性を複数アクセス数に対応付けるアクセス数テーブル41を記憶するアクセス数記憶部22と、アクセス数テーブル41を参照して複数アクセス数のうちから検証用業務特性に対応する検証用アクセス数を抽出し、検証用アクセス数と実行時間とに基づいて検証用サーバ2により検証用アプリケーション11が実行されて検証されるときの負荷となる多重度を算出する負荷検証要件特定部30とを備えていることが好ましい。

(もっと読む)

レジスタ設定値監視モジュール、システムおよびレジスタ設定値監視方法

【課題】 ソフトウェア開発の初期の段階においてレジスタ設定値間違いを発見することができるレジスタ設定値監視モジュールを提供する。

【解決手段】 レジスタチェックモジュール4は、機能ブロック6,7,8の制御レジスタの設定値に対する期待値を格納する制御レジスタ群22と、CPUにより機能ブロック6,7,8の制御レジスタに対して設定される設定値と制御レジスタ群22に格納されている期待値とを比較する比較回路23とを有する。レジスタチェックモジュール4は、比較回路23による比較結果が制御レジスタ群22に対して設定される設定値と制御レジスタ群22に格納されている期待値との不一致を示す場合、CPU2に対してエラー通知を出力する。

(もっと読む)

演算処理装置及びその自己診断方法

【課題】期待値を必要とせず入力データのみにより演算器の自己診断を可能にして実装した自己診断回路の規模を小さくする。

【解決手段】自己診断機能を備えたプロセッサであり、診断対象となる加減算器12を備えた演算回路10−1と、自己診断用データを格納するデータ格納部14と、自己診断用データを入力して演算回路により演算結果が全ビットがオール0(はオール1)となるように診断処理を実行させる自己診断処理部10−2とを備える。

(もっと読む)

二重化システムの系切替試験システム

【課題】 二重化システムの切替確認試験を1台の情報処理装置で行う二重化システムを提供する。

【解決手段】 運用系と待機系の情報処理装置を持つ二重化システムの系切替試験システムにおいて、1台の情報処理装置内に通常切替発生時に通信を行う通信アダプタとは別の試験用通信アダプタと、その試験用通信アダプタを介して、運用系または待機系の切替通信処理を擬似的に行う系切替制御手段を有する。

(もっと読む)

自動的に生成されたテストプログラムのための採点機構

【課題】本発明は、テストコードの実行がシミュレートされている間に選択された機能状態の適用範囲で作られる評価をするテストプログラムの生成の自動化を提供する。

を提供する。

【解決手段】データ処理装置のためのテストプログラムは、テストプログラムを形成している集団におけるプログラム命令の順序付けられたリストからなる例の変更について、遺伝子アルゴリズムを使用して生産される。集団は、特定の例が集団の中又は外へ交換されるべきであるか否かについてなされる決定がされているとき、集団全体がデータ処理装置において所定の機能ポイントの刺激に対して採点されることによる測定を使用して評価される。

(もっと読む)

1 - 15 / 15

[ Back to top ]