Fターム[5B048AA03]の内容

デジタル計算機の試験診断 (4,118) | 被試験装置 (1,129) | 論理回路 (93) | 演算回路 (23) | パイプライン演算回路 (8)

Fターム[5B048AA03]に分類される特許

1 - 8 / 8

マルチスレッド・プロセッサ

【課題】複数の命令実行手段を備えるマルチスレッド・プロセッサにおいて、命令実行手段の正確な機能チェックを行うこと。

【解決手段】複数のスレッドがハードウエア・マルチスレッディング処理を行うマルチスレッド・プロセッサであって、前記複数のスレッドによって使用可能な、演算器その他の複数の命令実行手段と、前記複数の命令実行手段に対して前記複数のスレッドのいずれかに属する命令を発行すると共に、所定のタイミングで前記複数の命令実行手段の機能チェック用命令と該機能チェック用命令が正しく実行されたか否かを確認する確認用命令を発行する命令発行手段と、前記命令発行手段が前記機能チェック用命令を発行する際と、前記確認用命令を発行する際とで前記複数の命令実行手段のうち異なる命令実行手段に命令を発行するように前記命令発行手段を制御する制御手段と、を備えるマルチスレッド・プロセッサ。

(もっと読む)

演算装置及びエラー検出方法

【課題】エラーの検出効果を高くする。

【解決手段】演算装置1は、命令制御部100と、第1オペランド制御部200と、第2オペランド制御部300と、演算部400と、NOP検出部500と、エラー検出部600と、を備える。NOP検出部500が出力する制御信号に従って、命令制御部100、第1オペランド制御部200及び第2オペランド制御部300は、直前のクロックサイクルで受信した入力信号を試験信号として演算部400に出力する。エラー検出部600は、演算部400が求めた演算結果データと試験演算結果データとを比較し、エラーが発生しているか否かを判別する。

(もっと読む)

プロセッサ検証プログラム

【課題】プロセッサ検証時におけるパイプラインステージの検証すべき処理状態の生成に係る制御を自動化したプロセッサ検証プログラムを提供することにある。

【解決手段】 プロセッサの検証処理をコンピューターに実行させるコンピューター読み取り可能なプロセッサ検証プログラムにおいて、検証処理は、テスト命令列内の命令がパイプラインステージそれぞれで処理中か否かを示しパイプラインステージの検証すべき処理状態を規定するパイプラインステージ組合せパターンを参照し、テスト命令列の命令を実行するとき、パイプラインステージそれぞれで命令が処理中か否かを示すステータス情報に基づいてインターロック信号をパイプラインステージに供給することにより、パイプラインステージの命令の処理状態をパイプラインステージ組合せパターンと一致させるタイミング生成工程を有する。

(もっと読む)

情報処理装置の試験命令列生成方式

【課題】情報処理装置のテスト命令列生成処理において、テスト命令列の組み合わせを乱

数によって決定し、分岐ループ命令列を生成しない場合、分岐命令の分岐方向は一方向(

分岐あり又は分岐なし)しか試験することができない。また、単純な分岐ループ(1重ルー

プ)では、分岐命令の先行制御論理を網羅的に試験することが困難である。

【解決手段】 試験命令列生成時に、分岐命令による多重ループ命令列生成手段を設け、

分岐命令を分岐あり・なしの両方向実行できるような命令列生成及び分岐ループ回数によ

って分岐先の命令アドレスの変更を可能とし、分岐命令の先行制御論理試験を網羅的に効

率よく行えるようにする。

(もっと読む)

誤り検出装置

【課題】デジタル演算処理装置におけるフリップフロップの遅延エラーを、回路占有面積を増大させることなく確実に検出する。

【解決手段】特定のフリップフロップ(FF(i))の入力および出力を受ける誤り判定回路(EDK)を設ける。この特定のフリップフロップ前段のフリップフロップ(FF(i−1))をラッチ状態に設定して、直後のサイクルで、誤り判定回路において、特定フリップフロップの入出力データの論理レベルの一致/判定を行ない、判定結果指示信号(Err)を生成する。

(もっと読む)

故障検出プログラム作成装置、プリプロセッサ、故障検出プログラム作成方法、及びプログラム

【課題】プログラムの本来性能を低下させずにプロセッサの故障検出率を高めることを目的として、アセンブリ言語で記述されたソースプログラムに対し、演算を二重化するコードをプログラムの空き部分に挿入することを特徴とする。

【解決手段】プリプロセッサ(10)は、アセンブリ言語で記述したプログラム(1)の性能を低下させずに、プログラム(1)内の空き命令を見つけて、二重化パターンファイル(11)を参照して二重化パターンを挿入して自動的に演算を二重化する。二重化できない場合、前記プリプロセッサ(10)は、前記二重化パターンの挿入前後の前記命令の出現回数に基づいて二重化度を算出し、他の命令に比べて前記二重化度が低い命令についてランダムパターンファイルを参照してランダムパターンを生成し、性能を低下させずにプログラム(1)に挿入する。

(もっと読む)

電子回路、及びその動作方法

電子回路が提供され、電子回路は、第1及び第2の組み合わせ論理ブロック;及び前記論理ブロックの間に位置するラッチを有し;前記電子回路は、前記ラッチがイネーブル信号に応じて開閉される通常モード、及び前記ラッチが開に保持される試験モードで動作する。  (もっと読む)

(もっと読む)

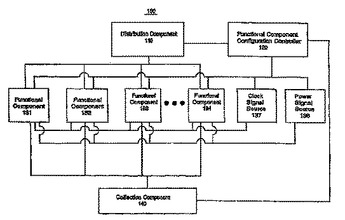

半導体機能回路のテストおよび構成のためのシステムおよび方法

集積回路において機能要素の構成を可能にするためのシステムおよび方法が開示される。本発明のシステムおよび方法が、製造欠陥、柔軟性特性、性能要求、およびシステムの健全性(例えば、適切に動作する要素の数)を含む種々の要因に基づいて、集積回路ダイの機能要素の動作特性を柔軟に変更し得る。様々なレベルの構成抽象化および要素組織化(例えば、トポロジーインバージョン解析)で、機能要素動作挙動がテストおよび解析される。テストおよび解析は、多数の機能要素で並列に実行され得る。様々なレベルの粒度および実時間で、グラフィカルユーザインタフェース(GUI)に機能要素構成関連の情報が提示される。グラフィカルユーザインタフェースは、フェイルパターンの認識、生産テストの調整、およびフィールド構成アルゴリズムの調節においてユーザの相互作用を容易にし得る。また、テストおよび解析情報は、種々の使いやすいデータベース形式で組織化され得る。  (もっと読む)

(もっと読む)

1 - 8 / 8

[ Back to top ]