Fターム[5B048CC02]の内容

デジタル計算機の試験診断 (4,118) | 試験方法 (877) | 基準パターンと比較 (179)

Fターム[5B048CC02]に分類される特許

1 - 20 / 179

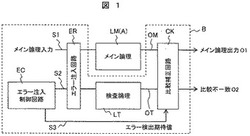

障害診断システム及び障害診断方法

自己診断機能付き装置

【課題】自己診断する論理の範囲を比較回路以外の検査論理、更にはメイン論理に広げ、検査論理、メイン論理に異常がある場合、比較回路が不一致を発生する前に検出し装置の交換ができるようにする。

【解決手段】同じ入力が与えられ、同じ論理演算を実施する第1と第2の論理部、第1と第2の論理部のいずれかにエラー信号を与えるエラー注入回路、第1と第2の論理部の出力を入力し選択した信号を与える選択回路と第1と第2の論理部の出力を比較し、比較不一致信号を与える比較回路とを備えた比較補正回路から構成され、比較補正回路は、第1と第2の論理部のいずれかにエラー信号を与えた時、第1と第2の論理部の出力が不一致にならない場合、または、第1と第2の論理部にエラー信号を与えないときに、第1と第2の論理部の出力が不一致になる場合に異常があると判断する。

(もっと読む)

スキャンパタン作成手法、プログラム、スキャンパタン作成装置、テスタ、及びテスト方法

【課題】スキャンテストに要する時間を削減するテストパタン作成方法を提供する。

【解決手段】テストパタン作成方法は、組み合わせ論理回路と少なくとも一つのスキャンチェーンとに関する情報を、記録媒体から読み出し、少なくとも一つのスキャンチェーンの入力側に近いフリップフロップから順番に抽出し(ステップS21)、抽出したフリップフロップがスキャンキャプチャ動作によって組み合わせ論理回路から取り込むキャプチャデータと照合する期待値の必要性を判定し(ステップS22〜S25)、期待値が不要と判定されたフリップフロップが入力側から連続して存在するフリップフロップの数を取得し(ステップS27)、スキャンチェーンに含まれるフリップフロップの総数と、取得したフリップフロップの数との差分を、スキャンキャプチャ動作後のスキャンシフト回数として決定する(ステップS28)。

(もっと読む)

バス診断機能を備えた制御装置

【課題】安全関連部と非安全関連部が混在している制御装置において、中央処理部が安全関連部にアクセスしたときのみ、データバス及びアドレスバス上の転送エラーを検知する制御装置を提供する。

【解決手段】制御装置の集積回路6a内に、CPU1aが安全関連レジスタにアクセスする際に、安全関連レジスタの値を格納するデータバス診断レジスタ12と、アドレスバスの値を格納するアドレスバス診断レジスタ13と、CPU1aが安全関連レジスタにアクセスする際にのみ、データバス診断レジスタ12に安全関連レジスタの値を、アドレスバス診断レジスタに13アドレスバスの値を夫々格納させるためのバス診断信号(CHKBUS)15を、データバス診断レジスタ12及びアドレスバス診断レジスタ13に供給するバス診断アドレス判定部14とを設ける。

(もっと読む)

集積回路、画像形成装置及び集積回路検査方法

【課題】本発明は、ASIC等の集積回路を単体で工数を削減しつつ、安価かつ適切に評価する。

【解決手段】エンジンASIC11は、動作モード切り替え用レジスタ39にテストモードが設定されると、スキャナ5から入力される画像データに対して、S2M画像処理モジュール31が、ライン同期信号s_lsync_n及びフレーム有効信号s_fgate_nに基づいて画像処理を施して、WDMAC33a〜33dがライト用アービタ35、リードデータセレクタ(R_SEL)40を介してバッファ制御部38に保管し、バッファ制御部38の画像データをRDMAC34a〜34dがリード用アービタ36、リードデータセレクタ(R_SEL)41を介して読み取ってM2P画像処理モジュール32に送る。M2P画像処理モジュール32は、該画像データに対して画像処理してプロッタ6に出力する。

(もっと読む)

半導体集積回路の機能検証装置

【課題】開発期間や開発コストを低減することができる、半導体集積回路の機能検証装置、及び半導体集積回路の機能検証方法を提供する。

【解決手段】テストシナリオ31に従いスティミュラスを生成するスティミュラス生成部321と、論理回路322から得られる出力値と期待値とを比較して一致するか否かを判定する結果判定部323と、出力値と期待値が不一致であると判定された場合に不一致情報をFailログ34として出力するFailログ生成部326と、論理回路322内の全ての信号・レジスタ・記憶素子の値を論理回路状態情報として論理回路状態情報記憶部33に保存させる状態ダンプ部324と、出力値と期待値が不一致であると判定された場合に論理回路状態情報記憶部33に保存されている論理回路状態情報を論理回路322にロードさせる状態ロード部325と、を備えていることを特徴とする。

(もっと読む)

故障箇所推定装置と方法並びにプログラム

【課題】スキャンテスト設計が施された機能ブロックと付加回路とを含む論理回路全体を故障診断を可能とし、診断処理時間を大幅に短縮可能とする装置、方法の提供。

【解決手段】論理回路内のスキャンフリップフロップで構成されるスキャンチェーンの構成情報、論理回路の設計情報を入力データ1として入力し、論理回路においてパラレル領域以外の回路部をシリアル領域として抽出することで、前記論理回路を前記パラレル領域とシリアル領域に分割する回路分割手段2と、正常回路における論理値を期待値として求める期待値計算手段3と、テストパタンに対する論理回路のテスト出力を入力データ1として入力し、テスト出力および、シリアル領域とパラレル領域の期待値を用いて、パラレル領域およびシリアル領域を故障診断し、出力部に出力する故障診断手段4とを備える。

(もっと読む)

ICカード及びプログラムコードの診断方法

【課題】 プログラムコードの自己診断によって特定のコマンド処理に不具合が発生すること、あるいはプログラムコード自己診断の実行が不十分となることを回避することのできるICカード及びプログラムコードの診断方法を提供する。

【解決手段】 外部からのコマンドを解釈実行し、その結果を応答するICカード(1)において、ICカードで実行されるプログラムを格納するプログラム領域(104)と、外部からコマンドを受信する受信部(13)と、コマンドに対応した処理、及びプログラム領域内のプログラムについてプログラムコードの良否診断処理を実行する制御部(101)とを有し、制御部は、プログラムコードの良否診断を、受信部が所定のコマンドを受信する毎の複数回に分割して実行し、分割された良否診断を実行した後で当該所定のコマンドの処理を実行するICカードである。

(もっと読む)

情報処理装置、故障検出装置、故障検出方法

【課題】CPUの故障率を検出するためのデータをより少ない記憶容量で記憶可能な情報処理装置を提供すること。

【解決手段】重複しないランダムパターンを生成するランダムパターン生成手段11と、前記ランダムパターンに演算を施す演算手段20と、前記ランダムパターンから一意に特定されるアドレスに、前記演算手段が前記ランダムパターンに演算を施した際の期待値を記憶した期待値記憶手段13と、前記演算手段の演算結果と、前記期待値記憶手段から読み出された期待値を比較する比較手段15とを有する。

(もっと読む)

テスト装置、テスト方法、プログラム及び記録媒体

【課題】 テストパワー考慮型のテスト生成において、テストパターン安全性を保証することを達成するテスト装置等を提供する。

【解決手段】 論理回路の故障の有無を判定するテスト装置であって、初期テストキューブが与えられ、初期未定値ビットに論理値を割り当てて中間テストパターンを生成する手段と、テストパターンが印加された論理回路に故障がなければ危険ビットが存在しないというテストパターン安全性を判定する手段と、テストパターン安全性を保証することに寄与しうる候補ビットを特定する手段と、初期未定値ビットにも候補ビットにも対応した中間テストパターンの入力ビットを新規未定値ビットとして新規テストキューブを生成する手段と、新規未定値ビットに論理値を割り当てて最終テストパターンを生成する手段と、最終テストパターン安全性を判定する手段と、論理回路テストにおいて危険ビットを使用させないマスク手段とを備える。

(もっと読む)

処理装置,制御装置および処理方法

【課題】高密度実装に伴い処理装置を成す各ボードに実装される部品の数が増大しても、処理装置の効率的な制御を実現する。

【解決手段】複数のボード20のそれぞれにおいて、管理部10からの実行指示に応じ、各ボード20上で実行されるべき一連の処理手順を記憶した記憶部20bから処理手順を一つずつ読み出し、読み出された処理手順に応じた処理を各ボード20上で順次実行させて複数の部品21a,21b,22a〜22cを制御し、一連の処理手順の実行結果を管理部10に通知する。

(もっと読む)

チャネル装置の診断方法

【課題】

光インタフェースを備えたチャネルでループバック試験を実施する場合、操作者は、ループコネクタの装着の他に、チャネルのオフライン作業と診断プログラムの操作を手動で行う必要があった。

【解決手段】

チャネル装置は、入出力装置との入出力動作を実行するCHプロセッサと、前記CHプロセッサとの間で入出力信号の信号変換を行う光モジュールとを備え、前記チャネル装置と前記入出力装置はそれぞれ装置固有の識別情報を有し、前記CHプロセッサは、ログイン処理により受信した識別情報が前記チャネル装置識別情報と一致している場合には自己診断処理を実行し、不一致の場合には入出力動作を実行する。

(もっと読む)

コンピュータシステム、試験装置、試験方法、及び試験プログラム

【課題】追い越し機能が正常に動作しているか否かを信頼性よく試験することができる、コンピュータシステム、試験装置、試験方法、及び試験プログラムを提供する。

【解決手段】試験装置2と、先行命令のアクセス先仮想メモリアドレスが、後続命令のアクセス先仮想メモリアドレスと重複するか否かを判定し、重複しない場合に、前記後続命令が前記先行命令を追い越して実行されるように、処理装置によるメモリへのアクセス動作を制御する、命令追い越し回路12と、前記後続命令の追い越しが発生した場合に、前記後続命令を特定する情報を生成し、追い越し結果情報として保存する、追い越しトレーサ回路13とを具備する。前記試験装置2は、設定変更部5と、試験命令列生成部6と、追い越し判別部7と、試験命令列変更部8と、SWシミュレータ実行部9と、実行結果判定部10とを備える。

(もっと読む)

制御装置の試験装置

【課題】車種ごとに異なる複数の機能を有する電子制御装置を有する電子制御システムの動作状態を試験する場合であっても、車種によってタイミングを修正することなく、車両の動的特性を考慮した制御装置の試験装置を提供する。

【解決手段】予め定められた手順書に基づいて、CANを介してECUへ操作情報を出力する出力手段と、操作されたECUからCANを介して情報を受信する受信手段と、受信された情報と、手順書に記載されたCAN期待値と、を比較し、比較した結果を判定結果として出力する判定手段と、を有する制御装置の試験装置。

(もっと読む)

情報処理装置、異常検出方法

【課題】異常のあるCPUコアを特定できない場合でも適切なフェールセーフ処理が可能な情報処理装置を提供すること。

【解決手段】プログラム記憶手段12と、ロックステップモードから非同期モードに切り替えるモード切り替え手段30と、を備えた情報処理装置100であって、ロックステップモードの第1の演算手段と第2の演算手段の演算結果を比較する比較手段32と、演算結果が一致しない場合、モード切り替え手段がロックステップモードから非同期モードに切り替えた後、第1の演算手段と第2の演算手段にそれぞれ自己診断ソフトを実行させるソフト制御手段31と、を有し、2つの演算手段の自己診断の結果がいずれも正常な場合、モード切り替え手段が非同期モードからロックステップモードに切り替えた後、ソフト制御手段が、自己診断ソフトの実行により動作が保証されたフェールセーフソフトを第1の演算手段と第2の演算手段にそれぞれ実行させる。

(もっと読む)

情報処理装置、ウォッチドッグタイマ、異常検出方法

【課題】高い故障検出率を低コストで実現する情報処理装置、ウォッチドッグタイマ及び異常検出方法を提供する。

【解決手段】複数の演算器を有するプロセッサ11と、各演算器を選択的に作動させる1つ以上の関数が記述されたプログラムを記憶するプログラム記憶手段と、演算器が関数を実行した演算結果を記憶する第一の記憶手段41と、演算器が関数を正常に実行して得られる期待値を記憶する第二の記憶手段42と、演算結果と期待値を比較して演算器の異常を検出する第一の異常検出手段32と、演算結果と期待値の比較結果を記憶する演算器に関連付けられた第三の記憶手段43と、を有する。

(もっと読む)

半導体回路およびそのテスト方法

【課題】効率よくテストを行うことが可能な半導体回路およびそのテスト方法を提供する。

【解決手段】半導体回路のテスト方法は、まず、少なくとも1つの引数と、テスト対象の半導体回路のテストを行うためのテストプログラムとを含むテストパタンの基本フォーマットを生成し、テスト装置内に記憶する。次に、前記引数に所定の値を設定して、前記テストプログラムおよび前記所定の値が設定された引数を含むテストパタンを生成し、前記テスト対象の半導体回路に供給する。次に、前記テストプログラムを前記半導体回路内に設けられる記憶部の第1のアドレスに格納し、かつ、前記所定の値が設定された引数を前記記憶部の第2のアドレスに格納する。さらに、前記第2のアドレスに格納された引数を参照しつつ、前記第1のアドレスに格納された前記テストプログラムを実行する。

(もっと読む)

演算制御装置、演算制御装置制御方法およびその制御用プログラム

【課題】複数のレジスタの値が一致したか否かをCPUのレジスタリード時に確認する。

【解決手段】レジスタ21乃至2nに保持された各テストデータが全て一致しているか否か比較判定部40で比較し比較結果を全比較結果Iとして出力すると共に、データ選択部30によって選択されたレジスタ21乃至2nのいずれか一つのレジスタの値とレジスタ21乃至2nの各値とがそれぞれ一致するか否か比較判定部40で比較し比較結果を個別比較結果J乃至Mとして出力し、選択されたリードデータと全比較結果Iとをビット連結部50で連結しリードデータ+全比較結果Fとして出力する。

(もっと読む)

検査装置

【課題】検査対象信号処理装置の内部状態をトリガに検査を行なう検査装置において、検査対象信号処理装置から状態信号を引き出すことなく、再現性のある検査を行なうことができるようにする

【解決手段】信号処理装置の内部状態をトリガにして信号処理装置の検査を行なう検査を行なう検査装置であって、信号処理装置に検査用データ信号を出力する入力発生部と、信号処理装置から検査用データ信号に応じて出力されたデータ信号を入力して、期待される値となっているか判定する出力判定部と、信号処理装置の内部状態を模擬し、模擬した内部状態があらかじめ設定されたトリガ発生条件に合致する場合にトリガを発生する検査対象動作模擬部と、トリガに基づいて、入力発生部に検査用データ信号を出力させるシーケンス制御部と、信号処理装置と共通のクロックを検査装置内に供給するクロック供給部とを備える。

(もっと読む)

プラント制御装置の試験装置

【課題】

本発明は、プラント制御装置の試験の際にプラントシミュレータ装置を用いる必要がなく、また、試験者の知識量によって試験結果の評価精度が左右されることの少ない試験装置を提供する。

【解決手段】

試験済みの制御装置11による制御対象プラント16の実運転中に発生した操作量信号、状態フィードバック信号及び制御信号を相互に関連付けてプラントデータ記録装置14に記録しておく。試験時には、プラントデータ記録装置14により記録された信号をプラントデータ再生装置23によって再生し、再生操作量信号及び再生状態フィードバック信号を被試験制御装置21に入力する。そして、入力信号に対応する制御信号を被試験制御装置21に出力させ、被試験制御装置21から出力される制御信号とプラントデータ再生装置から出力される再生制御信号とを比較可能な態様で表示装置22,24,25に表示する。

(もっと読む)

1 - 20 / 179

[ Back to top ]