Fターム[5B054DD15]の内容

Fターム[5B054DD15]の下位に属するFターム

ヒステリシス特性を有するもの (4)

信号出力時間を確保するためのもの (13)

Fターム[5B054DD15]に分類される特許

1 - 20 / 58

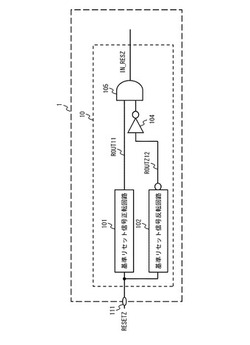

リセット信号生成回路及びそれを備えた半導体集積回路

【課題】ノイズや縮退故障等による意図しないリセット信号の解除を防止することが可能なリセット信号生成回路及びそれを備えた半導体集積回路を提供すること。

【解決手段】本発明にかかるリセット信号生成回路は、基準リセット信号RESETZを第1ノードに伝達するための信号線ROUT11と、基準リセット信号RESETZの反転信号を第2ノードに伝達するための信号線ROUTZ12と、第2ノードに伝達された信号の反転信号を出力するINV回路104と、第1ノードに伝達された信号の論理値と、INV回路104の出力信号の論理値と、が一致しない場合、基準リセット信号RESETZに関わらずリセット信号IN_RESZをアクティブにするAND回路105と、を備える。

(もっと読む)

携帯情報端末

【課題】 リセット動作を制限する。

【解決手段】 携帯電話1は、アプリケーションプログラムを実行可能なCPU21と、電源をオンした状態とオフした状態とに切換える指示を受付けるための電源スイッチ14Bと、電源スイッチ14Bが所定時間閉ざされると、CPU21を再起動させるためのリセット信号を出力するリセット検出回路20とを備え、CPU21は、リセット可能な状態とリセット不可能な状態とのいずれかを示す状態信号SL1を出力し、リセット検出回路20は、状態信号SL1がリセット可能な状態を示すこことを条件に、ハイの信号S4(リセット信号)をリセット回路41に出力する論理積素子27を含む。リセット回路41は、リセット検出回路20からハイの信号S4(リセット信号)が入力されると、CPU21にローの信号SL5(リセット信号)を出力する。

(もっと読む)

通信モジュールおよび車載機器

【構成】 通信モジュール10は、プロセッサ18を含み、プロセッサ18は、リセット回路26からのリセット信号に応じて、所定のリセットの処理を実行する。電源オフ状態から電源オン状態になると、外部電源が電源回路24に供給され、電源回路24は、各回路コンポーネントに電源を供給する。このとき、リセット回路26からプロセッサ18にリセットが要求される。また、外部機器からのリセット制御信号は、リセット回路26を介してプロセッサ18に与えられる。したがって、外部機器からプロセッサ18にリセットが要求される場合がある。リセット判別回路28は、外部機器からのリセットの要求であるかどうかを判別し、その判別結果をプロセッサ18に入力する。したがって、プロセッサ18は、リセットの種類に応じたリセットの処理を実行する。

【効果】 簡単な構成でリセットの種類を判別し、適切なリセットの処理を実行することができる。

(もっと読む)

電源制御回路及び電源制御方法

【課題】電源投入時に電源電位が安定するまでの待ち時間を改善する電源制御回路及び電源制御方法を提供する。

【解決手段】常時通電領域113と、少なくとも1つの電源遮断領域112とを有する半導体集積装置の電源制御回路200であって、検出部210と制御部220とを備える。検出部210は、電源遮断領域112の電源電位が、電源遮断領域の電源電位の安定を判定する下限の電源電位より低くなる回数をカウントする。そして、電源遮断領域112の電源電位が常時通電領域113の電源電位より高くなるときに、カウントした回数が増加していないことを検出する。制御部220は、検出部210がカウントした回数が増加していないことを検出した場合、電源遮断領域112のリセット状態を解除する。

(もっと読む)

リセット回路およびシステム

【課題】 パワーオンまたはパワーダウンを検出するリセット回路を誤動作することなく動作させ、パワーオン時にリセット信号を正常に出力する。

【解決手段】 電源検出回路は、電源電圧が第1電圧を超えたときにパワーオン状態を示すパワーオン信号を活性化するとともに、初期化信号の活性化中に初期化される。スタータ回路は、電源電圧線と接地線の間に直列に配置された抵抗素子、遮断スイッチおよびキャパシタを有し、抵抗素子と遮断スイッチとを接続する第1接続ノードから初期化信号を出力する。遮断スイッチは、パワーオン信号の活性化中にオフする。このため、パワーオン状態中に、抵抗素子を介してキャパシタが充電されることを防止できる。この結果、キャパシタのTDDBの劣化を確実に防止でき、リセット回路を搭載する半導体装置およびシステムの誤動作を防止できる。

(もっと読む)

電子回路、パワーオンリセット回路、集積回路装置及び電子機器

【課題】電源投入時に初期状態を確実に設定できる電子回路、パワーオンリセット回路、集積回路装置及び電子機器等を提供すること。

【解決手段】電子回路は、各回路素子がトランジスターで構成される複数の回路素子XA1〜XB2と、第1の高電位電源電圧VDDが供給され、VDDが所定の電圧レベルになるまでは、低電位電圧レベルに設定され、VDDが所定の電圧レベルを越えると、VDDに追従して電圧レベルが上昇する第2の高電位電源電圧VINTを出力する電源出力回路100とを含む。複数の回路素子のうち、初期状態においてその出力ノードが高電位電圧レベルになる回路素子である第1のグループの回路素子XA1、XA2には、VDDが供給され、初期状態においてその出力ノードが低電位電圧レベルになる回路素子である第2のグループの回路素子XB1、XB2には、VINTが供給される。

(もっと読む)

半導体集積回路、画像形成装置

【課題】機能モジュールがリセット中において、機能モジュールの動作モードを他の動作モードに切り換えることができる半導体集積回路及び画像形成装置を提供する。

【解決手段】システムリセット信号がアサートされたときにリセットされる機能モジュール25と、機能モジュール25に、機能モジュール25に設定されている動作モード以外の他の動作モードの設定を受け付けることを要求する切換要求信号を出力する制御部10に接続され、切換要求信号を受け付けたときに切換要求信号を保持する信号保持部20と、信号保持部20に保持された切換要求信号を受け付けて機能モジュール25に出力する信号出力部21と、システムリセット信号がアサートされたときに、信号保持部20に保持されている切換要求信号を信号出力部21に伝達して、機能モジュール25に向けて出力させる信号出力制御部23と、を備える。

(もっと読む)

自動測定と回復を行うシステム

【課題】現在のタッチコントロール装置に存在する欠点を克服する、新たな構造の、自動測定と回復を行うタッチコントロールシステムとそのリセット装置を提供する。

【解決手段】主に状態測定器、制御信号発生回路及びリセット制御回路を含む。状態測定器はタッチコントロール装置に内設されるフレームのオン/オフ状態を測定し、対応する状態信号を発生させる。制御信号発生回路は状態信号に基き対応する制御信号を発生させる。リセット制御回路は制御信号に基きタッチコントロール装置のリセットを行う。これにより、タッチコントロール装置はフレームのオン/オフ状態の変更後にリセットを行い、変更後のタッチコントロール環境下でタッチコントロール環境を再検索し、タッチコントロール精度を回復させる。本発明は自動測定と回復を行うタッチコントロールシステムを更に提供する。

(もっと読む)

パワーオンクリア回路

【課題】電源電圧の立ち上がり状態の影響を受けないクリア信号を生成、出力するパワーオンクリア回路を提供する。

【課題の解決手段】パワーオンクリア回路は、電源の投入によってパルスを発生するパルス発生回路1と、発生したパルスを遅延して出力する遅延回路5と、遅延されたパルスが入力する縦続接続した2段のインバータ6,7と、遅延回路5の前段側の出力が入力する入力端子と1段目のインバータ6の出力が入力する入力端子とを有するNOR回路8とを備え、NOR回路8の出力を電源電圧の立ち上がり状態の影響を受けない第1のクリア信号とし、インバータ7の出力を電源電圧の立ち上がり状態に応じた第2のクリア信号とするものである。

(もっと読む)

リセット回路

【課題】従来の低電圧を検知して、リセットをかける構成では、低電圧の設定値を超えると、リセットが解除され、通常電圧に復帰するまでの過程で、誤動作が発生する危険がある。例えば、リセットが直ぐに解除されると、十分に高い電圧で無い状況で、再起動が開始されることになり、レジスタ設定の誤書込みなどで、誤動作が発生するなど、信頼性面で問題があった。

【解決手段】本発明は、第1の検出電圧を検出する第1検出器と、前記第1の検出電圧より低い第2の検出電圧を検出する第2検出器と、前記第1検出器及び前記第2検出器からの検出結果を受け、リセットの要求を行うリセット要求信号の出力制御を行う制御回路と、を備え、前記制御回路は、前記第2の検出電圧を下回った後、前記第1の検出電圧を上回った時、前記リセット要求信号を変化させ、リセットの要求を行うことを特徴とする。

(もっと読む)

リセット制御回路

【課題】半導体集積回路のセキュリティレベルをハードウェア的に向上させることのできるリセット制御回路を提供する。

【解決手段】リセット制御回路1は、メモリ11に、リセット解除タイミングの設定値が予め書き込まれ、カウンタ12が、電源が投入されるとフリーラン動作し、トリガ信号出力部13が、カウンタ12からのオーバーフロー信号の出力ごとにトリガ信号を出力し、キャプチャ部14が、トリガ信号の出力後に入力リセット信号がリセット解除状態になったときのカウンタ12のカウント値をキャプチャし、比較部15が、キャプチャ部14にキャプチャされたカウント値がメモリ11に格納されたリセット解除タイミング設定値と一致するかどうかを比較し、ANDゲート16が、比較部15の出力とリセット信号との論理積をとり、内部リセット信号として出力する。

(もっと読む)

半導体装置

【課題】選択的にリセット動作を実行可能な半導体装置を提供すること。

【解決手段】半導体装置は、リセット動作を開始する際に外部から入力される信号を受けて活性化し、第1のトリガー信号RST_TRIG1を出力するリセットシーケンス回路25と、パワーオンリセット信号PWON_RSTb、及び前記リセットシーケンス回路25から出力された前記第1のトリガー信号RST_TRIG1に応答して、リセット対象となる回路毎に、リセット信号RSTを出力するリセット制御回路27と、外部から入力可能とされ、且つ前記リセット対象となる回路の選択情報、を保持可能なラッチ回路26とを具備し、前記リセット制御回路27は、前記ラッチ回路25に保持される前記選択情報に応じて、前記回路毎に前記第1のトリガー信号RST_TRIG1を選択的に制御する。

(もっと読む)

リセット信号生成回路

【課題】電源電圧が変動したときに不完全な短いパルスのリセット信号が出力されることを防止するリセット信号生成回路を提供する。

【解決手段】ノードBはパワーオンリセット時にはハイレベル、動作時にはローレベルである。動作時に電源(Vcc)が変動してノードCが一瞬でもハイレベルになるとスイッチ素子MN50がオンし、ノードBをローレベルに引き下げ、安定したローレベルのリセット信号RST1を出力する。ノードBがローレベルになるとスイッチ素子MN51は遅延してオフになり、容量104と105は充電回路112により徐々に充電される。ノードBの電位がインバータ回路106のスレッシュホールドレベルを超えるとリセット信号RST1はハイレベルに戻りリセットが解除され、スイッチ素子MN50はオフ、スイッチ素子MN51はオン状態に戻る。

(もっと読む)

リセット回路および電源制御用半導体集積回路

【課題】電源電圧が所定電圧より低い状態から上昇した場合に誤ってリセット解除信号が出力されてしまうのを回避することができるリセット回路およびそれを内蔵した電源制御用ICを提供する。

【解決手段】電源電圧に比例した電圧と参照電圧とを比較する電圧比較手段(CMP0)と、該電圧比較手段によって電源電圧が所定の電位以上になったことが検出された場合にその検出タイミングを遅らせて後段に伝える第1の遅延手段(DLY1)と、前記電圧比較手段によって電源電圧が所定の電位以下になったことが検出された場合にその検出タイミングを遅らせて後段に伝える第2の遅延手段(DLY2)と、を備えたリセット回路において、前記第2の遅延手段は、該遅延手段内部のノードの電位を論理しきい値で判定する第2判定回路(INV3)と、前記ノードに接続され電源電圧の上昇時に該ノードの電位を引き上げるプルアップ手段(SW3,GT1)とを設けるようにした。

(もっと読む)

リセット回路

【課題】記憶装置へのデータ書き込み中のリセット信号入力によるリセット動作を、データ書き込みに必要な時間だけ遅延させる。

【解決手段】CPU105がフラッシュROM106にデータを書き込んでいる途中の時刻で、ユーザによるリセット操作によりフリップフロップ100にリセット信号109が入力された場合、CPU105がフラッシュROM106にデータを書き込んでいる間は、リセット遅延信号107が‘H’レベルであるため、論理積回路102の出力信号は、常に‘L’レベルとなる。一方、遅延回路101からフリップフロップ100の出力信号が遅延されて出力されるまでの遅延時間が、データ書き込みに要する一回の最大アクセス時間より長く設定されているため、遅延回路101の出力信号は ‘L’レベルのままである。従って、データ書き込み中はCPU105のリセットを行わないようにできる。

(もっと読む)

リセット制御を有する集積回路装置

【課題】複数の内部回路ブロックのリセット解除タイミングを整合させた集積回路装置を提供する。

【解決手段】集積回路装置は,リセット信号に応答して第1のリセット動作を行う第1の内部回路ブロックと,第1のリセット動作と異なる第2のリセット動作を行う第2の内部回路ブロックとを有する。集積回路装置は,第1のリセット信号のリセット状態に応答して第1の内部回路ブロックに第1の内部リセット信号を出力する第1の内部リセット信号生成回路と,第2の内部回路ブロックが第1のリセット信号に応答して生成する第2の内部リセット信号を監視し,当該第2の内部リセット信号がリセット状態になったことを検出してリセット制御回路に第1のリセット信号を解除状態にさせる第2の内部リセット信号検出回路とを有する。第1の内部リセット信号生成回路は,第2の内部リセット信号が解除状態になったことに応答して第1のリセット信号を解除状態にする。

(もっと読む)

CPUボード

【課題】実装部品を削減すると共に、不用意な操作によるモード切り替えの危険を回避したCPUボードを実現する。

【解決手段】それぞれがメモリを有するメインCPU及びサブCPUを備え、第1のモードではダウンロードツールより前記メインCPU及びサブCPUのメモリにデータをダウンロードすると共に、第2のモードではユーザ支援ツールと前記メインCPUとが通信するCPUボードにおいて、

前記ダウンロードツールまたは前記ユーザ支援ツールと、前記メインCPUまたは前記サブCPUとの通信を中継するメインコネクタ手段と、

前記第1のモード時に、前記メインCPUに与えるXBOOT信号を生成する第1スイッチ手段の信号を入力するサブコネクタ手段と、

前記第1のモード時に、前記メインコネクタ手段からのデータを前記メインCPUまたは前記サブCPU手段に選択的に渡す切替手段と、

前記第1のモード時に、前記切替手段を操作する切替指令信号を生成する第2スイッチ手段と、を備える。

(もっと読む)

リセット信号監視回路

【課題】バッファ回路の特性に因らず誤出力を防止し、また、回路構成の相違による異常出力信号がロックされることを防止する。

【解決手段】異なるリセット電圧を出力する第1、第2のリセット信号発生回路11、12と、出力動作がロックされる第1、第2のバッファ回路13,14を設け、第1のリセット信号発生回路11で発生したリセット電圧は、タイマー回路15に入力され、このタイマー回路15は、リセット信号が一定時間継続しているかを監視し、検出する。リセット信号が継続されていたなら、第2のバッファ回路14を介してフォトカプラ16からCPUが動作できない場合の装置異常の出力信号を送出する。第2のバッファ回路14は、制御端子14aのリセット電圧で出力動作がロックされ、電源入り切り時における電圧変動では、第2のリセット信号発生回路12はリセット電圧を発生しない。このため、第2のバッファ回路14はロックされない。

(もっと読む)

リセットクロック制御回路

【課題】メタステーブル状態を発生させることなく、対象論理回路ブロックにおける非同期リセットを解除する。

【解決手段】シンクロナイザ10の非同期リセット入力端子に、対象論理回路100に対して任意の同期関係にある非同期リセット入力信号rst_nが入力され、D入力端子に、対象論理回路ブロック100に対して任意の同期関係にあるソフトウェアリセット信号srst_nが入力され、クロック入力端子に、クロック入力信号clkが入力されると、シンクロナイザ10は、対象論理回路100に非同期リセット信号resetを出力する。ゲーティングセル20は、クロックイネーブル端子に、シンクロナイザ10から出力された非同期リセット信号が入力され、クロック入力端子に、クロック入力信号clkが入力されると、対象論理回路100にクロック信号clockを出力する。

(もっと読む)

状態制御装置

【課題】 複数のボタンを設けることなく、ユーザ操作を煩雑にすることなく、CPUを強制的に電源オフ状態にし、かつ、マイコンをリセットすること。

【解決手段】 電源ボタンが第1所定時間継続して押下され続けると、マイコンがCPUを強制的に電源オフ状態に移行させる。電源ボタンが第2所定期間継続して操作され続けると、リセットICがマイコンをリセットさせる。従って、電源ボタンが継続して操作され続けることによって、まずはCPUを強制的に電源オフ状態にした後、マイコンをリセットすることができる。従って、ボタンを複数設ける必要がないのでコストを増加させることなく、ユーザ操作を煩雑にすることなく、CPUを強制的に電源オフ状態すること、及び、マイコンをリセットすることができる。

(もっと読む)

1 - 20 / 58

[ Back to top ]