Fターム[5B056AA05]の内容

Fターム[5B056AA05]に分類される特許

1 - 20 / 103

並列演算装置及びマイクロコンピュータ

【課題】並列的に入力されるデータに対処してヒストグラムの度数データを生成することができ、ヒストグラムの度数データを生成する処理時間をその入力データにおけるヒストグラム値の分布状況に依存せず、更にはヒストグラムの度数データを累積するために用いる記憶領域を少なくすることができる並列演算装置を提供する。

【解決手段】複数のプロセッサによる並列的な演算結果に対して、演算結果の種別毎にそのデータ数を並列的に計数する複数のカウンタを有し、夫々のカウンタの計数値を累積してヒストグラムの度数とするヒストグラムカウンタ回路を備える。

(もっと読む)

線形システム解法のためのアレイ処理

【課題】本発明は、線形システムを解くためのアレイ処理の方法を提供する。

【解決手段】線形システムを解くためにPE(54〜54N)を利用する。本発明の一実施形態(図3b)では、コレスキーファクタを判定するため、行列の対角要素がスカラーPEに射影される。別の実施形態では、コレスキーファクタを判定するため、2次元スカラーアレイが使用される。限られたバンド幅をもつ行列の場合、使用するプロセッサの数を減らした、プロセッサ(54〜54N)を用いることができる。

(もっと読む)

演算処理装置

【課題】ストライド命令の後続命令に対してもチェイニングを行って性能を向上することができる演算処理装置の提供を図る。

【解決手段】同時アクセス可能な複数のメモリブロックbank0〜bank3を有するデータメモリ2との間でデータを遣り取りする複数のベクトルパイプライン121〜124を有する演算処理装置であって、前記データメモリに対するストライドアクセスを、基本パターンのデータサイズを決める第1パラメータと、該基本パターンにおける有効なデータ数を決める第2パラメータで規定する。

(もっと読む)

ベクトル演算処理装置、ベクトル演算処理方法およびベクトル演算処理プログラム

【課題】キャッシュメモリと主記憶装置との間の負荷を軽減し、ロードバッファの解放タイミングを早める。

【解決手段】投機的に実行されるベクトルロード命令が発行された場合に、ベクトルデータのバッファ領域M2を確保するロードバッファ管理部31と、メモリアクセスリクエストに基づいて要素データをキャッシュメモリM1又は主記憶装置9から読み出し、読み出した要素データをバッファ領域M2に格納させるキャッシュ処理部4と、投機的実行に成功した場合にバッファ領域の要素データをベクトルレジスタM3に転送してからバッファ領域M2を解放し、一方、投機的実行に失敗した場合にバッファ領域M2の要素データをベクトルレジスタM3に転送せずにバッファ領域M2を解放するベクトル処理部6とを備え、キャッシュ処理部4は投機的実行に失敗した場合に要素データの主記憶装置9からの読み出しを抑止する。

(もっと読む)

ordering生成方法、プログラム及び共有メモリ型スカラ並列計算機

【課題】スパースな正値対称行列のコレスキーあるいは修正コレスキー分解を行う場合に、並列処理を高速化することができるorderingを生成する方法を提供する。

【解決手段】共有メモリ型並列計算機を用いてスパースな正値対称行列のコレスキー分解あるいは修正コレスキー分解を行うにあたり、スパース行列が表す連立1次方程式が提示する問題における離散化された空間を、再帰的に2つの分割領域と、その間にある分割面とに分割する。分割を、分割面を構成するノードの数がスーパーノードの幅程度となったら止める。そして、再帰的に2分割されるごとに、分割領域内のノードに、分割面から遠いほうから順に番号付けを行う。分割面内のノードは、再帰的2分割のたびに、分割領域の番号付けの後に番号付けを行う。

(もっと読む)

内積演算装置および内積演算方法

【課題】乗算器を使用しないハードウェア量の少ない演算器構成で、高並列に適したサイクルタイムの高速化が図れるとともに、ROMを用いなくても内積演算が効率よくかつ精度低下なく行うことができる内積演算装置および内積演算方法を提供する。

【解決手段】複数の入力ベクトル要素を格納する入力要素レジスタ2と、定数ベクトル要素の2のべき乗項と入力ベクトル要素との部分積を求めるバレルシフタ3と、部分積の累算を行う加減算器4と、加減算器の累算結果が格納されるアキュムレータ5と、アキュムレータ5に格納された累算途中の結果の切捨てを行うシフタ6と、定数ベクトル要素の最下位の2のべき乗項の同じ項にかかる全ての入力ベクトル要素の部分積の累算を行わせて順次高位の2のべき乗項にかかる部分積の累算を繰り返して最上位の2のべき乗項まで繰り返させる演算制御手段と、を備えている。

(もっと読む)

並列有限要素計算システム

【課題】CGCG法を発展させることで,より短時間で解が求まる並列有限要素計算システムを提供する。

【解決手段】解析対象領域Ωと,そのメッシュ分割を与える。並列プロセス数m0,階層数νおよび各階層の領域数νmνを入力する。並列プロセスにわたる第0階層領域分割を生成する。ν個の階層の領域分割を生成する。全ν階層の領域分割をもとに第1,…,ν世代コース空間W(1),…,W(ν)と,W(ν)の共役空間V(ν)を作る。全世代の2組の剛性行列と2組の外力ベクトルを作る。ν個のコース空間の方程式を直接法で解く。第ν世代の共役空間の方程式を反復法(前処理付きCG法)で解く。u=u(0)=w(1)+…+w(ν)+u(ν)によって解を与える。この方法は,最初に「領域分割」を全部与えておき直列に計算する方法である。領域分割を「共役空間」における反復法の収束の様子を見たうえで順次与え,つぎつぎと計算していく方法も本発明に含まれる。

(もっと読む)

情報処理装置

【課題】処理速度、或いは、プログラムの実行速度を向上させることができる情報処理装置の提供を図る。

【解決手段】ベクトルレジスタファイル(32)がベクトル長により物理番号と論理番号が変化する情報処理装置であって、ベクトル長を指定するベクトル長レジスタ31と、前記ベクトル長レジスタによるベクトル長の第1値VLと、ベクトル長を変化させる命令によるベクトル長の第2値VL’を比較する比較器21と、前記比較器からの比較結果に従って、実行中の先行命令に続く後続命令の発行可否を判定する発行可否判定回路22と、を有するように構成する。

(もっと読む)

ベクトル型計算機及びベクトル型計算機の命令制御方法

【課題】ベクトルギャザー命令やベクトルスキャッター命令に対して、動的な追い越し制御が行えるベクトル型計算機を提供する。

【解決手段】最小値最大値判定器21でベクトルギャザー命令又はベクトルスキャッター命令に対するアドレスの依存元命令を実行する固定小数点演算器12の演算結果を用いてベクトル要素の最小値及び最大値を判定する最小値最大値判定し、この最小値及び最大値を最小値/最大値レジスタ部31に保持しておく。ベクトルギャザー命令又は前記ベクトルスキャッター命令を実行する際に、保持されている最小値及び最大値から、前記ベクトルギャザー命令又は前記ベクトルスキャッター命令のアドレスのアクセス範囲を特定し、ベクトルギャザー命令又はベクトルスキャッター命令の追い越し制御を行う。

(もっと読む)

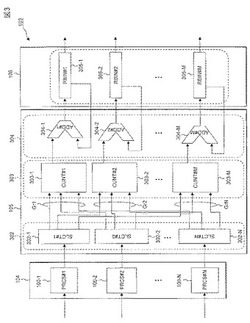

ベクトル処理装置及びベクトル演算処理方法

【課題】ベクトル処理装置内のベクトル演算パイプのデータ入出力を高速化すること

【解決手段】ベクトル演算処理装置内に、ベクトル演算処理を行う複数のベクトル演算パイプ210を設けた少なくとも1以上のベクトル処理ユニット200を備える。ベクトル処理ユニット200内であって、かつ、ベクトル演算パイプ210の外部に前記ベクトル演算パイプに対応する出力用のデータバッファ220、及び入力用のデータバッファ230を設ける。

(もっと読む)

球面調和関数変換を行う並列計算機システム、並列計算機システムの制御方法及び制御プログラム

【課題】球面調和関数変換の計算時間を短縮化することを目的とする。

【解決手段】球面調和関数を用いて行う球面のシミュレーションを行う並列計算機システムにおいて、スペクトル空間のデータを東西波数により複数個のデータに分割されたスペクトルデータを保持する記憶部と、分割された各スペクトルデータの逆ルジャンドル陪関数変換によるフーリエ係数データへの変換を、球面における緯度方向について、分割された計算領域について実行する演算部と、演算部により変換されたフーリエ係数データを、演算部による次の球面における緯度方向について、分割された計算領域の逆ルジャンドル陪関数変換が開始してから、他の計算ノードに通信経路を介して送信する通信部と、を含む、互いに通信経路を介して接続された複数の計算ノードを有する並列計算機システムが提供される。

(もっと読む)

行列をSIMDマルチコア・プロセッサ・アーキテクチャ上で転置するためのコンピュータ実装方法、コンピュータ可読ストレージ媒体及びシステム

【課題】配列データをSIMDマルチコア・プロセッサ・アーキテクチャ上で転置するためのシステム、方法及びコンピュータ可読ストレージ媒体を提供する。

【解決手段】SIMD形式の行列が受け取られる。この行列は、通常のデータ形式を有する行列MをSIMD変換したものから成る。この行列の各要素から行列Mの転置のSIMD変換の各要素へのマッピングが定義される。行列M及びこの定義されたマッピングに基づき、SIMD転置行列Tが生成される。行列Mの複数の列上で動作するように、行方向アルゴリズムが修正なしでSIMD転置行列Tに適用される。

(もっと読む)

乗累算演算を実行するための装置および方法

【課題】乗累算演算を実行するデータ処理装置及び方法を提供する。

【解決手段】該データ処理装置は、制御信号に応答して、入力データ要素において、データ処理演算を実行するデータ処理回路を含む。命令デコーダ回路は、入力オペランドとして、第1入力データ要素、第2入力データ要素及び述語値を指定する述語化された乗累算命令に応答して、データ処理回路を制御するように制御信号を生成し、第1入力データ要素および前記第2入力データ要素を乗算し、乗算データ要素を生成し、該述語値が第1の値を有する場合、該乗算データ要素を初期累算データ要素に加算して結果累算データ要素を生成し、該述語値が第2の値を有する場合、該初期累算データ要素から該乗算データ要素を減算して、該結果累算データ要素を生成することで、乗累算演算を実行する。本発明は、パフォーマンス、エネルギー消費及びコード密度を改善する。

(もっと読む)

マルチMACアーキテクチャにおける低電力FIRフィルタ

【課題】性能を犠牲にせずに低電力を実現するためのマルチMACアーキテクチャを提供する。

【解決手段】本発明の実施形態は、チェーンの第1の乗加算器の出力結果をチェーンの第2の後続乗加算器への入力として供給することによって、2つ以上の乗加算器ユニット(210、220、230、240)の乗加算器チェーンの演算をスケジュールして、比較的低いワット損を可能にするシステムおよび方法を対象とする。

(もっと読む)

ベクトル演算装置およびベクトル演算方法

【課題】処理性能の向上したベクトル演算装置を提供すること

【解決手段】ベクトル演算装置1は、複数個のベクトルデータを格納する複数のベクトルレジスタ110、および、ベクトルレジスタ110から出力されるベクトルデータに対し演算を行うベクトル演算器111を有するベクトルパイプ11と、イテレーション演算のk(k:1以上の整数)番目の演算を行うベクトルパイプ11からk+1番目の演算を行うベクトルパイプ11に演算結果を順次並列して供給するパス116と、複数のイテレーション演算を複数のベクトルパイプ11で並列して実行するよう命令発行管理を行う命令発行部102とを備える。

(もっと読む)

データマップ読み取り装置、データマップ読み取り方法

【課題】高速メモリを用いたMAP引きによる演算を高速に実行するデータマップ読み取り装置及びデータマップ読み取り方法を提供すること

【解決手段】検索用データ24を記憶する第1の記憶手段15と、第1の記憶手段15のアドレスに従い、検索用データ24を一様方向に読み出す読み出し手段23と、読み出し手段が読み出した、検索用データ24の複製を記憶する第2の記憶手段13と、第2の記憶手段13に複製された検索用データ24を被検索値xinに基づき検索する検索手段25が、検索用データを24インクリメントサーチするかデクリメントサーチするかによって、検索用データ24の複製を読み出す方向を、第1の記憶手段15のアドレスの降順方向又は昇順方向のいずれかに切り替える切り替え手段21と、を有することを特徴とするデータマップ読み取り装置100を提供する。

(もっと読む)

メディアデータ符号化用8点変換

一般に、8点離散コサイン変換(DCT)を実施する技術が記載される。8点離散コサイン変換(DCT)ハードウェアユニットを備える装置は、空間領域から周波数領域へメディアデータを変換するためにこれらの技術を実施する。8点DCTハードウェアユニットは、第1の関係に基づいて第1のスケール因子(μ)に関係している内部因子A、Bを備える偶数部を含む。8点DCTハードウェアユニットは、第2の関係に基づいて第2のスケール因子(η)に関係している第3、第4、第5及び第6の内部因子(G,D,E,Z)を備える奇数部を更に含む。第1の関係は、第1のスケール因子を第1及び第2の内部因子に関係付ける。第2の関係は、第2のスケール因子を第3の内部因子及び第4の内部因子ならびに前記第5内部因子及び第6の内部因子に関係付ける。  (もっと読む)

(もっと読む)

データ処理装置

【課題】複数の1次キャッシュ間におけるデータ転送を効率よく行なうことができるデータ処理装置を提供する。

【解決手段】本発明のデータ処理装置1は、複数の演算器11、21、32、41と、複数の1次キャッシュ12、22、32、42と、2次キャッシュ50と、順次連続的に接続された複数のバッファキャッシュ13、23、33、43とを備えている。第1段目のバッファキャッシュ13には2次キャッシュ50からデータが転送されており、複数のバッファキャッシュ13、23、33、43は、各バッファキャッシュ13、23、33、43のデータの一部を後段側に順次転送すると共に、各バッファキャッシュ13、23、33、43のデータの一部を各バッファキャッシュ13、23、33、43に対応する1次キャッシュ12、22、32、42に転送する。

(もっと読む)

シミュレーション・システム、方法及びプログラム

【課題】 マルチコアまたはマルチプロセッサ・システムにおいて、処理ループを投機的パイプライニングで高速化する際に、予測の誤差をシステム的に計算することによって、誤差の累積を減らすこと。

【解決手段】

マルチコアまたはマルチプロセッサ・システムの環境において、制御ブロックのループの個々の処理が、投機的パイプライニングの技法で、好適には個別のスレッドとして個別のコアまたはプロセッサに割り当てられる。この予測入力に基づく出力に対して、当該スレットの予測変数値を用いて、補正値が計算される。この補正値の計算は、予測変数値の一次微分係数の近似値としての勾配値として与えられる。シミュレーション・システムの場合一般的に、変数値は複数あるので、一次微分係数は、ヤコビ行列としてあらわされる。そこで、本発明では、その各々の成分が一次偏微分係数の近似値としての勾配値である行列をヤコビ行列と呼ぶことにする。すると、本発明において、補正値の計算は、このようにして定義されたヤコビ行列によって行なわれる。

(もっと読む)

電磁界解析装置

【課題】小型化することができ、処理時間を削減ができる電磁界解析装置を得る。

【解決手段】解析で用いる係数、電界値及び磁界値をそれぞれ保持するメモリ群4a〜4cと、メモリ群4a〜4cの読み出し及び書き込みのアドレスを制御するメモリ制御部3と、メモリ群4a〜4cから係数、電界値及び磁界値を同時に読み出し、読み出した係数、電界値及び磁界値をそれぞれ所定のタイミングで所定クロック分遅延させ、電界及び磁界の時間変化式をストリーム形式で算出して電界値及び磁界値を更新する時間変化式算出部2とを設け、メモリ制御部3及びメモリ群4a〜4cは、読み出し用及び書き込み用のアドレス線6a、6bによって接続され、メモリ群4a〜4c及び時間変化式算出部2は、読み出し用のデータ線7a〜7cによって接続されているとともに、書き込み用のデータ線8によって接続されている。

(もっと読む)

1 - 20 / 103

[ Back to top ]