Fターム[5B056BB82]の内容

Fターム[5B056BB82]に分類される特許

1 - 20 / 20

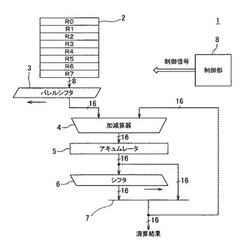

内積演算装置および内積演算方法

【課題】乗算器を使用しないハードウェア量の少ない演算器構成で、高並列に適したサイクルタイムの高速化が図れるとともに、ROMを用いなくても内積演算が効率よくかつ精度低下なく行うことができる内積演算装置および内積演算方法を提供する。

【解決手段】複数の入力ベクトル要素を格納する入力要素レジスタ2と、定数ベクトル要素の2のべき乗項と入力ベクトル要素との部分積を求めるバレルシフタ3と、部分積の累算を行う加減算器4と、加減算器の累算結果が格納されるアキュムレータ5と、アキュムレータ5に格納された累算途中の結果の切捨てを行うシフタ6と、定数ベクトル要素の最下位の2のべき乗項の同じ項にかかる全ての入力ベクトル要素の部分積の累算を行わせて順次高位の2のべき乗項にかかる部分積の累算を繰り返して最上位の2のべき乗項まで繰り返させる演算制御手段と、を備えている。

(もっと読む)

演算装置及び演算方法

【課題】 浮動小数点積和演算あるいは固定小数点乗算がそれぞれ実行される場合に、無効な電力消費が発生するという問題点がある。

【解決手段】 通知された演算命令に基づいて選択した入力データを構成する複数の部分データそれぞれについて最上位ビットから連続している0の数を計数して第1のリーディングゼロカウントとし、第1のリーディングゼロカウントに基づいて入力データについて最上位ビットから連続している0の数を計数して第2のリーディングゼロカウントを出力するリーディングゼロ手段と、第1のリーディングゼロカウントを入力して演算命令に基づいた演算を行うとともに、第2のリーディングゼロカウントを入力して演算命令に基づいた演算を行う第1の演算手段と、第1の演算手段及びリーディングゼロ手段と連携して演算命令に基づいた演算を行う第2の演算手段とを有する。

(もっと読む)

データ変換処理装置およびデータ変換処理方法

【課題】 画像データの符号化及び復号の両方に共通して使え、ロッシ−・ロスレス符号化復号半2重システムを低コストで実現する。

【解決手段】 N個の入力データを、N次元空間上で回転変換する装置であって、特定の1つのデータを除くN−1個のデータ毎に第1と第2の重み係数が定められており、前記特定の1つの入力データにN−1個の第1の重み係数を乗じた結果を、対応するN−1個の入力データに加減算する第1群リフティング演算部1010と、第2の重み係数を、第1群リフティング演算出力のN−1個のデータに乗じ、N−1個の乗算結果を前記特定の1つのデータに加減算する第2群リフティング演算部1020と、第1の重み係数を、第2群リフティング演算出力の特定の1つのデータに乗じ、N−1個の乗算結果を対応するN−1個のデータに加減算する第3群リフティング演算部1030を有する。

(もっと読む)

浮動小数点積和演算装置、浮動小数点積和演算方法、及び浮動小数点積和演算用プログラム

【課題】IEEE754R規格に準拠した浮動小数点積和演算を行う。

【解決手段】浮動小数点演算器において、浮動小数点乗算器と浮動小数点加算器を個別に有し、通常はそれぞれが独立で動作するが、浮動小数点積和命令時には、浮動小数点乗算器は、浮動小数点乗算の中間結果を浮動小数点加算器に受け渡し、浮動小数点加算器は、中間結果幅に対応した桁合わせシフト(左右シフト)と仮数部絶対値加算と正規化シフトを行い、浮動小数点加算を行う。

(もっと読む)

乗算器/アキュムレータ・ユニット

【課題】回路における消費電力、複雑さ及びスペースを低減し、かつ演算処理を高めた集積回路における乗算器/積算器(MAC)ユニット、更に同一の集積回路に前記MACユニットを二重に設けた二重MACユニットを提供する。

【解決手段】MACユニット(100)において、第1のバイナリ・オぺランドX(102)と第2のバイナリ・オぺランドY(104)との複数の部分積を発生するブース記録ロジック(120)と、低減した前記部分積を第3のオぺランドと算術的に組み合わせて最後の部分積を得るワラス・ツリー加算器(130)と、最後の和を発生する最後の加算器(140)と、前記最後の加算器を選択的に丸める即ち飽和させる飽和回路(150)とを備える。

(もっと読む)

時間ドメインから周波数ドメインへ及びそれとは逆にデジタル信号を変換する方法

【課題】整数型離散コサイン変換の丸め回数を少なくし、近似エラーを減少する。

【解決手段】順方向変換及び逆方向変換において、デジタル信号は、複数のブロックへとグループ分けされるデータ記号で構成され、各ブロックが所定数のデータ記号を含み、デジタル信号の2つのブロックを1つの変換エレメントにより変換するプロセスを備え、変換エレメントは、2つのサブマトリクスを含むブロック対角マトリクスに対応し、各サブマトリクスは、変換マトリクスを備え、且つ変換エレメントは、複数のリフトステージを備え、更に、各リフトステージは、補助的な変換及び丸めユニットによるデジタル信号のブロックの処理を含む。

(もっと読む)

データ変換装置及びその制御方法

【課題】少ない処理量で整数型ロスレスアダマール変換を実現する。

【解決手段】第1の演算器群1001は、変換対象のデータD0を、変換対象のデータD1乃至D3にそれぞれ加算する。シフタ106は、データD0を1ビット左シフトする。第2の演算器群1002は、第1の演算器群で算出された3つのデータを、シフタ106の出力データから減算する。シフタ107は、減算結果を1ビット右シフトすることで、第2の演算器群102による演算結果を、1/2にすると共に、その小数点以下を切り捨てる丸め処理を行なう。符号反転器108は、シフタ107の出力データの符号を反転し、DC変換係数データY0として出力する。第3の演算器群1003は、シフタ108の出力データを、第1の演算器群1001からの出力データから減じ、これらをAC変換係数データY1乃至Y3として出力する。

(もっと読む)

演算装置、逆数の近似計算プログラムおよび近似計算方法

【課題】逆数または平方根逆数の近似計算をニュートンラフソン法によって行う際、同程度の大きさの浮動小数点数の減算処理に伴ってプロセッサで生じるビットシフト処理に起因するストールを回避でき、計算速度を向上できる演算装置を提供する。

【解決手段】演算装置1は、初期近似精度を持つ初期近似逆数に対して近似計算を行う。まず、中間値演算部15が、ニュートンラフソン法の1段近似計算により、中間近似精度を持つ中間近似逆数を計算し、そして、目標値演算部17が、ニュートンラフソン法の多段近似計算によって目標精度まで精度を高める。中間近似精度は、プロセッサでの浮動小数点数の減算処理に伴う仮数部のビットシフトによるストールが生じない上限ビットシフト量に対応する非ストール誤差を残すように設定されている。この中間近似精度が得られるように、中間値演算部15では、故意に誤差を拡大した1段近似計算が行われる。

(もっと読む)

順方向および逆離散コサイン変換の効率的な固定小数点近似

固定小数点計算を使用して、逆離散コサイン変換の計算を近似する技術が説明されている。これらの技術によれば、スケーリングされた係数のマトリクスに、スケールファクタを乗算することによって生成される。次に、バイアスをかけられた係数のマトリクスは、スケーリングされた係数のマトリクスのDC係数に、中間バイアス値を加算することによって生成される。固定小数点算術演算は、そのあとで、バイアスをかけられた係数のマトリクスに対して変換を適用するために使用される。結果として生じるマトリクスにおける値は、そのあと、ピクセルコンポーネント値のマトリクスを導き出すために右シフトされる。ピクセルコンポーネント値のマトリクスは、そのあとで、ピクセルのマトリクスを作るために結合される。これらの技術によって生成されたピクセルのマトリクスは、理想的な逆離散コサイン変換(“IDCT”)を使用して、伸張されたピクセルのマトリクスに、非常に近似している。  (もっと読む)

(もっと読む)

逆離散コサイン変換計算における誤差低減

固定小数点を用いる離散コサイン変換の計算における丸め誤差を低減するための技術について説明する。これらの技術に従って、離散コサイン変換において、縮尺された係数の行列は係数の行列の係数に縮尺因数を乗算することにより、計算される。次に、中点バイアス値および補足バイアス値が縮尺された係数の行列のDC係数に加算される。次に、逆離散コサイン変換が求めた縮尺された係数の行列に適用される。次に、求めた行列中の値が画素成分値の行列を導出するために右シフトされる。ここに説明したように、補足バイアス値をDC係数へ加算することはこの右シフトに起因する丸め誤差を減少させる。その結果、これらの技術を用いて復元されたディジタルメディアファイルの最終版は、ディジタルメディアファイルの原版により良く類似しているかもしれない。

(もっと読む)

順方向および逆離散コサイン変換の効率的な固定小数点近似

固定小数点計算を使用して、逆離散コサイン変換の計算を近似する技術が説明されている。これらの技術によれば、スケーリングされた係数のマトリクスに、スケールファクタを乗算することによって生成される。次に、バイアスをかけられた係数のマトリクスは、スケーリングされた係数のマトリクスのDC係数に、中間バイアス値を加算することによって生成される。固定小数点算術演算は、そのあとで、バイアスをかけられた係数のマトリクスに対して変換を適用するために使用される。結果として生じるマトリクスにおける値は、そのあと、ピクセルコンポーネント値のマトリクスを導き出すために右シフトされる。ピクセルコンポーネント値のマトリクスは、そのあとで、ピクセルのマトリクスを作るために結合される。これらの技術によって生成されたピクセルのマトリクスは、理想的な逆離散コサイン変換(“IDCT”)を使用して、伸張されたピクセルのマトリクスに、非常に近似している。  (もっと読む)

(もっと読む)

逆離散コサイン変換の計算中の誤差の低減

固定小数点の計算を使用して離散コサイン変換の計算中に丸め誤差を低減させる技法が、説明される。これらの技法によれば、逆離散コサイン変換において、係数のベクトルは、固定小数点数に対して一連のバタフライ構造演算を使用して計算される。次に、中間バイアス値と、補足バイアス値とが、スケール変更された係数の行列のDC係数に対して加算される。次に、逆離散コサイン変換が、スケール変更された係数の、結果として生ずる行列に対して適用される。次いで、結果として生ずる行列の中の値は、ピクセル成分値の行列を導き出すために右シフトされる。ここにおいて説明されるように、DC係数に対する補足バイアス値の加算は、この右シフトに帰せられる丸め誤差を低減させる。結果として、これらの技法を使用して伸張されるデジタルメディアファイルの最終バージョンは、デジタルメディアファイルの元のバージョンに、より密接に類似することができる。  (もっと読む)

(もっと読む)

逆変換回路

【課題】 多様な仕様の逆変換アルゴリズムを実行することができる逆変換回路を得ることを目的とする。

【解決手段】 入力前処理部1から出力された列データd0〜d3と係数テーブル2から出力された行データcとの積和演算を実施する積和演算部3〜6を設け、可変丸め部7が積和演算部3〜6における演算結果の行要素毎に、別々の丸め処理を実施するようにする。これにより、定数項eを適宜設定することで、多様な仕様の逆変換アルゴリズムを実行することができるようになる。

(もっと読む)

ベクトル積和演算回路

【課題】 ベクトルレジスタの各要素の書換えを行うことなく、2つのオペランドの演算を容易に行うことが可能なベクトル積和演算回路を提供する。

【解決手段】 マスクレジスタ31〜33は各オペランド毎にデータの有効/無効を示すマスクビットを格納する。制御回路11〜13は演算モードと各オペランドに付随するマスクビットとから選択信号を生成する。機能セレクタ1〜3は各オペランドを入力とし、オペランドデータと予め設定された所定値(“0”または“1”)とのうちのいずれかを制御回路11〜13からの選択信号にしたがって選択し、積和演算回路の各回路に出力する。

(もっと読む)

演算装置および演算方法

【課題】 より正確な浮動小数点を用いた演算を行うこと。

【解決手段】 乗算対象である第1の数と第2の数との積の演算を、二進浮動小数点を用いて行う演算装置であって、前記第1の数、前記第2の数、および、演算によって発生した数を、所定の桁数より下位の桁のビットを切り捨てるかあるいは切り上げることによって所定の桁数内の数として記憶する記憶部と、前記記憶部に記憶された前記第1の数を1のビットの最上位桁と最下位桁が分かれるように2つ以上の数に分離し、前記分離したそれぞれの数と前記第2の数の積の演算を行い、それぞれの当該演算結果を別々に前記記憶部に記憶させる処理部と、を有することを特徴とする。

(もっと読む)

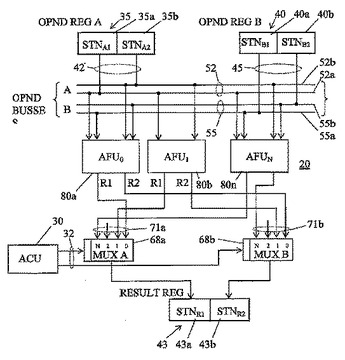

モーダル区間プロセッサ

論理回路は、複数の算術関数ユニット(20)を使用して様々なモーダル区間計算値を算出する。マルチプレクサ(68)は、所望の計算値を記憶レジスタ(43)にゲート制御によって出力する。  (もっと読む)

(もっと読む)

データ変換装置およびその方法

【課題】 1回の丸め処理のみによる16点ロスレスアダマール変換を実現する。

【解決手段】 16個のデータにアダマール変換行列を乗算して16個の線形アダマール変換係数を得る線形変換工程と、前記16個の線形アダマール変換係数を、各々が奇数個となるよう4種類のグループに分類し、該グループ毎に所定のオフセット値を加算するオフセット工程と、前記オフセット値の加算後に小数点以下を切り捨てて前記ロスレスアダマール変換係数を得る整数化工程と、を有する。

(もっと読む)

少なくとも2つの入力値を処理するための装置および方法

丸め誤差の減少のために、第1および第2の非整数の入力値は、丸められ第3の入力値に加算される(269)非整数の結果値を得るために非整数の状態で、例えば加算によって、提供され(260、262)、組み合わされる(268)。したがって、丸め誤差は、リフティングステップに分割された2つの回転間、または、リフティングステップに分割された第1回転およびそれに続く多次元リフティングの連なりの第1のリフティングステップ間のインターフェイスで減少させることができる。 (もっと読む)

時間ドメインから周波数ドメインへ及びそれとは逆にデジタル信号のドメイン変換を実行する方法

時間ドメインから周波数ドメインへ及びそれとは逆にデジタル信号のドメイン変換を実行する方法において、複数のリフトステージを含む変換エレメントにより変換を実行するステップを備え、前記変換は変換マトリクスに対応し、複数のリフトステージのうちの少なくとも1つのリフトステージは、少なくとも1つの補助的な変換マトリクスと、丸めユニットとを備え、この補助的な変換マトリクスは、前記変換マトリクスそれ自体で構成されるか、又は低い次元の対応変換マトリクスで構成される。この方法は、更に、前記補助的な変換マトリクスによる変換の後に前記丸めユニットにより信号の丸め演算を実行するステップも備えている。 (もっと読む)

時間ドメインから周波数ドメインへ及びそれとは逆にデジタル信号を変換する方法

変換マトリクスを含む変換関数を使用して時間ドメインから周波数ドメインへ及びそれとは逆にデジタル信号を変換する方法であって、デジタル信号は、複数のブロックへとグループ分けされるデータ記号で構成され、各ブロックが所定数のデータ記号を含むような方法。この方法は、デジタル信号の2つのブロックを1つの変換エレメントにより変換するプロセスを備え、変換エレメントは、2つのサブマトリクスを含むブロック対角マトリクスに対応し、各サブマトリクスは、変換マトリクスを備え、且つ変換エレメントは、複数のリフトステージを備え、更に、各リフトステージは、補助的な変換及び丸めユニットによるデジタル信号のブロックの処理を含む。 (もっと読む)

1 - 20 / 20

[ Back to top ]