Fターム[5B060AC13]の内容

Fターム[5B060AC13]に分類される特許

1 - 20 / 121

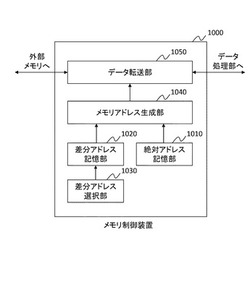

メモリ制御装置、メモリ制御方法、データ処理装置、画像処理システム

【課題】回路規模を抑えつつデータ整列が完了した状態で外部メモリから内部メモリにデータを転送する方法が求められていた。

【解決手段】本発明のメモリ制御装置は、外部メモリから複数の処理機構を備えるデータ処理手段にデータを転送するメモリ制御装置であって、所定のデータ転送期間において共通の基準値となる絶対アドレスを記憶する絶対アドレス記憶手段と、複数の差分アドレスを記憶する差分アドレス記憶手段と、複数の差分アドレスを所定の順序で選択する差分アドレス選択手段と、差分アドレス選択手段が選択した差分アドレスと絶対アドレスとを組み合わせてメモリアドレスを生成するメモリアドレス生成手段と、メモリアドレス生成手段で生成されるメモリアドレスを外部メモリに入力し、メモリアドレスからデータを読み出してデータ処理手段にデータを転送するデータ転送手段と、を具備する。

(もっと読む)

メモリコントローラ

【課題】プロセッサにて処理されるデータが格納されるメモリの容量を削減する。

【解決手段】メモリコントローラ2は、メモリ領域RBのアドレスBnに書き込みデータYを書き込むようにプロセッサ1からの書き込み要求を受け取ると、メモリ領域RAのアドレスAmから読み出すようにプロセッサ1から指示された読み出しデータXと、メモリ領域RBのアドレスBnに書き込むようにプロセッサ1から指示された書き込みデータYが一致するかを判定し、それらの読み出しデータXと書き込みデータYが一致する場合、書き込みデータYをメモリ領域RBのアドレスBnに書き込まないようにする。

(もっと読む)

データ転送制御装置及びデータ転送方法

【課題】メモリに対して複数のアクセス手段からのアクセスが同時に行われる場合に、メモリへのアクセス効率を向上する。

【解決手段】データ転送制御装置は、データを格納するメモリと、同じアドレス順で前記メモリにアクセスする複数のアクセス部とを備える。データ転送制御装置は、複数のアクセス部による前記メモリのアクセスアドレスの差を検出し、検出されるアクセスアドレスの差を小さくするために、複数のアクセス部のうちのアクセスアドレスが先行しているアクセス部の前記メモリへのアクセスの実行頻度を減少させる。

(もっと読む)

情報絞り込み検出機能を備えたメモリ、その使用方法、このメモリを含む装置。

【課題】

パターン認識など情報検出の最大の課題は検索時間でありメモリの逐次比較処理が不要な非ノイマン型情報検出メモリを実現する。

【解決方法】

メモリアドレスごとに情報を記憶しその情報を読み出し可能なメモリで、このメモリは、外部から与えられる第1のデータは記憶されたメモリのデータを比較するためのデータ、第2のデータはアドレス同士を比較するためのデータ、の双方の入力データの入力手段と、この入力手段から与えられた上記双方の入力データにより記憶された情報のデータと、そのアドレスと、の双方を二重並列に合否判定し、その双方の合否判定結果をさらに並列に論理演算する手段と、上記論理演算に合格するこのメモリの上記アドレスを出力する手段と、を具備することを特徴とする情報絞り込み検出機能を備えたメモリであるのでインテリジェンスな情報検索はもとより人工知能等に広く利用可能である。

(もっと読む)

画像処理装置、画像処理方法、及びプログラム

【課題】キャッシュ技術を用いて画像変形処理を行う際に、処理速度を向上させる。

【解決手段】入力画像を入力する。入力画像をブロック単位で格納する。領域を出力画像内に設定し、設定した領域内のそれぞれの画素について、画素に対応する入力画像内の画素を含むブロックを特定した場合に、特定されたブロックのデータ量の合計がキャッシュメモリの容量以下となるように、部分領域の大きさを決定する。出力画像の画像領域を複数の部分領域に分割する。複数の部分領域のそれぞれについて順に部分画像を生成する。部分画像で構成される出力画像を出力する。

(もっと読む)

サーバ装置、メモリ管理方法及びメモリ管理プログラム

【課題】メモリを効率的に使用する。

【解決手段】サーバ装置3は、クライアント2が取得するデータの種類ごとにデータの実行履歴から算出したデータ量を表す使用メモリ量情報3bから、クライアント2からの要求に応じて実行するデータの種類に対応するデータ量を特定し、特定したデータ量をメモリ3aに割り当てるようにした。このため、メモリ3aの容量に対してデータ量を効率的に割り当てることが可能となる。したがって、1台のサーバ装置3に対して接続できるクライアント2の台数を増加させることが可能となり、サーバ装置3の増設を防ぎ、サーバ装置3の導入コストを抑制することができる。

(もっと読む)

画像処理装置

【課題】フレームバッファへの書込みと読出しが並列に行われる画像処理装置において、フレーム間で読出開始位置が異なっても、画像処理後のフレームの出力レートを一定に保つ。

【解決手段】書込部120はフレーム毎に該フレームに含まれる複数の画像データを所定の順序でフレームバッファ130に書き込む。読出部140は、フレーム毎に、第1の順位から第2の順位までに書込部120が書き込んだ複数の画像データを読み出す。第1の順位は、画像処理部150が当該フレームに対して行う画像処理によって異なりうる。読出部140は、各フレームに対して、該フレームの先頭の画像データの書込みの開始から所定の時間が経過した時点で読出しを開始する。この所定の時間は、フレームの先頭の画素の書込みの開始から、最も後の第1の順位に対応する画素のデータの書込みの完了まで以上の時間である。

(もっと読む)

コンピュータのメモリ使用についての情報を提供するシステム及び方法

【課題】コンピュータのメモリ使用に関する情報を提供する。

【解決手段】ディスプレイユニットに接続されるクライアントユニット8を有する呼出コンピュータ2、駆動システムコア4、駆動システムコアユニット5、カップリングユニット6、及び中継ユニット7を有する被呼出コンピュータ1、及び少なくとも1つの呼出コンピュータと少なくとも1つの被呼出コンピュータとを接続する通信チャネルとを備え、カップリングユニットは、駆動システムコアに統合される駆動システムコアユニットと、少なくとも1つの被呼出コンピュータに統合される中継ユニットとに接続され、中継ユニットと駆動システムコアユニットとの間で中間のデータ転送装置としての役割を果たし、駆動システムコアユニットへのアクセスを確立し、中継ユニットから駆動システムコアユニットにデータを転送し、駆動システムコアユニットから中継ユニットにデータを伝送する。

(もっと読む)

印刷装置

【課題】印刷装置において、メモリの空き領域の断片化による画像データの書き込み待ちを解消する。

【解決手段】印刷すべき複数の画像データをメモリ34に配置し、該配置された複数の画像データを順次読み出して印刷を実行する印刷装置において、メモリ34における複数の画像データDk,Dl、Dmの配置領域の間に空き領域V2が存在する場合、メモリ34に配置されている全ての画像データDk,Dl、Dmがメモリ34中で連続的に配置されるように、複数の画像データDk,Dl、Dmのうち少なくとも1つの画像データの配置位置を変更するメモリ管理手段を備える。

(もっと読む)

半導体記憶装置の制御プログラム、半導体記憶媒体制御装置、半導体記憶媒体の制御方法及び画像形成装置

【課題】画像形成装置に不揮発性の半導体記憶装置を搭載する場合において、ウェアレベリングの処理を効率化する。

【解決手段】画像形成装置における画像形成出力においてNANDフラッシュメモリへの情報の書き込み命令を取得し、情報を書き込むべき記憶領域が、描画情報を一次的に記憶するための一次記憶領域であるか、それ以外の通常記憶領域であるか判断し、一次記憶領域である場合に、情報の書き込み先として一次記憶領域に含まれる全領域を先頭から順番に選択し、次の画像形成出力において再度前記一次記憶領域に情報を書き込む際、前回の画像形成出力において情報が書き込まれた領域の次の領域を選択する。

(もっと読む)

データ転送装置、その制御方法、および制御プログラム

【課題】DRAMなどのメモリに複数種類のデータを転送して格納する際、プリチャージの回数を抑えてデータを効率よく転送する。

【解決手段】データ転送制御装置310は、互いに異なる複数種類のデータをDRAM320に転送する。DRAMには複数のページが規定されており、データ転送制御装置は複数種類のデータについて所定のデータ量を1つの単位として、当該1つの単位毎に前記複数種類のデータをページの1つに転送する。この際、CPU205は複数種類のデータについて所定のデータ量を設定する。

(もっと読む)

メモリ制御方法、メモリ制御装置、および画像形成装置

【課題】シリアル−パラレル変換とパラレル−シリアル変換を効率的に実行する。

【解決手段】画像処理前のラインデータを記憶するラインメモリと画像処理後のラインデータを記憶するラインメモリとを同一素子で構成し、シリアルデータ形式で入力されるラインデータをラインメモリで記憶する処理前・メモリ入力タイミング,記憶された処理前のラインデータをパラレルデータ形式で読み出す処理前・メモリ出力タイミング,処理後のパラレルデータ形式のラインデータをラインメモリで記憶する処理後・メモリ入力タイミング,記憶された処理後のラインデータをシリアルデータ形式で読み出す処理後・メモリ出力タイミング,の4タイミングで制御し、同一ライン周期内に処理前・メモリ出力タイミングの直後に処理後・メモリ入力タイミングを実行すると共に、同一ライン周期内に処理後・メモリ出力タイミングの直後に処理前・メモリ入力タイミングを実行する。

(もっと読む)

画像形成装置

【課題】ユーザの利便性の低下及びメモリの無駄が生ずることなく、待機時の消費電力を効果的に削減することができる画像形成装置を提供する。

【解決手段】本発明の画像形成装置は、複数のDRAM21a〜21hと、DRAM21a〜21hの管理を行うCPU11と、DRAM21a〜21hを予め定められた単位の区分D1〜D4に区分し、CPU11によるDRAM21a〜21hの管理状況に応じて、DRAM21a〜21hに対する電力の供給及び停止を区分D1〜D4毎に制御する電源制御部23とを備える。

(もっと読む)

ユーザ応答時間を考慮したメモリ管理装置及び方法

【課題】 ユーザ応答時間を考慮したメモリ管理装置及び方法を提供する。

【解決手段】 システムの性能を考慮して早いユーザ待機時間を与えることができるメモリ管理装置は、メモリを割り当てるメモリ割り当て部と、システムの性能またはユーザ応答時間を考慮して、割り当てられたメモリの解除に関する解除単位を獲得する解除単位算出部と、獲得された解除単位に基づいて割り当てられたメモリを解除するメモリ解除部と、を含む。

(もっと読む)

画像処理装置のメモリ管理方法、プログラム及び画像処理装置

【課題】メモリの空き領域の断片化を抑止する。

【解決手段】画像形成装置で用いられるメモリ管理方法は、RAM12がDL、FB及び圧縮データを記憶する工程と、CPUが、RAM12に記憶されたデータの削除順序をメモリ管理テーブルによって管理し、RAM12の空き領域の断片化解消処理を行うときにRAM12に記憶されたDL、FB及び圧縮データを各データの削除順序に基づいて連続する領域に配置するように並べ替える工程と、を有する。

(もっと読む)

メモリシステム

【課題】 リフレッシュ動作が必要なDRAMを備えたメモリシステムにおいて、必要なリフレッシュ動作を行いながらもデータ転送効率を向上させる。

【解決手段】 リフレッシュ制御回路16は、ラインメモリ12からフレームメモリ14に対する対象データのデータ転送開始時におけるアドレスポインタ21のポインタ値である基準ポインタ値に基づいて設定された判定基準値を保持する基準値保持部23と、所定のタイミングでアドレスポインタ21のポインタ値と判定基準値を比較し、前者が後者を下回っていればフレームメモリ14に対してリフレッシュ動作の制御信号の送信を許可し、前者が後者以上であれば前記制御信号の送信を不許可とするリフレッシュ実行決定部24を備える。

(もっと読む)

メモリコントローラ、撮像装置

【課題】広帯域メモリアクセス要求に対するインターリーブアクセスと狭帯域メモリアクセス要求に対する非インターリーブアクセスを動的に切り替える。

【解決手段】インターリーブアクセス手段7aと非インターリーブアクセス手段7bを備えたメモリコントローラ10であって、ページ単位でアドレスを変換する記憶管理手段13をさらに有し、前記記憶管理手段13は、ページ毎にインターリーブアクセスと、非インターリーブアクセスを切り替える、ことを特徴とする。

(もっと読む)

メモリ管理装置

【課題】不揮発性半導体メモリの寿命を延ばす。

【解決手段】本発明の一態様に係るメモリ管理装置1は、第1の半導体メモリと、第1の半導体メモリよりもアクセス可能上限回数の小さい不揮発性の第2の半導体メモリとのうちの少なくとも一方に記憶される各データの特性に基づいて生成され、当該各データの配置領域を決定するヒントとなる配置ヒント情報14を管理する。メモリ管理装置1は、配置ヒント情報14とメモリ使用情報11とメモリ固有情報12とに基づいて、書き込み対象データに対して第1の半導体メモリと第2の半導体メモリとのメモリ領域の中から、書き込み領域を決定する管理部15を具備する。配置ヒント情報14の生成は、オペレーティングシステムによって行われる。

(もっと読む)

メモリ管理装置

【課題】書き込み回数、読み出し回数、消去回数のうちの少なくとも一つに上限のある不揮発性半導体メモリを効率的に使用する。

【解決手段】本発明の一例のメモリ管理装置1は、外部から接続された不揮発性半導体メモリ32aの所定領域毎の消去回数を含むメモリ使用情報11を管理するメモリ使用情報管理部22と、メモリ使用情報11に基づき、不揮発性半導体メモリ32aの消去回数が、当該不揮発性半導体メモリ32aの消去可能上限回数に達する前に、不揮発性半導体メモリ32aに警告を通知する通知部35とを具備する。

(もっと読む)

メモリアクセスシステムおよびメモリアクセス制御方法

【課題】アクセス効率の高いメモリアクセスシステムを提供することである。

【解決手段】本発明にかかるメモリアクセスシステムは、第1乃至第4のメモリ10、20、30、40と、メモリコントローラ1とを備える。メモリコントローラ1は、第1のチップセレクト信号(CS0)を活性化する第1のタイミングにおいて、互いに異なる第1および第2の固有アドレス(ADA、ADB)を供給することで、第1および第2のメモリ10、20に格納された第1のブロック群のブロックにアクセスする。また、第2のチップセレクト信号(CS1)を活性化する第2のタイミングにおいて、互いに異なる第1および第2の固有アドレス(ADA、ADB)を供給することで、第3および第4のメモリ30、40に格納された第2のブロック群のブロックにアクセスする。

(もっと読む)

1 - 20 / 121

[ Back to top ]