Fターム[5B060HA02]の内容

Fターム[5B060HA02]に分類される特許

1 - 10 / 10

メモリシステム

【課題】不良メモリチップが発生した場合でも、並列駆動可能な組み合わせ数を最大限確保可能なメモリシステムを提供すること。

【解決手段】物理バンク内の不良メモリチップが識別可能な不良メモリチップ情報に基づき、不良メモリチップを使用せずに各レーン内において並列アクセス可能なメモリチップ数が最大となるように、論理バンクを構成する複数の物理バンクの組み合わせを動的に設定する。

(もっと読む)

フラッシュメモリ用インターリーブポリシー

【課題】読出しインターリーブポリシーの選択と、書込みインターリーブポリシーの選択とを独立して行う製品ならびに関連する方法およびシステムを提供する。

【解決手段】インターリーブされたメモリを使用してデータを処理するためのシステムであって、電源と、前記電源と接続されて動作可能な複数のメモリ素子と、前記複数のメモリ素子へのアクセスのインターリーブ比を選択的に制御するメモリコントローラと、命令を受け取るプロセッサとを備え、該命令は、前記プロセッサに前記メモリコントローラに対して前記インターリーブ比を特定させる処理を実施させ、前記処理が、前記メモリ素子に対するアクセス要求を受け取り、受け取られた前記アクセス要求を処理するための前記電源から前記メモリに引き出されるピーク電流を、前記アクセス要求を実施すべきインターリーブ比を選択することによって制御する。

(もっと読む)

メモリシステム

【課題】ホストからの指示に応じて消費電力の上限を抑制可能なメモリシステムを提供する。

【解決手段】並列動作可能な複数のバンクを有する不揮発性半導体メモリと、ホストからの電源管理コマンドを受信すると、受信した電源管理コマンドを解析するコマンド解析部と、このコマンド解析部の解析結果に応じて書き込みの際に並列動作させるバンクの上限数を動的に可変制御する記録制御部とを備える。

(もっと読む)

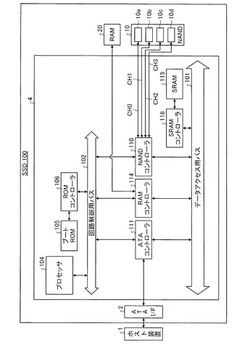

不揮発性記憶装置

【課題】高速アクセスあるいは省電力などの様々な要求(使用用途)に適応できる不揮発性記憶装置あるいはメモリコントローラを提供する。具体的には、フラッシュメモリの同時アクセス数(バンク数)を適応的に変更可能な不揮発性記憶装置を実現すること。

【解決手段】メモリコントローラ113内部に切替レジスタ105を設け、アクセス装置100が当該レジスタを書き換えることによって不揮発性メモリ114の同時アクセス数を変更する。あるいは、不揮発性メモリ114内部に切替レジスタ105を設け、アクセス装置100の指示に応じてメモリコントローラ113が当該レジスタを書き換えることによって不揮発性メモリ114の同時アクセス数を変更してもよい。また、予め不揮発性記憶装置115内の不揮発性記憶デバイス(ROM104等)に記憶しておき、起動時にこれを読み出して切替レジスタ105に設定するようにしてもよい。

(もっと読む)

メモリコントローラおよびフラッシュメモリシステム

【課題】2プレーン書き込み機能を効率的に利用することができるメモリコントローラを提供する。

【解決手段】データの書き込み先の空きブロックを検索するときに、ペアブロックの空きだけを検索する空きブロック検索テーブル100を用いた検索を最初に行い、この空きブロック検索テーブル100を用いた検索でペアブロックの空きが検出されなかった場合にだけ、片割れ良品ブロックの空きを検索する。ペアブロックの空きがあるときには、2プレーン書き込みを行い、ペアブロックの空きがなかった場合は、適宜組み合わせた片割れ良品ブロックにデータを書き込む。

(もっと読む)

フラッシュメモリ用インターリーブポリシー

【課題】読出しインターリーブポリシーの選択と、書込みインターリーブポリシーの選択とを独立して行う製品ならびに関連する方法およびシステムを提供する。

【解決手段】様々な実施形態では、動作中の選択は、静的であることも動的であることもある。読出しインターリーブポリシーおよび書込みインターリーブポリシーを動的に選択する諸実施形態では、選択は、温度、電源、バッテリ電圧、動作モードなど様々な動作状態に基づく可能性がある。動作モードの例としては、(1)外部電源に接続されたときにフラッシュメモリの読出しまたは書込みを行うもの、(2)携帯型電源(例えば、バッテリ)から給電されたときにフラッシュメモリの読出しを行うもの、および(3)携帯型電源から給電されたときにフラッシュメモリへの書込みを行うものを挙げることができる。

(もっと読む)

情報処理装置、情報処理方法、および、プログラム

【課題】全メモリに対するアクセスのインタリーブ数を2の乗数にすることで、メモリ構成に依存しないインタリーブを実施する。

【解決手段】WAY数S10a、S11a、S20a、S21a〜S80a、S81a、および、セグメント数S10b、S11b、S20b、S21b〜S80b、S81b、であるセグメント情報を保持するセグメント情報保持回路S10、S11、S20、S21〜S80、S81と、下限アドレスB10、B11、B20、B21〜B80、B81と、上限アドレスT10、T11、T20、T21〜T80、T81とを有し、メモリ構成上一部のメモリ空間のインタリーブ数が2の乗数を満たさない場合、任意のメモリの下限アドレスを底上げすることで、該当する単位メモリへのアクセスを2の乗数でインタリーブする。

(もっと読む)

バンクメモリを動的に管理する方法及び装置

【解決手段】複数のメモリバンクの一部を、キャッシュメモリとして、制御可能に割り当てる技術が示される。この目的のために、コンフィギュレーショントラッカ及びバンクセレクタが適用される。コンフィギュレーショントラッカは、各メモリバンクがキャッシュ内で動作すべきか否かを設定する。バンクセレクタは、複数のバンク分散機能を有している。到来アドレスを受け取ると、バンクセレクタは、キャッシュとして現在動作しているメモリバンクの設定を決定し、メモリバンクの設定に基づいて、適切なバンク分散機能を適用する。適用されたバンク分散機能は、キャッシュに内に設定されたバンクのうちの1つにアクセスするために、到来アドレスのビットを利用する。 (もっと読む)

記憶装置

【課題】

データ書込処理速度やデータ読出処理速度を適宜変化させることができるようにする。

【解決手段】

この半導体記憶装置1のコントローラ3は、設定装置11からグレードを指定するためのグレード指定信号を受信すると、当該受信したグレード指定信号により指定されたグレードに対応する個数のフラッシュメモリチップCPに対してデータ書込処理及びデータ読出処理を並列的に実行し得るように論理ブロック割当処理を実行するようにした。

(もっと読む)

データ構造の選択的複製方法および装置

低遅延メモリ118におけるデータ構造体を選択的に複製する方法および装置を提供する。このメモリ118は、同一データ構造体の複製コピーを格納するように構成される複数の個別のメモリバンク432を有する。格納されたデータ構造体へのアクセス要求を受信すると、低遅延メモリ118のアクセスコントローラ160はメモリバンクのうちの1つを選択し、次に、選択されたメモリバンクから格納データにアクセスする。メモリバンクの選択は、それぞれのメモリバンクの相対的有効性を比較するサーモメータ技術を用いて達成できる。最終的な効率を得られる例示的なデータ構造体には、決定性有限オートマトン(DFA)グラフ、および格納されるよりも高頻度でロードされる他のデータ構造体が含まれる。 (もっと読む)

1 - 10 / 10

[ Back to top ]