Fターム[5B060MB01]の内容

Fターム[5B060MB01]の下位に属するFターム

同一種別の複数のバス (72)

異なる性質/バス幅/種別のバス (39)

Fターム[5B060MB01]に分類される特許

1 - 20 / 44

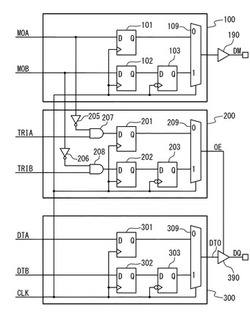

メモリ制御装置

【課題】メモリ書き込み時の消費電力を削減できるメモリ制御装置を提供する。

【解決手段】メモリ制御装置は、データバスを介してメモリ装置にデータをバースト転送するデータ出力バッファ回路390と、データのうちのメモリ装置内のメモリセルへの書き込みを禁止するデータを示すマスク信号をメモリ装置に出力するマスク信号出力バッファ回路190とを具備し、データ出力バッファ回路390は、マスク信号が書き込み禁止を示すときに出力ノードをハイインピーダンスにする。

(もっと読む)

メモリ制御装置

【課題】メモリ制御装置を提供する。

【解決手段】一次コントローラ及び二次コントローラがフラッシュメモリをアクセスするように制御するメモリ制御装置である。バススイッチは、第1、第2及び第3のシリアル周辺機器インタフェースバスそれぞれを介して、一次コントローラ、二次コントローラ及びフラッシュメモリに接続される。選択ユニットは、第3のシリアル周辺機器インタフェースバスを第1のシリアル周辺機器インタフェースバス及び第2のシリアル周辺機器インタフェースバスのうちいずれか一方に選択的に接続させる。選択ユニットは、バススイッチが第1のシリアル周辺機器インタフェースバスを介して一次コントローラからの第1のアクセス要求を受信した場合に、第3のシリアル周辺機器インタフェースバスを第1のシリアル周辺機器インタフェースバスに接続させる。

(もっと読む)

構成可能な入出力ポートを伴うメモリモジュール

【課題】メモリモジュールの入出力ポートの入力/出力の構成を変更可能とする。

【解決手段】メモリモジュール320は、1つ以上のメモリデバイスと、1つ以上のメモリデバイスと通信するコントローラ330と、複数の入出力ポート350とを有する。複数のコントローラ310の一つは入出力ポートのそれぞれを構成するようにコントローラ330に指示する。コントローラ330は、各入出力ポート350を、入力、出力、または双方向入出力として構成する。

(もっと読む)

不揮発性メモリのデイジーチェイン配置

【課題】組み込みフラッシュメモリおよび他のデバイスに関連した短所のいくつかを克服するメモリシステムを提供する。

【解決手段】フラッシュメモリシステムは、システム・イン・パッケージ(SIP)容器310の中に実装されている。前記システムは、フラッシュメモリコントローラ320と複数のフラッシュメモリデバイス330a〜330nとを有する。単一パッケージまたはモジュールに適用されるSIPは、多数の集積回路(チップ)を有する。フラッシュメモリコントローラは、SIP内の複数のメモリデバイスと外部システムとをインタフェースするように構成されている。メモリデバイスは、デイジーチェインカスケード接続に構成されており、前記デイジーチェインカスケードを通じて転送されたコマンドを介してフラッシュメモリコントローラに制御される。

(もっと読む)

情報処理装置、データバス設定方法、およびプログラム

【課題】装置を小型化でき、かつ、複数のメモリデバイスのいずれにもアクセス可能な情報処理装置を提供する。

【解決手段】複数の記憶手段と、複数の記憶手段に対して情報の入出力を制御する制御手段と、情報を制御手段と送受信するために複数の記憶手段毎に制御手段と接続された第1の信号線と、情報を制御手段と送受信するために複数の記憶手段で共用され、制御手段の接続先を変更可能な第2の信号線と、制御手段からの指示に基づいて、複数の記憶手段のうち、いずれか1つの記憶手段に第2の信号線を接続させる切り替え手段と、を有する。

(もっと読む)

半導体集積回路

【課題】内部プロセッサ、メインメモリ用のメモリI/F、外部プロセッサを有するデバイス用の外部I/F、及びレジスタを備えた半導体集積回路において、内部プロセッサからレジスタ制御を行った場合と外部プロセッサからレジスタ制御を行った場合との応答性能差異を少なくすると共に、外部プロセッサからメインメモリへのアクセス制御を行う場合の応答性能を向上させる。

【解決手段】半導体集積回路(SoC1cで例示)は、プロセッサ11及びメモリコントローラ15がバス接続された第1の内部バス(バス10で例示)とレジスタ31がバス接続された第2の内部バス(バス30で例示)とを含む複数の内部バスを備える。外部I/F16は、第1の内部バスと第2の内部バスとの間に多重バス接続され、メインメモリにメモリコントローラ15を介してアクセスする場合とレジスタ31にアクセスする場合とで、利用する内部バスを切り替える。

(もっと読む)

独立リンクおよびバンク選択

【課題】複数のメモリバンクと複数のリンク制御部とを備えるメモリシステムを提供する。

【解決手段】メモリバンクごとに、リンク制御部ごとの出力を受け取り、そのリンク制御部のうちの1つだけの出力をメモリバンクに伝えるための第1のスイッチングロジックがある。リンク制御部ごとに、各メモリバンクの出力を受け取り、そのメモリバンクのうちの1つだけの出力をリンク制御部に伝えるための第2のスイッチングロジックがある。本発明の一部の実施形態によれば、複数のリンク制御部による同じメモリバンクへの同時の、または重複するアクセスを防ぎ、同じリンク制御部による複数のバンクへの同時の、または重複するアクセスを防ぐために、第1のスイッチングロジックおよび第2のスイッチングロジックの両方の動作を制御するためのスイッチ制御部ロジックがある。

(もっと読む)

メモリシステム

【課題】

実施形態は、消費電流を低減可能なメモリシステムを提供する。

【解決手段】

本実施形態のメモリシステムは、前記NAND型フラッシュメモリと前記入出力部との間、および前記NAND型フラッシュメモリと前記入出力バッファ部との間に設けられた複数のデータバスと、入力される選択信号に基づいて、所望の前記データバスを選択するスイッチと、前記NAND型フラッシュメモリ、前記入出力部、及び前記スイッチを制御して、少なくとも前記入出力バッファ部から前記NAND型フラッシュメモリにデータを書き込むとき、選択された前記データバスを介して、前記NAND型フラッシュメモリと前記入出力バッファ部との間を接続し、残りのデータバスを介して、前記NAND型フラッシュメモリと前記入出力バッファ部との間を接続しない前記選択信号を前記スイッチに出力する制御部とを含む。

(もっと読む)

アイソレーションメモリバッファを組み込んだロードリデュースド・デュアル・インライン・メモリ・モジュール(LR−DIMM)を利用したスイッチ/ネットワークアダプタ・ポートインターフェースを含むヘテロジニアスコンピューティングシステム

【課題】アイソレーションメモリバッファを組み込んだLR−DIMMを利用したスイッチ/ネットワークアダプタ・ポートインターフェースを含むヘテロジニアスコンピューティングシステムを提供する。

【解決手段】コンピュータシステム100は、少なくとも1つの高密度ロジックデバイス106及びメモリバスに高密度ロジックデバイスを接続するコントローラを備える。複数のメモリスロットがメモリバスと接続され、アダプタポートが複数のメモリスロットのうちの少なくとも一部と関連付けられ、アダプタポートの各々は、関連付けられたメモリリソースを含む。ダイレクト・エクセキューション・ロジック要素108は、アダプタポートのうちの少なくとも1つと接続される。メモリリソース110は、少なくとも1つの高密度ロジックデバイス及びダイレクト・エクセキューション・ロジック要素によって、選択的にアクセス可能である。

(もっと読む)

ランダムアクセス動作及びファイル格納動作をサポートする分散型メモリアレイ

【課題】ランダムアクセス動作及びファイル格納動作をサポートする分散型メモリアレイを提供する。

【解決手段】分散型メモリアレイ102は、データを格納するメモリアセンブリ125を備え、各メモリアセンブリ125は双方向交差ストラップ式ネットワークを介して共に結合された複数のメモリモジュールを有し、各メモリモジュールはスイッチングメカニズムを有する。メモリアセンブリ125と結合されたゲートウェイ117をさらに備える。ゲートウェイ117は、メモリアセンブリ125へのアクセスを提供する複数のユーザーアクセスポートと、ユーザーアクセスポートにおいて、ユーザーからファイル格納動作又はランダムアクセス動作のいずれかのためのメモリアセンブリ125へのアクセス要求を受信するように、かつ、メモリアセンブリ125における利用可能なメモリの割当てユニットを割り当てるように構成されたファイルマネージャーとを備える。

(もっと読む)

メモリシステム

【課題】増設メモリを含むメモリシステムの、アドレス信号、及び、コマンド信号の波形品質を保つメモリシステムを提供すること。

【解決手段】直列に配置されるメモリコントローラと第1のメモリとメモリ用ソケットとの間に設けられる信号切替スイッチと、前記信号切替スイッチから分岐する終端抵抗と、

前記メモリ用ソケットに第2のメモリが挿入されない場合に、前記第1のメモリから前記メモリコントローラとは異なる方向への接続を、前記終端抵抗に接続する、前記信号切替スイッチの切替を行う、接続切替手段と、を有するメモリシステム。

(もっと読む)

半導体メモリモジュール

【課題】消費電流を低減した半導体メモリモジュールを提供する。

【解決手段】半導体メモリモジュール100は、インターフェースチップ110を有する。インターフェースチップ110は、内部にクロック信号同期回路(DLL)を備え、外部から入力される外部クロックClockに同期した制御信号を生成する。インターフェースチップ110は、この制御信号を低周波数化し、半導体メモリ101〜108に対して、信号線121を介してクロックを供給する。半導体メモリ101〜108は、供給されたクロックに同期したコマンドアドレス信号を、インターフェースチップ110から取り込み、コマンドに応じた動作を行う。また、半導体メモリ101〜108は、読み出し、書き込み動作において、インターフェースチップ110との間でデータ入出力を行う。インターフェースチップ110は、ビット幅を変換して外部へデータの入出力を行う。

(もっと読む)

半導体装置

【課題】予備の貫通電極を用いて貫通電極の不良を救済する場合に、置換の前後における信号パスの長さの差を短縮する。

【解決手段】ドライバ回路101〜108を有する半導体チップIFと、レシーバ回路201〜208を有する半導体チップCCと、半導体チップCCに設けられた貫通電極301〜309とを備える。半導体チップIFは、i番(iは1〜nの整数)のドライバ回路の出力端をi番からi+m番の貫通電極のいずれかに排他的に接続する出力切り替え回路120を有し、半導体チップCCは、i番(iは1〜nの整数)のレシーバ回路の入力端をi番からi+m番の貫通電極のいずれかに排他的に接続する入力切り替え回路220を有する。これにより、置換前の信号パスと置換後の信号パスとの間にほとんど配線長差が生じないことから、信号品質が高められる。

(もっと読む)

マルチポート・メモリおよびその動作

ポート間でコマンドを伝達するための増設した制御バスを有するマルチポート・メモリは、外部制御バスから受信したコマンド、または増設した制御バスから受信したコマンドに応答するように構成され得る個々のポートを有する。これにより、異なる用途に応じた性能特性の調整が容易になるような、メモリ帯域幅または待ち時間を変化させるポートの様々な組み合わせが容易に実現できる。 (もっと読む)

アダプタ

【課題】情報処理装置が備える複数のCPUソケットのうち空きソケットに接続されたメインメモリを有効に利用するための新しい枠組みを提供する。

【解決手段】本発明のアダプタ5は、パーソナルコンピュータ1が備える複数のCPUソケット7a,bのうち空きソケットに装着されるアダプタである。具体的には、第1のCPUソケット7aに装着されたCPU9から、アダプタ5が装着された第2のCPUソケット7bに接続されているメインメモリ11bへのデータ書き込み要求又は該メインメモリ11bからのデータ読み出し要求を受信した場合に、該受信したアクセス要求に応じた処理を実行する。

(もっと読む)

デジタル信号プロセッサ

【課題】性能および有用性を増進させるデジタル信号プロセッサを提供する。

【解決手段】可変長命令セットを利用するための通話を処理するデジタル信号回路において、DSPは3つのデータバスの組を含み、その上でデータはレジスタバンク120と3つのデータメモリ102,103,104と交換されることができる。レジスタバンク120は、少なくとも二つのプロセスユニット128,130によりアクセス可能なレジスタを有して使用され得る。命令フェッチユニット156は、命令メモリ152中に格納される可変長の命令を受信することを含むことができる。この命令メモリ152は3つのデータメモリ102,103,104の組から離されている。

(もっと読む)

設定可能モジュールおよびメモリサブシステム

設定可能メモリサブシステムは、第1および第2のメモリ収容デバイス(MCD)ペアを装着した回路基板を備えたメモリモジュールを含む。各MCDペアは、第2のMCDと通信する第1のMCDを有する。各MCDは、入力ポート、出力ポート、およびメモリを有し、それぞれがブリッジと通じている。命令に応じて、ブリッジは、入力ポートから出力ポートへまたは入力ポートからメモリへデータパケットの一部の少なくとも1つを転送し、あるいはメモリから出力ポートへメモリパケットの一部を転送する。折返しデバイスは、第1のMCDペアから命令およびデータパケットを受信し、第2のMCDペアへ命令およびデータパケットを伝送する。  (もっと読む)

(もっと読む)

画像圧縮装置

【課題】画像圧縮処理において、低消費電力で符号化効率高い、画像圧縮装置を提供する。

【解決手段】外部より画像信号を入力可能な画像入力部と、入力された画像に所定の画像処理を行う画像処理部と、該画像処理部で処理された映像信号を解析を行うための演算部と演算用メモリからなる画像解析部と、前記画像入力部より入力された画像を圧縮処理するための画像圧縮処理部と、前記画像解析部の演算部とは異なった汎用処理演算部と、汎用処理メモリを設け、前記画像処理部と前記画像圧縮処理部とを結ぶ第一のデータバスとは別の第二のデータバスによって、前記画像処理部と画像解析部とを結ぶ構成とした。

(もっと読む)

コンフィギュラブルな帯域幅メモリ・デバイスおよび方法

たとえばメモリ・ダイのスタックおよび装着された論理ダイを含むようなメモリ・デバイス、および方法が記載されている。記載されている方法およびデバイスは、メモリ・ダイのスタックのうち選択された部分に帯域幅を構成することを提供する。付加的な装置、システム、および方法が開示されている。 (もっと読む)

メモリーネットワークの方法、装置、およびシステム

装置とシステムには第1のノードグループを含めることができ、第1のノードグループには、メモリーに連結された第1のネットワークノードが含まれ、第1のネットワークノードには、第1のポート、第2のポート、プロセッサポート、およびホップポートが含まれる。ネットワークノードグループには、メモリーに連結された第2のネットワークノードを含めることができ、第2のネットワークノードには第1のポート、第2のポート、プロセッサポート、およびホップポートが含まれる。第2のネットワークノードのホップポートは第1のネットワークノードのホップポートに連結され、第1のネットワークノードと第2のネットワークノードとの間で通信するように構成される。ネットワークノードグループには、第1のネットワークノードのプロセッサポートに連結され、第2のネットワークノードのプロセッサポートに連結されたプロセッサを含めることができる。このプロセッサは、第1のネットワークノードを経由して第1のメモリーにアクセスし、第2のネットワークノードを経由して第2のメモリーにアクセスするように構成される。その他の装置、システム、方法についても、本明細書にて開示される。  (もっと読む)

(もっと読む)

1 - 20 / 44

[ Back to top ]