Fターム[5B061BC01]の内容

Fターム[5B061BC01]に分類される特許

1 - 20 / 43

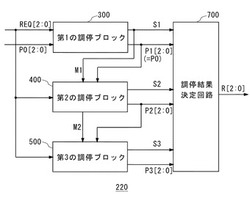

調停回路及び半導体装置

【課題】複数の要求装置の優先順位を動的に可変にでき、処理効率を高めると共に、該複数の要求装置の総数が変化した場合に柔軟に対応可能にする。

【解決手段】調停要求信号REQは各調停ブロックに入力される。各調停ブロックは、調停結果と優先信号を調停結果決定回路に出力する。第1の調停ブロック300は、さらに、優先順位パターンP0が入力され、第1の調停結果P1と第1のマスク信号M1を第2の調停ブロック400に出力する。第2の調停ブロック400は、さらに、第1の調停結果P1が入力され、第2の調停結果P2と第2のマスク信号M2を第3の調停ブロック500に出力する。第3の調停ブロック500は、さらに、第2の調停結果P2が入力される。調停結果決定回路700は、各調停ブロックからの信号に基づいて調停結果Rを選択する。

(もっと読む)

情報処理装置、その装置を用いた記録装置、及び、情報処理方法

【課題】複数の異なるプロトコルを持つバス間で共有メモリを使用するシステムにおいて、メモリアクセスの順序保障を行うことを目的とする。

【解決手段】CPUが接続されるバスとは異なるプロトコルによって動作し、ライトDMAを行うバスマスタが接続されるのと同じバスに接続される順序保障回路を備える。その順序保障回路は、ライトDMAを行うバスマスタからのライトDMA終了通知割り込み信号を検出し、リードDMAを行うバスマスタによるメモリからのリードDMA動作の後、ライトDMA完了通知割り込み信号を発行する。これにより、メモリアクセスの順序保障を実現する。

(もっと読む)

データ転送システム

【課題】動作効率を向上できるデータ転送システムを提供する。

【解決手段】1つの実施形態によれば、第1の速度でデータをそれぞれ転送する複数のラインを有するバスと、前記バスに接続された複数のマスタ装置と、前記バスに接続されたスレーブ装置とを備え、前記スレーブ装置は、前記バスにそれぞれ接続され、前記バスを介して前記マスタ装置から転送指示をそれぞれ前記第1の速度で受信する複数のスレーブインターフェースと、前記複数のマスタ装置の間における処理内容の関連性に依存した順番で前記複数のマスタ装置が優先順位付けされた優先順位情報に従って、前記複数のスレーブインターフェースで受信した転送指示の処理順を決定する調停部と、前記調停部により決定された処理順に従い、転送指示に応じた外部との間のデータ転送処理を前記第1の速度より速い第2の速度で行う処理部とを有することを特徴とするデータ転送システムが提供される。

(もっと読む)

情報処理装置

【課題】第1のチップで処理されたデータがバス及び第2のチップを経由してDRAMに転送される場合に、第1のチップで処理されたデータと第2のチップで処理されたデータとのアクセス競合を防止する。

【解決手段】デコーダ53は第1のチップ7で調停されてバス15及び第2のチップ9を経由してDRAM11に転送されるデータに対して、第2のチップ9上の配線61,63,65の中でそのデータに割り当てられている優先度に対応する配線を選択する。第2の調停部(調停部33c〜33g)は第1のチップ7で処理されたデータ及び第2のチップ9で処理されたデータの中で、同じ優先度が割り当てられているデータどうしのアクセスが競合すれば調停をし、かつ、異なる優先度が割り当てられているデータどうしのアクセスが競合すれば調停をする。

(もっと読む)

競合試験装置

【課題】本発明の一実施例では、擬似アクセス信号発生手段を設けることなく、確実にアクセス競合を発生させる競合試験装置を提供することを目的とする。

【解決手段】プログラムを記憶する記憶部と、該記憶部に記憶されたプログラムを読み出し、読み出した該プログラムを実行する第1および第2の演算部と、該記憶部の同一アドレス空間に同時になされた読み出し要求に対するプログラムの転送処理を調停し調停結果を出力する調停部とを有する演算装置のアクセス競合試験を行う競合試験装置は、該記憶部の奇数個のアドレス空間にそれぞれ該調停部の調停動作を試験する試験プログラムを記憶させ、該記憶部に記憶された複数の試験プログラムを所定の順序に従って該第1の演算部に読み出させ、該記憶部に記憶された複数の試験プログラムを該所定の順序と逆の順序に従って該第2の演算部に読み出させ、該調停部の調停結果を記録する。

(もっと読む)

データ処理システム

【課題】 データ処理システムの消費電力をきめ細かく制御する。

【解決手段】 複数のマスターの各々は、データの転送要求とともにデータの転送速度を示すスピードグレード信号を出力する。調停回路は、複数のマスターからの転送要求およびスピードグレード信号を調停する。クロックイネーブル生成回路は、調停回路により調停されたスピードグレード信号に応じて、有効期間の比率が異なるクロックイネーブル信号を生成する。スレーブは、クロックイネーブル信号が有効なときにクロック信号を受けて動作し、調停回路により調停された転送要求に応じてデータを転送する。これにより、スレーブを動作させるクロック信号の周波数を転送要求毎に変更でき、スレーブの電力のきめ細かな制御を容易に実施できる。

(もっと読む)

データアクセス制御装置

【課題】 アクセス制御部からシリアルバスを介して被アクセス部が接続される構成において、アクセス期間を短縮化させる。

【解決手段】 アクセス制御部1は、 シーケンスデータと非シーケンスデータを特定しシリアルバス3からアクセス先を指定してデータ伝送する。被アクセス部5、7は、シリアルバス3に直列接続され非シーケンスデータおよびシーケンスデータがアクセスされる。被アクセス部5、7は第1、第2のメモリ空間11、13、調停部15およびアクセス空間17を有する。第1のメモリ空間11はシリアルバス3に接続され非シーケンスデータを記憶する。第2のメモリ空間13はシリアルバス3に接続されシーケンスデータを記憶する。調停部15は非シーケンスデータとシーケンスデータを調停する。アクセス空間17は調停部15からの非シーケンスデータとシーケンスデータのアクセスを受ける。

(もっと読む)

インタフェース装置、画像形成装置

【課題】送信データの書き込み要求と、受信データの読み出し要求とが重複して発生しているときに、受信データによるメモリオーバーを起こすことなく、送信データの書き込みと受信データの読み出しとからなる一連の処理を行う時間を短縮することができるインタフェース装置を提供する。

【解決手段】調停部24は、送信データの書き込み要求と、受信データの読み出し要求とが重複して発生して、書き込み要求を読み出し要求に優先して有効としている間において、送信データ記憶部20に記憶されている送信データのデータ量が予め設定された第1データ量を超えており、且つ、受信データ記憶部22に記憶されている受信データのデータ量が、記憶容量未満の範囲で予め設定された第2データ量を超えているときには、書き込み要求を有効とすることを中断して、一時的に読み出し要求を書き込み要求に優先して有効とした後に、書き込み要求を有効とすることを再開する。

(もっと読む)

インターラプトプロキシ機能を具備したシステムオンチップ及びそのインターラプトプロキシ処理方法

【課題】各種IPで発生したインターラプト処理をエラーなく、より迅速に実行することができるシステムオンチップを提供する。

【解決手段】本発明のシステムオンチップは、プロセッサコアとモジュール化された複数のIPの以外に別途のインターラプトプロキシ処理部を含む。インターラプトプロキシ処理部はプロセッサコアと複数のIPに接続され、複数のIPに対するインターラプト関連タスク、例えばインターラプト解除を専担して処理する。本発明の実施形態の構成により、システムオンチップの動作パフォーマンスが改善される。

(もっと読む)

情報処理装置

【課題】最小限の回路規模により複数の暗号化処理を並列に行う。

【解決手段】メモリ上のデータを転送する複数の転送手段と、データに処理を施すデータ処理手段と、複数の転送手段から転送要求をアビトレーションするアビトレーション手段と、データ処理手段における処理に関するパラメータを複数の転送手段ごとに保持する手段と、アビトレーションの結果に基づき、パラメータをデータ処理手段に出力する手段と、処理されたデータの出力先を選択する出力先選択手段と、を有し、データ処理手段は、動作状況を示す動作中判別信号をアビトレーション手段に送信し、アビトレーション手段は、転送要求それぞれの優先度が記述されたアビトレーションポリシーを保持しており、当該アビトレーションポリシーと動作中判別信号とに基づき、転送要求をアビトレーションし、出力先選択手段は、アビトレーションの結果と動作中判別信号に基づき、データの出力先を選択する。

(もっと読む)

情報処理装置およびメモリアクセス調停方法

【課題】プロセッサの内蔵メモリに対して、小規模で常に優先かつ高速なメモリへのデータ入出力機構を実現する。

【解決手段】命令をパイプライン処理するプロセッサと、プロセッサに内蔵するメモリと、メモリに対し高い優先度でアクセスをする入出力制御手段からなる情報処理装置において、メモリアクセス調停方法は、プロセッサと入出力制御手段のメモリへのアクセスが競合した場合に、プロセッサに供給するクロックをウェイトさせるステップ(S512)と、入出力制御手段のメモリへのアクセスを実行するステップ(S506)と、入出力制御手段のメモリへのアクセス終了後にプロセッサのクロックウェイトを解除し、プロセッサのメモリへのアクセスを実行するステップ(S507、S511)からなる。

(もっと読む)

バス調停回路及びバス調停方法

【課題】各バスマスタが複雑なバス要求をしたとしても、最適なバス使用許可期間を保証することができるバス調停回路を提供することである。

【解決手段】本発明にかかるバス調停回路1は、複数のバスマスタ4、5、6からのアクセス要求のうち優先度の高いバスマスタからのアクセス要求に対してバス使用権を許可する固定優先判定回路3と、複数のバスマスタからのアクセス要求を固定優先判定回路3へアサートするか否かを判定する判定調整回路2と、を備える。判定調整回路2は、バス使用権が許可されているバスマスタのアクセス要求とバス使用権が許可されていないバスマスタのアクセス要求とが競合した場合、バス使用権が許可されているバスマスタのアクセス要求を所定の期間マスクする。

(もっと読む)

データ処理システム

【課題】固定優先順位バスアクセス調停方式を用いる階層バス構造において、システム動作に応じて優先順位が更新される場合においても、バスアクセス要求の調停を正確に実行する。

【解決手段】複数の上位階層バス回路(6A,6B)各々において、対応のバスマスタ群(2A,2B)に含まれるバスマスタのアクセス要求を優先順位に従って調停し、アクセス要求が許可された選択バスマスタの優先順位情報を示す優先順位伝達信号(PRA,PRB)を下位階層のバスコントローラ(10)へ転送する。下位階層バス回路(9)において、下位バスコントローラが、転送された優先順位伝達信号(PRA,PRB)に従ってアクセス要求の調停を実行して、優先順位の高い上位階層バス回路またはバスマスタを選択する。

(もっと読む)

マルチプロセッサシステム

【課題】プロセッサと演算手段およびLANコントローラから各バスを介してアクセス可能な共有メモリで構成されるマルチプロセッサシステムにおいて、共有メモリへのアクセスが競合するとシステム全体のスループットが低下する。

【解決手段】同期制御手段14から送付されるタイムテーブルTBLにしたがって、各バス41〜43から共有メモリ5へのアクセスを許可するタイミングと時間帯を決定するデータ転送同期手段6を用いることで、共有メモリ5のアクセスを管理・制御し、プロセッサ11〜13と演算手段21〜23およびLANコントローラ31〜33がメモリアクセスで待たされたり、データ転送が輻輳する状態の発生を防ぐ。

(もっと読む)

バスの使用権を制御する装置および方法

【課題】複数のIPコアによりバスが共用される場合におけるバスの使用のリアルタイム性を保証し、さらにバスの使用効率の向上を図る。

【解決手段】複数のIPコア30によるバスの使用権を制御する装置であって、主制御部10と、個々のIPコア30に対応して個別に設けられた副制御部20とを備える。主制御部10は、所定のタイム・スライスに基づいて予め定められたスケジュールにしたがって、各々のIPコア30とバスとの間の接続を切り替える。副制御部20は、主制御部10の制御下で、このスケジュールにしたがって、IPコア30によるバスの使用を制御する。

(もっと読む)

情報処理装置、割り込み制御方法

【課題】優先順位の高いOSと優先順位の低いOSがハードウェア資源を共有する場合に、割り込み処理に関して、優先順位の高いOSの負荷を低減可能な情報処理装置及び割り込み制御方法を提供すること。

【解決手段】本発明に係る情報処理装置は、優先順位の高い第1のOS11と、第1のOS11とハードウェア資源を共有する優先順位の低い第2のOS12を備え、ハードウェア資源より第1のOS11が割り込み通知を受けた場合に第1のOS11が処理する割り込みでないときに第2のOS12に対して割込み通知の転送処理を実行する。第1のOS11の負荷制御部70は、第1のOS11の転送処理に伴う負荷を検出し、当該転送処理に伴う負荷の状態を判定する。第2のOS12の遅延処理部42等は、負荷が大きいと判定した場合に、第2のOS12の処理を遅延させる。

(もっと読む)

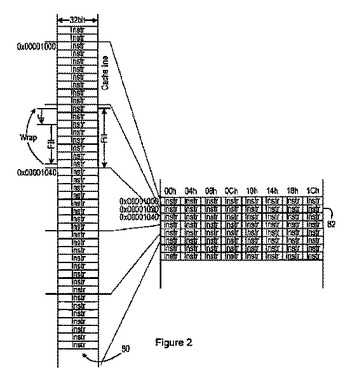

データバースト間の競合の解決

組込みシステムにおいて、複数のデータ要求装置と、複数のデータソースと、データ要求装置及びデータソースを相互接続するバスファブリックとがあり、バスファブリックが複数のバスコンポーネントを備える。バスコンポーネントと関連付けられたデータソース及び調停装置のうちのいくつか又は全ては、競合するデータバーストのうちの第1のデータバーストを選択すること、第1の選択されたデータバーストのクリティカル部分の長さを判定すること及び選択されたデータバーストのクリティカル部分を処理することによりデータバースト間の競合を解決する。次に、競合するデータバーストのうちの第2のデータバーストが選択され、第2の選択されたデータバーストのクリティカル部分の長さが判定され、第2の選択されたデータバーストのクリティカル部分が選択されたデータバーストの非クリティカル部分の前に処理される。  (もっと読む)

(もっと読む)

ビデオ符号化・復号化装置

【課題】限られたメモリリソースを用いてシステムパフォーマンスを最大にすることができるビデオ符号化・復号化装置を提供すること。

【解決手段】ビデオ符号化・復号化装置100は、動き補償装置101のダイレクトメモリアクセス手段160が、補間手段180から補間完了を受け取った後にDMA要求を生成し、メモリアクセス調停手段110からDMA ACKを受け取った後、最大DMAバースト制約及びブロックバッファサイズ制約に従って複数個のDMA入力データを受け取り、復号化パラメータと演算処理レベルLcと最大DMAバースト制約とブロックバッファサイズ制約とに従って、参照ピクセルデータを可変サイズブロックバッファ170に格納するためのブロックメモリアドレスを生成する。

(もっと読む)

資源要求調停装置、資源要求調停方法、及び、コンピュータプログラム

【課題】本発明は、予め固定された優先順位を用い、かつ当該優先順位の他には資源要求装置間の関係を関知することなく、各資源要求装置へのサービス品質を管理する資源要求調停装置を提供する。

【解決手段】本発明の資源要求調停装置において、リクエストマスク部50、51は、それぞれメモリアクセス要求部80、81が必要最小頻度を超えて発行したメモリアクセス要求REQをマスクし、調停部40は、リクエストマスク部50、51によってマスクされなかったメモリアクセス要求RREQの一つを、予め固定された優先順位に従って承認する。これにより、当該優先順位の他には各メモリアクセス要求部間の関係を関知することなく、しかも、固定優先順位のごく簡便な調停によって、各メモリアクセス要求部が必要とする資源要求の承認頻度が保証される。

(もっと読む)

DMAコントローラ

【課題】データ転送に用いるバス帯域に応じてバスを解放するDMAコントローラを提供。

【解決手段】DMAコントローラ24は、各モジュールがデータ転送に用いるバス帯域を取得する帯域設定レジスタ38と、各モジュールのデータ転送回数を取得する転送カウンタ36と、各モジュールの優先度を取得する優先度レジスタ40を有し、バス帯域、データ転送回数、および優先度を基に各モジュールの優先順位を決定し、この優先順位に従って各モジュールにバスを解放することによって、帯域が設定されているモジュールには帯域を保証したデータ転送を行わせる装置である。

(もっと読む)

1 - 20 / 43

[ Back to top ]