Fターム[5B061CC00]の内容

バス制御 (3,799) | 入出力割込み (144)

Fターム[5B061CC00]の下位に属するFターム

ベクタ割込み (12)

ノンベクタ割込み (14)

割込みレベルを有するもの (18)

割込み受付け回路 (53)

割込み要因保持回路 (33)

Fターム[5B061CC00]に分類される特許

1 - 14 / 14

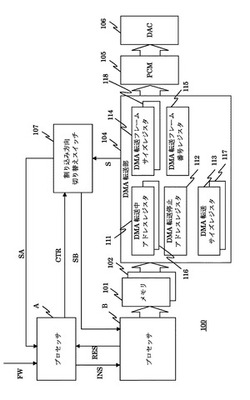

オーディオ再生装置及びオーディオ再生方法

【課題】DMA転送を用いるオーディオ再生装置に対して、消費電力を抑制すると共に、通常再生と特殊再生の切り替え時に誤再生を回避する。

【解決手段】DMA転送部104は、DMA転送フレーム番号レジスタ115、DMA転送フレームサイズレジスタ114、DMA転送中アドレスレジスタ111、DMA転送停止アドレスレジスタ112を備える。プロセッサAにより電源のオン/オフが制御されるプロセッサBは、DMA転送中に、通常再生とは異なる特殊再生が要求されたときに、メモリ101に格納されたフレームのうちの、該フレームの転送が完了すると、メモリ101に格納されたデコード後データの転送を停止する停止フレームの終端アドレスをDMA転送停止アドレスレジスタ112に設定する。

(もっと読む)

データ転送装置およびデータ転送方法

【課題】上位装置の記憶部にデータの転送が終了した毎にデータ転送が完了した旨を上位装置の制御部へ通知する。

【解決手段】データを転送する転送先アドレスおよび転送データ数を定義した転送設定情報を複数記憶する転送リスト5と、転送リスト5に設定されたそれぞれの転送設定情報に従って入力データを上位装置の記憶部に転送するとともに該転送が完了するとその旨を上位装置へ通知(48)する転送データ制御部4と、その通知の要否を記憶する割込みモードレジスタ41とを設け、転送データ制御部4は、割込みモードレジスタ41に通知要が記憶されているとき、転送リスト5に設定された転送設定情報毎に、入力データの転送が完了した旨を上位装置へ通知する。

(もっと読む)

データ受信システムおよび割り込み実行方法

【課題】複数のデータ出力装置からの非同期の割り込み要求信号を欠落なく、効率的に確実に、データ受信装置に、任意のタイミングでデータを送信するデータ受信システムおよび割り込み実行方法を提供する。

【解決手段】複数のデータ出力装置から非同期で割り込み要求もしくはデータを受信するデータ受信システムにおいて、データ出力装置からの割り込み要求信号を検出し、CPUに割り込み信号を送信する割り込み発生回路部と、データ出力装置から受信データを取得した複数のデータを一時的に保持するデータバッファ部と、割り込み発生回路部からの割り込み信号を受信した際に全てのデータ出力装置に対してデータが入力されているか否かを判断し、入力されているデータを順次受信する割り込みルーチンと、全てのデータ受信が終了した場合に割り込みリセットを実行するCPUを有するデータ受信システムを提供する。

(もっと読む)

半導体集積回路

【課題】複数の割り込み要因に対する処理での重複処理の矛盾を解消する際の負担を軽減する。

【解決手段】外部メモリ7へデータ転送が完了し、高優先度のデータ転送完了割り込みが発生する。受信中断の間に所定パケット数のデータ転送が未完了の場合、低優先度のタイマ割り込みが生成される。割り込みに応答した外部メモリのデータ処理前にカウンタ114から転送パケット数が取得される。受信再開後に、カウンタは転送再開パケット数を格納する。タイマ割り込み発生18Cに応答したカウンタからの転送パケット数の取得18Dの後、データ転送完了割り込み18Eが生じる。取得転送パケット数に従って、タイマ割り込みの発生18Cに応答する処理18I(図18(A))もしくはデータ転送完了割り込みの発生18Eに応答する処理18G(図18(B))のいずれかの実行が省略される。

(もっと読む)

仮想プロセッサへの直接的なインタラプトの送信

【課題】本発明の課題は、仮想化環境における効果的なインタラプト処理を実現する装置、方法及びシステムを提供することである。

【解決手段】上記課題を解決するため、本発明は、ゲストが仮想プロセッサ上で実行されている間に、インタラプトリクエストを受け付けるインタフェースと、前記インタラプトリクエストの属性に基づき、前記インタラプトリクエストが前記仮想プロセッサに送信されるべきか判断する送信ロジックと、前記インタラプトリクエストが前記仮想プロセッサに送信されるべきでないと前記送信ロジックが判断した場合、前記ゲストからホストに当該装置の制御を移行するイグジットロジックとから構成されることを特徴とする装置を提供する。

(もっと読む)

割込検出装置および情報処理システム

【課題】メッセージ形式の割込み(MSI:Message Signaled Interrupt)の特性を利用して、割込処理を柔軟に行う。

【解決手段】PCIデバイス#A(310)がMSIを送信すると(801)、メモリ220にMSIの内容がライトされる(802)。ブリッジ装置100は、PCIデバイス#A(310)からメモリ220へのメッセージのアドレス情報を監視しており、所定のアドレス領域に該当するMSIを検出する(803)。このMSI検出を契機として、ブリッジ装置100は、新たなMSIを発行する(804)。新たなMSIのアドレス情報に従ってPCIデバイス#B(320)は当該MSIを受信する(805)。これにより、プロセッサによる割込処理を経ることなくデバイスの起動処理が行われる(806)。

(もっと読む)

制御装置及び割り込み信号発生方法

【課題】 割り込み信号の周期が正常であるか否かの検証が容易な制御装置を提供する。

【解決手段】 第1タイマ回路51、第2タイマ回路53、第3タイマ回路55を備え、これらのタイマ回路から出力される割り込み信号により割り込み処理を実行するマイコン14であって、基準となる割り込み信号を送出する第1タイマ回路51と、第1タイマ回路51から送出された基準となる割り込み信号に基づいて割り込み処理の処理タイミングを判定し、処理タイミングとなると割り込み信号の送出命令を第2タイマ回路53、第3タイマ回路55に出力するソフトウェア処理部14と、割り込み信号の送出命令を受信して、ソフトウェア処理部14に割り込み信号を送出する第2タイマ回路53、第3タイマ回路55とを有する構成としている。

(もっと読む)

画像処理装置、画像処理制御方法、画像処理制御プログラム及び記録媒体

【課題】本発明は、外部IFを介して外部装置と通信を行うとともに画像形成処理、画像読み取り処理等のデータ処理を実行する画像処理装置、画像処理制御方法、画像処理制御プログラム及び記録媒体に関する。

【解決手段】複合装置1は、画像読み取り部4、画像印刷部5及び操作部6及び外部IF部12に対応して、それぞれDMAC9〜12を備えており、また、読み取りジョブ制御処理プログラム、印刷ジョブ制御処理プログラム、操作制御処理プログラム及び複写ジョブ制御処理プログラムを備え、各プログラムが、それぞれの動作制御の開始時に、各DMAC9〜12への動作データの設定制御処理において、それぞれの制御対象の処理を優先させる割り込み優先度を動作データとして設定して割り込み発生タイミングを設定し、該動作制御の終了時に、該割り込み優先度を所定の初期割り込み優先度に戻している。

(もっと読む)

データ処理装置

【課題】簡素な構成で、複数のコントローラ間で割込処理を効率良く行うことができるデータ処理装置を提供する。

【解決手段】タイマ割込機能を有するCPU202のタイマレジスタに対応する領域をPCIメモリ500内に設け、MFPコントローラ100からPCIメモリ500に設けられた当該領域にアクセスすることにより、カウントの開始を書き込めるようにする。

(もっと読む)

割込制御方法および情報処理装置

【課題】割込頻度が高い状態でもアプリケーション処理時間を確保できるように、割込要因のデータ処理を低優先度のタスクから実行する割込制御方法において、アプリケーションが実行権を長時間握ると、データ処理性能が低下する。

【解決手段】データ処理タスク33を呼び出す開始処理タスク32を起床させた時(S12)、タイマ35による時間カウントを開始する(S13)。時間カウント開始後、一定時間が経過した時にタイマ割込を発生させ(S41)、開始処理タスク32に実行権を移す(S43)。開始処理タスク32の実行時は、タイマ35による時間カウントを停止してから(S21)、データ処理タスク33を呼び出す(S22)。

(もっと読む)

データ処理装置

【課題】データ処理装置におけるCPUのストールサイクルを改善する。

【解決手段】CPU(10)と、上記CPUに結合された第1バス(12)と、上記第1バスよりもデータの転送速度が遅い第2バス(16)と、上記第1バスに結合された割り込み処理回路(15)と、上記第2バスに結合され、上記CPUによってアクセス可能な周辺モジュール(17,18)とを含むとき、上記周辺モジュールは、上記CPUに対する割り込み要因を出力可能な第1機能を含み、上記割り込み処理回路は、上記周辺モジュールから出力された割り込み要因に基づいて上記CPUに割り込み要求を通知する第2機能を含む。上記CPUは、割り込み要因解析において上記割り込み処理回路をアクセスすれば良く、上記周辺モジュールをアクセスする必要がない。これにより、上記CPUのストールサイクルが改善される。

(もっと読む)

マイクロプロセッサ、ネットワークシステム及び通信方法

【課題】第1に、ネットワークで接続されたマイクロプロセッサがネットワークからパケットを受信した際に発生するCPUへの割り込みを極力減らし、プロセッサを効率的に動作させるということ。第2に、送信側のマイクロプロセッサにレスポンスのよい返信を返すことが可能なマイクロプロセッサ及び通信方法を提案すること。

【解決手段】マイクロプロセッサにCPUと通信モジュールを備える。通信モジュール3は、マイクロプロセッサが管理する情報を記憶するレジスタ22を有する。通信モジュールは、ネットワークを通して入力されるパケット内の所定のビット位置の情報と、レジスタに保持された情報を比較し、比較結果により、パケット受信に対応した処理をCPUが行なうか否かを判定する。

(もっと読む)

ユーザ・モード・ドライバへ割り込みを配送する方法

デバイス・ドライバがユーザ・モードのレベルで動作することができるフレームワークを提供するシステム及び方法である。プラットフォーム(例えば、APIC)又はバス(PCIバス)のジェネリックな特徴を用い、ユーザ・レベルのドライバを待機してデバイス割り込みをクリアすることを必要とせずに、CPUを割り込みモードから取り出す。これにより、ユーザ空間において完全なデバイス・ドライバを書くことが可能になる。デバイス・ドライバは、依然として割り込みに関する告知を受け取るが、割り込みの優先順位においてではない。同じ方式を共有された割り込みにも拡張することができ、その場合には、複数のデバイスが単一の割り込みラインを共有する。  (もっと読む)

(もっと読む)

受信フレーム処理装置、通信処理装置、および受信フレーム処理方法

【課題】 後段の処理装置におけるフレーム処理量に合わせて割り込みを生成して、フレーム処理量に占める割り込み処理量の割合が小さくなるように割り込みを行うこと。

【解決手段】 総フレーム処理量予測手段1100は、フレームを受信すると、後段処理装置5000に渡していない受信フレーム全ての後段処理装置5000における総フレーム処理量を予測して、処理量比較手段1200へ出力する。処理量比較手段1200は、基準処理量保持手段1300からの基準処理量と、総フレーム処理量予測手段1100からの総フレーム処理量とを比較し、総フレーム処理量が基準処理量と比較して大きい場合には、割り込み生成手段1900に通知する。割り込み生成手段1900は、処理量比較手段1200から総フレーム処理量が基準処理量より大きいことを通知されると、後段処理装置5000に対して割り込み信号を生成する。

(もっと読む)

1 - 14 / 14

[ Back to top ]