Fターム[5B061QQ01]の内容

Fターム[5B061QQ01]の下位に属するFターム

衝突防止 (8)

Fターム[5B061QQ01]に分類される特許

1 - 20 / 57

信号転送回路

【課題】プロトコルに従ってアクセスを行うアービタとバスマスタとの間の入出力信号のタイミングの制約を改善することができる信号転送回路を提供する。

【解決手段】バスマスタから入力されたメモリへのアクセス要求をアービタに中継する際に、入力されるアクセス要求入力信号およびメモリアドレス入力信号のタイミングを整えたアクセス要求出力信号およびメモリアドレス出力信号を出力すると共に、アービタから入力されるアクセス許可入力信号に先行して、アクセス許可出力信号をバスマスタに出力する制御信号転送部と、データをバスマスタまたはアービタに中継する際に、入力されるそれぞれのデータ入力信号のタイミングを整えたそれぞれのデータ出力信号を、バスマスタまたはアービタに出力すると共に、アービタから入力されるデータ有効期間入力信号のタイミングを整えたデータ有効期間出力信号をバスマスタに出力するデータ信号転送部と、を備える。

(もっと読む)

情報処理装置および画像形成装置

【課題】バスのロックを自動的に解除することによってユーザーの利便性を向上させることが可能な情報処理装置を提供する。

【解決手段】この情報処理装置では、バス制御部140は、複数のデバイスのうちのいずれかのデバイスが他のデバイスに処理要求を行った後に、処理要求元のデバイスまたは処理要求先のデバイスからバス1に対して処理完了を示す完了信号の送信が無いことに起因するバス1のロックを検知したとき、完了信号をバス1に対して代理で送信する。

(もっと読む)

情報処理装置及びメモリ管理方法

【課題】 転送装置から転送されてくる画像データを効率的に処理できる情報処理装置およびメモリ管理方法を提供することを目的とする。

【解決手段】 実施形態によれば、情報処理装置は、メモリと、テーブルと、変更手段と、通知手段とを有する。メモリは、複数の画像データを保持する複数のバッファ領域を有する。テーブルは、複数のバッファ領域を画像データが書き込まれる受信バッファと画像データを保持する保持バッファとに割り当てる。変更手段は、前記受信バッファに書き込まれた画像データを保持する場合、前記保持すべき画像データが書き込まれた受信バッファと保持バッファとを入れ替える。通知手段は、変更手段により受信バッファと保持バッファとを入れ替えた場合、変更後の受信バッファを示す情報を画像転送元へ通知する。

(もっと読む)

バス制御装置及び情報処理装置

【課題】外部からバス使用量を制御できない管理外モジュールを有する場合であっても、バス上のデータ転送量がバス帯域を超えることを抑制可能なバス制御装置を提供する。

【解決手段】本発明にかかるバス制御装置は、情報処理装置に対してバス制御を行うバス制御装置であり、バス監視部と、制御部を有する。情報処理装置は、バスと、外部によりバスの使用量が制御できない管理外モジュールを1つ以上含む管理外ブロックと、外部によりバスの使用量が制御できる管理内モジュールを1つ以上含む管理内ブロックとを備える。制御部は、バス監視部が得たデータ転送量と、管理内ブロックによるバスの使用量とから管理外ブロックによるバスの使用量を算出すると共に、算出した管理外ブロックのバスの使用量と、管理内ブロックによるバスの使用量との和が第1の閾値以下になるように、管理内ブロックによるバスの使用量を制御する。

(もっと読む)

情報処理装置及び画像形成装置

【課題】一つのチップの機能ブロックから別のチップの機能ブロックへデータを転送する場合に、予め定められた機能ブロックからのデータについては、転送遅延が生じないようにする。

【解決手段】監視部37は、第1の送信バッファ25に蓄積されているデータ量が、所定のしきい値を超えていれば、第1のチップ11と第2のチップ13との間でデータの転送遅延が発生するとみなす。しきい値を超えれば、第2にチップ13に配置された複数の第2の機能ブロックのうち予め定められた第2の機能ブロックについては、第2のチップ13において、第2の送信バッファを経由させずに第2の追越用ラインを経由させ、第1のチップ11において、第1の受信バッファ35を経由させずに第1の追越用ライン39を経由させて、宛先となる第1の機能ブロック19へ転送させる。

(もっと読む)

データ転送装置

【課題】スケジューリングテーブルや入出力データバッファからデータを読む際に一過性の入出力エラーが発生しても誤った入出力データの転送を回避する。

【解決手段】制御部130は、データ転送に先立ち、スケジューリングテーブル12aの先頭位置に予め設定された、読み出したデータが目的のデータであることを示す第1の特定の情報と、入出力データバッファ12bの先頭位置に予め設定された第1の特定の情報とを照合し、更に、スケジューリングテーブルの任意の位置に予め設定された、ポインタが所望の位置にあることを示す第2の特定の情報と、入出力データバッファの任意の位置に予め設定された第2の特定の情報とを照合し、共に一致した場合にデータ転送を許可する。

(もっと読む)

制御装置

【課題】記憶装置と接続する情報処理装置などで発生するノイズの影響を受けることなく、記憶装置の状態を制御する。

【解決手段】記憶装置450と接続する信号線を介して、記憶装置450の状態を設定する第1の設定手段と、制御装置430に接続される第1の伝送路を介して、記憶装置450の状態を設定する第2の設定手段と、第1の伝送路を介して制御装置に接続されると共に、第2の伝送路を介して演算装置420と接続され、第1の伝送路と第2の伝送路とを切り替えて、制御装置430あるいは演算装置420の一方を、記憶装置450と通信可能に接続する切り替え手段440と、を備える。

(もっと読む)

I2Cバス通信制御システム、及びI2Cバス通信制御方法

【課題】I2Cバスフリーズの原因となったスレーブ装置を速やかに特定する。

【解決手段】プロセッサ100が主プロセッサ、プロセッサ110、1m0が従プロセッサの場合に、主プロセッサがI2C通信を開始し、通信相手を指定するスレーブアドレスを送出したとき、従プロセッサ110、1m0は、I2Cバスに流れているスレーブアドレスを取得しておく。従プロセッサ110、1m0のいずれかに切り替わったときにI2Cバスがフリーズしていた場合、取得済みスレーブアドレスに基づいてバスフリーズ原因のスレーブ装置を特定する。また、特定したスレーブ装置のみに対してリセットをかけることで、I2Cバスフリーズから復帰する。

(もっと読む)

データ転送装置、メモリ制御装置、およびメモリシステム

【課題】誤り訂正が発生したとしてもデータ伝送が待たされる時間を少なくし、データ転送に要する時間を短縮することが可能なデータ転送装置、メモリ制御装置、およびメモリシステムを提供する。

【解決手段】データ転送元の第1メモリ装置200の第1メモリアドレスと、データ転送先の第2メモリ装置の第2メモリアドレスと、転送データに誤りが検出されたか否かを示す誤り信号と、誤り訂正が完了して第2メモリ装置106に格納しているデータが有効であるか否かを示す有効信号を記憶する領域を複数含むデータ情報記憶領域109と、第2メモリ装置に格納しているデータのうち、データが有効であるメモリのアドレスである第2メモリ有効アドレスを出力し、第2メモリ装置の第2メモリ有効アドレスからデータを読出し、読出したデータと共に、第2メモリ有効アドレスに対応する第1メモリ装置のアドレスを転送する制御部108とを有する。

(もっと読む)

データ転送装置、データ転送方法及びデータ転送プログラム

【課題】データの転送元領域と転送先領域とが重なった場合において、バースト転送機能を用いて転送を行った場合であっても、データ破壊の発生を防止することを目的とする。

【解決手段】転送元領域から読み出したデータをバッファ領域へ一旦書き込み、バッファ領域に書き込まれたデータを転送先領域へ書き込む。この際、データの書き込みを完了したバッファ領域におけるアドレス値と、データを読み出そうとしているバッファ領域におけるアドレス値との大小関係に基づき、バッファ領域からのデータ読み出しを制御する。

(もっと読む)

マイコン、処理同期方法

【課題】一方のコアから他方のコアに割込みによりイベントを通知する際、イベントの誤通知を検知できるマイコンを提供すること。

【解決手段】第1のコア52と第2のコア53間で通信する通信手段43と、第1のコアと第2のコアが共有する共有メモリ51と、外部信号を取得して第1の処理を実行し、第1の処理毎に所定情報を共有メモリに書き込む第1の処理手段55と、通信手段を介して第2のコアに処理要求を出力する処理要求手段33と、処理要求をトリガーに第2の処理を実行する第2の処理手段56と、を有するマイコン100において、第2のコアは、処理要求を受け付けた場合、共有メモリから最新の所定情報と前回の所定情報を読み出し、最新の所定情報と前回の所定情報に規定された関係がある場合のみ、第2の処理手段に第2の処理の実行を許可する比較手段57、を有する。

(もっと読む)

ダイレクトメモリアクセス制御装置、ダイレクトメモリアクセス制御システム、プログラム、画像処理装置および複合機

【課題】、DMA実行中の転送元および転送領域へのメモリアクセスによる誤動作継続防止を目的とする。

【解決手段】同一のシステムバスを用いて、DMAおよびメモリアクセスの転送制御を行うDMAコントローラであって、DMAにおける転送元のアドレス範囲、およびDMAにおける転送先のアドレス範囲が格納される各レジスタ22〜25と、メモリアクセスにおけるデータ転送を行うためのアドレスが、システムバス上に指定されると、指定されたアドレスが、DMAの転送元のアドレス範囲内、もしくはDMAの転送先のアドレス範囲内のアドレスである場合、メモリアクセスにおけるデータは、不正アクセスである旨の不正アクセス警告信号を出力する不正アクセス検出回路1と、を有することを特徴とする。

(もっと読む)

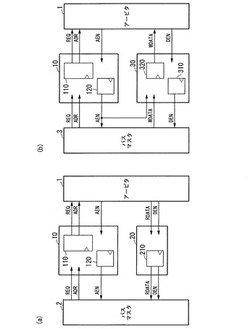

バスシステムおよびそのデッドロック回避回路

【課題】スプリットトランザクションにより複数のスレーブへの同時アクセスを許容したシステムにおいて、デッドロックの発生を防止する。

【解決手段】先行トランザクション情報管理部410は、対応するマスタから複数のスレーブの何れかに先に発行された先行トランザクション情報を管理する。発行停止判定部420は、先行トランザクション情報に基づいて、対応するマスタから新たに発行されたトランザクションがデッドロックの要因になるか否かを判定する。レスポンス出力制御部430は、先行トランザクション情報に基づいて、対応するマスタへ返送すべきレスポンスを制御する。退避バッファ470は、先行トランザクションに対する複数のスレーブからのレスポンスが予め期待された順序とは異なる順序で戻ってきた場合に、そのレスポンスを退避する。

(もっと読む)

バス接続回路及びバス接続方法

【課題】I2Cバス接続された周辺部品がBus-Busyとなった場合でも、システム全体が動作し続けることができるようにすること。

【解決手段】本発明のバス接続回路21は、周辺部品側のI2C端子レベルを検出するバッファ24と、周辺部品とシステム全体のI2Cバスとを切り離すSW25と、I2C故障検出制御モジュール26と、周辺部品側がHi-Z状態になっているかを確認するためのPull Up抵抗34と、Pull Down抵抗35と、を備える。I2C故障検出制御モジュール26は、バッファ24で受けた値が、Highレベルか、それともLowレベルであるかを判断するH/Lレベル検出部30と、Lowレベルの持続時間を測るLowレベル検出時間計測部31と、SW25をON/OFF制御するI2Cバス切断制御部32と、Pull抵抗制御部33と、を備える。

(もっと読む)

信号伝送装置、情報機器、および通信システム

【課題】データ通信時の異常発生を低減する。

【解決手段】光伝送媒体と接続可能なQSFPコネクタ301、302と、機器と接続可能なカードエッジ330と、カードエッジ330に対して送受信される電気信号を中継するスイッチ/ブリッジ320と、光伝送媒体により伝送された光信号を変換した電気信号をQSFPコネクタ301、302から入力し、入力した電気信号の電気的特性を調整してスイッチ/ブリッジ320に出力するリピータ311、312と、を備え、スイッチ/ブリッジ320は、調整された電気信号をカードエッジ330に中継し、カードエッジ330から入力した電気信号をQSFPコネクタ301、302に中継する。

(もっと読む)

データ転送装置、データ転送方法およびプログラム、ならびに、画像形成装置

【課題】優先順位の高い要求に対するデータ転送性能を保証できるようにする。

【解決手段】アービタによる複数のDMACが発行した要求の調停を禁止する調停禁止期間と、調停を禁止しない調停有効期間とを設け、調停禁止期間と調停有効期間とを繰り返す。アービタは、高優先度のDMACが発行した要求に対して、調停禁止期間を無視して当該要求を受け付ける。また、調停禁止期間と調停有効期間とが繰り返される調停禁止サイクル有効期間と、調停有効期間のみを含む調停禁止サイクル無効期間とを設け、調停禁止サイクル有効期間の終了後に調停禁止サイクル無効期間を開始させ、低優先度のDMACが発行した要求を受け付ける。

(もっと読む)

バスシステムおよびバスシステムと接続機器とを接続するブリッジ回路

【課題】バスシステムにおいてスプリットトランザクション実行中の接続機器を、誤動作させることなくバスシステムから切断する。

【解決手段】M台のマスタ100がマスタ切断ブリッジ400を介してインターコネクト300に接続される。S台のスレーブ200がスレーブ切断ブリッジ500を介してインターコネクト300に接続される。マスタ切断信号409により切断が示されると、対応するマスタ100に代わってマスタプロトコル整合部401がスレーブ200とのプロトコル上のやりとりを行う。スレーブ切断信号509により切断が示されると、対応するスレーブ200に代わってスレーブプロトコル整合部501がマスタ100とのプロトコル上のやりとりを行う。マスタ100またはスレーブ200は任意のタイミングで切断および再接続される。

(もっと読む)

データ転送制御装置及び電子機器

【課題】スケルチ検出回路の回路規模を小さくすると共に、設計のために要する負荷小さくする。また、パケットを受信する後段の機器に対してのドリブルビットの伝播をなくす。

【解決手段】第1のパケットを受信する第1のポートと、第2のパケットを送信する第2のポートと、前記第1のパケットの終了コードである第1のコードを検出する第1の制御部と、前記第2のパケットの終了コードである第2のコードを生成する第2の制御部と、を含み、前記第2のパケットは、前記第1のパケットとして受信したデータの前記第1のコード以降のデータを前記第2のコードに置き換えたものであることを特徴とするデータ転送制御装置を提供する。

(もっと読む)

計算機装置及びその制御方法

【課題】長距離及び高周波数伝送が必要な場合に、振幅が減衰した信号とノイズを区別し、ノイズによる誤動作を防ぐ。

【解決手段】計算機モジュール110及びI/Oモジュール120の中継バッファ600,601,602,603は、それぞれPCIeインターフェース161,162の信号振幅を判断して信号とノイズを区別し、出力信号のON/OFFを制御するノイズフィルタ回路を有する。I/O HUB300及びPCIeスイッチ400は、通信モードに応じて、中継バッファのノイズフィルタ回路の有効/無効を切り替え、通信速度が高速の時にはノイズフィルタ回路を無効にする。ケーブル抜去検出回路115,125は、PCIeケーブル151の抜去をI/O HUB300及びPCIeスイッチ400に通知し、PCIのグリッチによるノイズによる誤作動を抑止する。

(もっと読む)

信号処理装置、及び信号伝送方法

【課題】バスシステムにおいて伝送遅延による受信不良を回避することが可能な信号処理装置を提供すること。

【解決手段】第1バスに接続された主機器から供給されるクロック、当該クロックに同期して主機器から送信されるデータを受信する主側受信部、主側受信部でデータが受信された場合に主機器の通信動作を一時停止させる主動作停止部、第2バスに接続された従機器に対し、主側受信部で受信されたクロック及びデータを送信する従側送信部、従側送信部で送信されたクロックに同期して従機器から送信されたデータを受信する従側受信部、従側受信部でデータが受信された場合に主機器の通信動作を再開させる主動作再開部、主動作再開部により通信動作が再開された主機器から供給されるクロックに同期して従側受信部で受信されたデータを主機器に送信する主側送信部を備える信号処理装置が提供される。

(もっと読む)

1 - 20 / 57

[ Back to top ]