Fターム[5B062AA08]の内容

マイクロコンピュータ (2,258) | 目的、効果 (507) | 誤動作防止 (111)

Fターム[5B062AA08]に分類される特許

1 - 20 / 111

電子制御装置

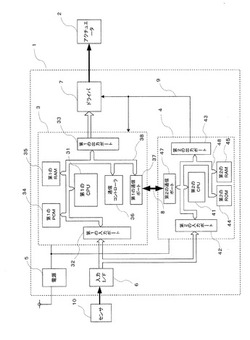

【課題】第1のマイコンの異常を第2のマイコンにより確実に監視することが出来る電子制御装置を提供する。

【解決手段】少なくとも2個のマイクロコンピュータを有し、第1のマイクロコンピュータ(3)が主に制御対象の制御を司り、第2のマイクロコンピュータ(4)が、主に第1のマイクロコンピュータ(3)の異常の監視を行なうように構成された電子制御装置であって、第1マイクロコンピュータ(3)は、自身が制御量の演算に用いるデータの少なくとも一部を、自身の演算リソースを用いずに第2のマイクロコンピュータ(4)に送信するように構成され、第2のマイクロコンピュータ(4)は、送信されたデータに基づいて第1のマイクロコンピュータ(3)の異常の有無を判断するように構成されている。

(もっと読む)

電子制御装置

【課題】複数の割込みが優先順位により実行されることを回避する。

【解決手段】エンジンの制御装置6は、パルス信号の立下りエッジと立上りエッジとの間の時間により回転方向を判定する。立下りエッジの割込で立下り処理(12)が実行され、立上りエッジの割込で立上り処理(13)が実行される。これらの割込は、他の処理(14)の実行中は、キュー処理部(15)に格納され待たされる。キュー処理部(15)は、割込処理の優先順位に応じて割込処理を格納するから、立下り処理(12)と立上り処理(13)とが逆の順序で格納されることがある。フラグ設定部(16)と比較部(17)とは、同じ処理が連続して実行されることを判定する。この判定に応答して、キュー修正部(18)は、立下り処理(12)と立上り処理(13)とが割込み時刻の順序で交互に実行されるようにキュー処理部(15)の内容を修正する。

(もっと読む)

マイクロコンピュータ

【課題】入力信号に特定方向の有効エッジが発生すると、その時の時刻情報を記憶する時刻記憶レジスタを備えたマイコンにおいて、所定のモニタ開始時からCPUが時刻記憶レジスタの値を読み込む処理を行う時までのモニタ期間中に有効エッジが複数回発生しても、有効エッジが最初に発生した時の時刻情報をCPUが取得可能にする。

【解決手段】マイコンでは、CPUによりキャプチャモードレジスタの値が“1”に設定されると(S101:Y)、入力信号に検出対象のエッジが発生した時に、キャプチャイネーブルレジスタの値が“0”の場合だけ(S104:Y)、キャプチャレジスタがフリーランニングタイマの値を更新記憶し(S102)、その更新記憶が行われるとソフト処理に拘わらずキャプチャイネーブルレジスタの値が“0”から“1”になる(S103)。また、キャプチャイネーブルレジスタの値はCPUのソフト処理で“0”に書き換え可能である。

(もっと読む)

集積回路装置、処理システム、電子機器、及び集積回路装置のモード切替方法

【課題】プログラム等の変更をする際の誤った設定による誤動作を防止することができる集積回路装置等を提供する。

【解決手段】集積回路装置100は、1又は複数のモード設定端子102と、通常プログラムを記憶するROM130と、電源投入時において1又は複数のモード設定端子102により起動モードが設定されたとき、通常プログラムの少なくとも一部を修正プログラムに置き換えるための記憶エリアを有するRAM130と、起動モードから通常モードに変更された後、RAM130に記憶され、通常プログラムの少なくとも一部に置き換えられた修正プログラムを実行するCPU120とを含む。

(もっと読む)

半導体装置

【課題】安定に動作する半導体装置を提供する。

【解決手段】このマイクロコンピュータは、主電源端子T1と電源ノードN1の間に接続されたスイッチS1と、補助電源端子T2と電源ノードN1の間に接続されたスイッチS2とを備え、主電源端子T1の電圧V1と参照電圧VR1とを比較し、V1>VR1の場合はスイッチS1をオンさせるとともにスイッチS2をオフさせ、V1<VR1になった場合は、スイッチS1をオフさせるとともに、電源ノードN1の電圧V3が徐々に上昇するようにスイッチS2をオン/オフさせる。したがって、V3をV1からV2に切換える場合でも、V3によって駆動されるクロック発生回路9は安定に動作する。

(もっと読む)

プロセッサシステム及び半導体集積装置

【課題】処理速度の低下を最低限に抑えかつ従来技術に比較して消費電流の変動を抑える。

【解決手段】プロセッサシステム1は、プログラムメモリ2に格納された複数の命令コードを任意の順序で連続して実行する。テーブルメモリ53は、各命令コードと各命令コードの実行時の消費電流量との関係を示す消費電流量テーブルを格納する。電流変動抑制回路51は、消費電流量テーブルを参照して、連続する2つの命令コードの実行時の消費電流量の差の大きさが所定のしきい値以下になるように、上記連続する2つの命令コードのうちの一方の命令コードの実行時にプロセッサシステム1に流す補正消費電流を算出し、上記算出された補正消費電流量の補正消費電流をプロセッサシステム1に流すように、補正消費電流発生回路54を制御する。

(もっと読む)

リセット回路及びマイコン搭載装置

【課題】マイコン搭載装置への電源供給遮断時にもマイコンにリセットをかけられるようにする。

【解決手段】電子制御装置1では、電源入力ライン17へのバッテリ電圧(Vbat)から電源回路19がマイコン21用の電源電圧(以下、VS)を生成する。そしてリセット回路2は、マイコン21のリセット端子25をVSにプルアップする抵抗27と、VSの立ち上がり時にマイコン21にパワーオンリセットをかける回路29とに加え、オンすることで抵抗27の上流側にVSを供給するMOSFET51と、抵抗の上流側とグランドとの間に接続された抵抗52と、電源入力ライン17とMOSFET51のゲートとの間に接続された駆動用の抵抗53とを備える。そして、電源入力ライン17へのバッテリ電圧が遮断されると、VSがマイコン21の最低動作電圧Vminまで低下するよりも前に、MOSFET51がオフしてリセット端子25が抵抗52により0Vとなる。

(もっと読む)

半導体集積回路及び半導体集積回路の動作制御方法

【課題】温度が高くなりすぎたりあるいは低くなりすぎたりする発振状態となって、半導体集積回路が誤動作、動作停止等することを防止する。

【解決手段】実施形態によれば、半導体集積回路1は、回路部の温度又は動作速度に基づいて、温度が安定するように、回路部の制御パラメータを調整して、フィードバック制御を実行する制御部と、温度の時系列データである第1の履歴データと、制御パラメータの時系列データである第2の履歴データとを含む履歴データを格納する履歴レジスタ17と、履歴データからフィードバック制御の有効性を判定する有効性判定部24とを有する。

(もっと読む)

状態保持回路における状態保全性の検証

【課題】 本発明は、データ処理動作を行うよう構成されたデータ処理回路を備えたデータ処理装置を提供する。

【解決手段】 複数の状態保持回路がデータ処理回路の一部を形成し、これらの回路は、低電力モードに入ったデータ処理回路のそれぞれのノードにてそれぞれの状態値を保持するよう構成される。1以上のスキャンパスは、状態値がそれぞれのノードにスキャンインまたはアウトされてもよいよう、複数の状態保持回路を直列に接続する。複数のパリティ情報生成要素はスキャンパスに結合され、状態保持回路によってそれらそれぞれのノードにて保持されたそれぞれの状態値を示すパリティ情報を生成するよう構成される。複数のパリティ情報生成要素は、それぞれの状態値の一つが変化した場合にパリティパスの出力にて生成された出力パリティ値を反転するよう、1以上のパリティパスを提供し、状態保持回路によって保持された状態値の保全性の外部指示を提供するよう配置される。

(もっと読む)

デュアルパスマルチモード順次記憶素子

【課題】デュアルパスマルチモード順次記憶素子

【解決手段】本明細書では、デュアルパスマルチモード順次記憶素子(SSE)(10)が説明されている。一実施例では、デュアルパスマルチモードSSEは、第1(14)および第2(12)の順次記憶素子、データ入力、データ出力ならびに選択機構(16)を備えている。第1および第2の順次記憶素子(14、12)は、それぞれ、入力および出力を有する。データ入力は両方の順次記憶素子の入力に結合され、データを受け入れるように構成される。データ出力は両方の順次記憶素子の出力に結合され、データを出力するように構成される。選択機構(16)は、データ入力からのデータをデータ出力に渡すために、順次記憶素子のうちの1つを選択するように構成される。一実施例では、第1の順次記憶素子はパルストリガー式記憶素子(14)を備えており、第2の順次記憶素子はマスタースレーブ記憶素子(12)を備えている。

(もっと読む)

制御装置

【課題】複数のCPUコアを用いて構成される複数のシステムの中から異常状態のシステムを選択的にリセットするための技術を提供する。

【解決手段】マルチコアマイコン1の3つのCPUコア11〜13を用いて構成される3つのシステムの中から、異常状態のシステムが異常監視部40によって検出されると、異常状態のシステムを識別可能なリセット要求信号がリセット部50によって出力される。そして、3つのシステムで動的に共有される周辺機能部30は、周辺機能部30を利用しているシステムと、リセット要求信号に基づき識別される異常状態のシステムが一致することを条件としてリセットされる。このため、周辺機能部30が、正常なシステムによって利用されている状態においてリセットされないようにすることができる。

(もっと読む)

制御装置

【課題】複数のCPUコアを用いて構成される複数のシステムの中から異常状態のシステムを選択的にリセットするための技術を提供する。

【解決手段】マルチコアマイコン1の3つのCPUコア11〜13を用いて構成される3つのシステムの中から、異常状態のシステムが異常監視部40によって検出されると、異常状態のシステムを識別可能なリセット要求信号がリセット部50によって出力される。そして、3つのシステムで静的に共有されるメモリ20は、3つのシステムのそれぞれに割り当てられた3つの記憶領域21〜23のうち、リセット要求信号に基づき識別される異常状態のシステムに割り当てられた記憶領域がリセットされる。このため、正常なシステムによって利用されている記憶領域までリセットされないようにすることができる。

(もっと読む)

自動リセット回路、自動リセット方法、プログラム、自動リセット装置および情報端末

【課題】 MPUを用いることなく、ハードウェアリセットに依らなければ回復不可能な異常発生の際に、ハードウェアリセットを実施しシステムを回復する自動リセット回路を提供する。

【解決手段】 電源電圧確定回路5が、電源電圧確定信号14を出力し、リセット信号出力手段2が、タイマー1から出力されるタイマー信号11により起動してリセット信号10を出力し、リセット信号出力制御手段4が、コンピュータ起動時に、リセット信号出力手段2を制御し、ファームウェア6が、リセット信号出力制御手段4を稼働させ、タイマー1の初期化とタイマー設定を行いタイマー信号11を無効化し、割り込み検出回路7が、コンピュータ稼働中に、タイマー1の時間の経過により割り込み処理の実行を検出して出力した割り込みハンドラー起動信号13を受けて、割り込みハンドラー6が起動し、タイマー1の初期化とタイマー設定を行い、タイマー信号11を無効化する。

(もっと読む)

自己診断回路および自己診断方法

【課題】マイクロコンピュータの自己診断の実行時間を削減する。

【解決手段】リセット後の動作がホットスタートかコールドスタートかを判定する手段と、各機能ブロックで発生するエラーが他のどの機能ブロックへ影響があるのかの関連付け情報を保持し、通常動作時に発生したエラーがどのブロックで発生したエラーであるかを判定し、複数の機能ブロックからBISTを実行する機能ブロックを選択する手段と、選択された機能ブロックのBISTを実行する順序を関連付け情報に基づいて制御して、BISTの実行を指示する手段と、を備え、ホットスタートと判定された場合には、BISTを実行する機能ブロックを選択するとともに、選択した機能ブロックのBISTを実行する順序を関連付け情報に基づいて制御してBISTを実行し、コールドスタートと判定された場合には複数の機能ブロックのすべてのBISTを実行する。

(もっと読む)

マイクロコンピュータ

【課題】1つのDMAコントローラが複数の処理手段に共用されるようになっているマイクロコンピュータにおいて、異なる処理手段に割り当てられた記憶領域同士の間でDMA転送が行われてしまう誤アクセスを防止する。

【解決手段】1つのDMAコントローラ37が2つのプロセッサエレメント(PE)1,2に共用されるマイコン40には、記憶領域のうち、どの記憶領域がどのPEに割り当てられているかを示す割当テーブルを記憶するレジスタ41が設けられている。そして、DMAコントローラ37は、DMA要求を受けると、その要求が示すデータ転送元の記憶領域が割り当てられているPEと、その要求が示すデータ転送先の記憶領域が割り当てられているPEとを、上記割当テーブルから特定して、その特定した両方のPEが一致していないと判定した場合には、データの転送処理(DMA転送)を実施しないようになっている。

(もっと読む)

信号処理装置

【課題】従来よりもノイズに妨害されることなく入力信号から値を読み取る。

【解決手段】信号処理装置Aは、外部からデジタル信号dsを受信する入力端子1と、異なる複数のサンプリング周期を合わせてデジタル信号dsの値を読み取る入力信号読み取り部5とを具備する。

(もっと読む)

マイクロコンピュータ

【課題】処理負荷の増大を抑制しつつ、処理結果の正確性を確保すること。

【解決手段】複数の命令実行手段を備え、該複数の命令実行手段について故障診断を行う機能を有するマイクロコンピュータであって、プログラムメモリに格納された命令を取得し、該取得した命令を解読する命令取得解読手段と、該命令取得解読手段により解読された命令に基づき、前記複数の命令実行手段に命令を発行すると共に、命令の発行先を特定する発行先特定情報を所定の記憶手段に書き込む命令発行手段と、を備え、前記複数の命令実行手段のうち、前記発行先特定情報が前記所定の記憶手段に書き込まれた命令実行手段について故障診断を行い、前記発行先特定情報が前記所定の記憶手段に書き込まれていない命令実行手段については故障診断を行わないことを特徴とする、マイクロコンピュータ。

(もっと読む)

マイクロプロセッサ

【課題】書き換え不能なメモリに格納した割り込み処理プログラムを変更できることを目的とする。

【解決手段】複数種類の割り込みで処理する複数のプログラムのアドレスをベクタ毎に格納した第1割り込みベクタテーブルと、第1割り込みベクタテーブルの各ベクタの示すアドレスに処理プログラムを格納する領域とを第1メモリ13に設け、第1割り込みベクタテーブルと同一内容の第2割り込みベクタテーブルを第2メモリ14に設け、第1割り込みベクタテーブルをアクセスするアドレスを第2割り込みベクタテーブルをアクセスするアドレスに変換するアドレス変換手段22を有し、外部機器30から供給される命令により、第2割り込みベクタテーブルの任意ベクタのアドレスと任意ベクタの示すアドレスに格納する処理プログラムとを第2メモリ14に書き込む書き込み手段43を有する。

(もっと読む)

内部クロック周波数制御回路及びこれを利用する半導体装置

【課題】半導体装置の外部から入力されるコマンド(命令)及びアドレスのセットアップ/ホールドマージンを増加させることができる内部クロック周波数制御回路及びこれを利用する半導体装置を提供する。

【解決手段】本発明は、モードレジスタセット制御信号を受信してモードレジスタセット信号を出力するモードレジスタセットと、モードレジスタセット信号がイネーブルされて外部クロックと同一の周波数のデータ処理用クロックの予め設定された周期が経過するとイネーブル信号を生成する遅延部と、イネーブル信号がイネーブルされると外部から入力される同期命令をデコーディングして分周開始信号を生成する分周命令デコーダと、分周開始信号に応答して外部クロックと同一の周波数の選択クロックを出力するか、または、外部クロックより周波数が低いクロックを選択クロックとして出力する分周選択部とを含む。

(もっと読む)

半導体装置及び半導体装置におけるリセット制御方法

【課題】外部からのリセット要求が入力されたとき、同期してリセット信号を出力するか、非同期でリセット信号を出力するかを、動作ステートに応じて適切に切り替えることができるようにする。

【解決手段】直列接続された複数の保持部を有するリセット要求保持部に外部からのリセット要求を保持し、リセット切替部が複数の保持部の出力のすべてを論理積演算して非同期リセット要求とするとともに複数の保持部の最終段の保持部の出力を同期リセット要求として非同期リセット要求と同期リセット要求を論理積演算して演算結果を出力するとともに、同期リセットモードでは非同期リセット要求をマスクし、リセット切替部での演算結果に基づいてリセット出力部よりリセット信号を出力する。

(もっと読む)

1 - 20 / 111

[ Back to top ]