Fターム[5B062HH01]の内容

マイクロコンピュータ (2,258) | クロック、電源、リセット (407) | クロック (124)

Fターム[5B062HH01]の下位に属するFターム

クロック周波数の制御 (61)

Fターム[5B062HH01]に分類される特許

1 - 20 / 63

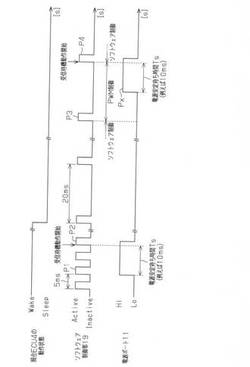

IC出力ポート切換制御装置

【課題】電源を省電力化することができるIC出力ポート制御装置を提供する。

【解決手段】ワイヤレスキーシステムの照合ECU4は、自身のメモリに記憶されたプログラムにて所定周期で動作するソフトウェア制御部19と、自身に元から備わるPWMリソースとを有する。照合ECU4のスリープ中、車両受信機が受信待機動作をとるパルスP4の1周期前のパルスP3で電源ポート11をソフトウェア制御からPWM制御に変更することにより、電源ポート11をPWM制御に切り換える。このため、PWM制御のパルスPxがHiレベルに立ち上がってからの時間が電源安定待ち時間Tsとして車両受信機に供給される。

(もっと読む)

マイクロコンピュータおよびフィールド機器

【課題】マイクロコンピュータの回路規模の単純化を図りつつ、消費電力を低減させることを目的とする。

【解決手段】本発明のマイクロコンピュータは、信号処理を行う複数の機能ブロック4を有するマイクロコンピュータ1であって、クロックCLKを生成するクロック生成部3と、機能ブロック4のうち1つの機能ブロック4−1に備えられ、他の機能ブロック4が使用可能な共通レジスタ13に入力または出力されるデータをクロックCLKの供給が停止されたときにも保持する出力データ保持部14および入力データ保持部15と、各機能ブロック4のうち動作を行う機能ブロック4のみにクロックCLKを供給するようにスイッチ制御を行うコントロールブロック2と、を備えている。

(もっと読む)

デュアルパスマルチモード順次記憶素子

【課題】デュアルパスマルチモード順次記憶素子

【解決手段】本明細書では、デュアルパスマルチモード順次記憶素子(SSE)(10)が説明されている。一実施例では、デュアルパスマルチモードSSEは、第1(14)および第2(12)の順次記憶素子、データ入力、データ出力ならびに選択機構(16)を備えている。第1および第2の順次記憶素子(14、12)は、それぞれ、入力および出力を有する。データ入力は両方の順次記憶素子の入力に結合され、データを受け入れるように構成される。データ出力は両方の順次記憶素子の出力に結合され、データを出力するように構成される。選択機構(16)は、データ入力からのデータをデータ出力に渡すために、順次記憶素子のうちの1つを選択するように構成される。一実施例では、第1の順次記憶素子はパルストリガー式記憶素子(14)を備えており、第2の順次記憶素子はマスタースレーブ記憶素子(12)を備えている。

(もっと読む)

半導体集積回路装置およびその制御方法

【課題】確実にスリープモードに設定することが可能な半導体集積回路装置およびその制御方法を提供する。

【解決手段】まず、第1の値に設定された第1のイネーブル信号を演算部に供給し、演算部を通常動作モードより消費電力が小さいスリープモードに設定する。次に、第1の期間経過後に第1のイネーブル信号が第1の値であるか否かを判定し、第1の値である場合、第2の値に設定された第2のイネーブル信号をメモリに供給し、メモリをスリープモードに設定する。次に、第2の期間経過後に第2のイネーブル信号が第2の値であるか否かを判定し、第2の値である場合、第3の値に設定された第3のイネーブル信号をアナログ回路に供給し、アナログ回路をスリープモードに設定する。次に、第3の期間経過後に第3のイネーブル信号が第3の値であるか否かを判定し、第3の値である場合、第4の値に設定された第4のイネーブル信号をレギュレータに供給し、レギュレータをスリープモードに設定する。

(もっと読む)

半導体装置及び自動車用コントロールシステム

【課題】電源遮断後も、PLL発振状態からの遷移か、PLL自走からの遷移かの識別を可能にする。

【解決手段】電源供給状態から電源遮断状態に遷移された後に再び電源供給状態に復帰される第1領域(12)と、上記第1領域の電源遮断にかかわらず、電源電圧が保持される第2領域(13)と、上記第1領域に供給される第1クロック信号を形成する発振器(11)とを含んで半導体装置(1)を構成する。上記第1領域はPLL回路を含む。上記第2領域には、上記PLL回路の動作モードがPLL発振モードであるかPLL自走モードであるかを識別可能な情報を保持可能な情報保持部を設け、上記第1領域が電源遮断状態から電源供給状態に復帰した際の上記PLL回路の動作モードを、上記情報保持部の保持情報に従って決定する。

(もっと読む)

半導体装置

【課題】検知対象クロックと検知用クロックの周波数比を容易に調整できるようにする。

【解決手段】検知用クロックで動作するカウント値が変更可能なカウンター部でのカウント完了時にレベル出力部より出力される信号の信号レベルを反転させ、その信号レベルの変化が検知対象クロックで動作するクロック検知部を通過したか否かをレベル出力部の出力信号とクロック検知部の出力信号の信号レベルを比較することで判定し検知対象クロックの停止を検知する。

(もっと読む)

半導体装置及び半導体装置におけるリセット制御方法

【課題】外部からのリセット要求が入力されたとき、同期してリセット信号を出力するか、非同期でリセット信号を出力するかを、動作ステートに応じて適切に切り替えることができるようにする。

【解決手段】直列接続された複数の保持部を有するリセット要求保持部に外部からのリセット要求を保持し、リセット切替部が複数の保持部の出力のすべてを論理積演算して非同期リセット要求とするとともに複数の保持部の最終段の保持部の出力を同期リセット要求として非同期リセット要求と同期リセット要求を論理積演算して演算結果を出力するとともに、同期リセットモードでは非同期リセット要求をマスクし、リセット切替部での演算結果に基づいてリセット出力部よりリセット信号を出力する。

(もっと読む)

マイクロコントローラ及びその制御方法

【課題】低消費電流で動作する構成が求められている。

【解決手段】入力データが入力されると、前記入力データに応じて起動要求信号を出力するデータ入力部と、前記起動要求信号に応じて起動し、クロック信号を生成する発振器と、前記データ入力部からの前記起動要求信号を前記発振器に出力し、起動後に生成される前記発振器からのクロック信号を、前記データ入力部の動作クロック信号である第1のクロック信号と、第2のクロック信号として供給するクロック信号供給制御部と、前記第2のクロック信号を動作クロックとして動作し、その動作時に前記入力データに応じた処理を行うCPUと、を有するマイクロコントローラ。

(もっと読む)

マイクロコンピュータ

【課題】解除条件を伴う低消費電力モードであっても、割込要求に対応することができ、より効果的に低消費電力化すること。

【解決手段】解除条件を伴う停止命令を実行して第1の停止状態へ移行する第1のCPU101と、第1のCPU101と少なくとも周辺回路とを接続するバス102と、第1の停止状態である期間に、クロックに応じてバスのバス情報を読み出し、バス情報と解除条件とが一致した場合、第1のCPU101の停止を解除するための解除要求信号を出力する監視制御回路107と、を備えるマイクロコンピュータ。第1の停止状態である期間に、周辺回路から第1のCPU101へ割込要求があった場合、第1のCPU101は、動作状態へ移行して割込処理を終了させた後、第1の停止状態へ戻り、監視制御回路107は、第1のCPU101が当該割込処理中、バス情報の読み出しを一時的に中断する。

(もっと読む)

マイクロコンピュータ及び画像表示装置

【課題】LCDダイレクトドライブのための制御にハードウェアを用いることで、ユーザプログラム作成の負担軽減を図る。

【解決手段】クロック信号を形成可能なタイマパルスユニット(103)と、表示用データを液晶ディスプレイへDMA転送可能なDMAコントローラ(110)と、上記DMA転送に用いられる第1クロック信号と、上記液晶ディスプレイへの表示に用いられる第2クロック信号とを選択的に上記液晶ディスプレイのクロック入力端子へ伝達可能なセレクタ(105)とを設ける。また上記セレクタの選択状態を設定可能なレジスタ(106)と、上記レジスタの設定情報に基づいて、上記セレクタの選択状態を上記DMA転送に同期して制御するための制御論理(107)とを設ける。ユーザプログラムにおいては、LCDダイレクトドライブのための制御に関して上記レジスタへの設定を行うだけで良いので、ユーザプログラム作成の負担を軽減できる。

(もっと読む)

半導体集積回路および電子情報機器

【課題】半導体集積回路において、スタンバイモードからの復帰時間を短くでき、スタンバイモードからの復帰のための不揮発性メモリなどの付加的な回路は不要で余分なコストが発生しないという利点を維持したまま、スタンバイモードにおける電源電圧をさらに下げることでリーク電流を抑えた低消費電力動作を実現する。

【解決手段】半導体集積回路100において、複数の内部回路のうちの主要なコア回路の動作モードを、通常動作モードとスタンバイモードとの間で切り替えるモード切替回路108と、該モード切替回路に該スタンバイモードを解除するよう指示するスタンバイ解除要因検出回路107とを備え、該モード切替回路108及び該スタンバイ解除要因検出回路107を、該スタンバイモードでのスタンバイ電圧により該システムクロックとは非同期で動作するよう構成した。

(もっと読む)

マイクロコンピュータ

【課題】CPUが、例え、低消費電力モード中に外来ノイズの影響を受けたとしても外部信号端子はハイインピーダンス状態となっているので、その端子によって外部デバイスが駆動されることはなく、信頼性を向上する。

【解決手段】端子制御手段は、CPUが低消費電力モードに移行する場合に出力するコマンドに応じて、外部信号端子42に接続される出力バッファ43Aをハイインピーダンス状態に設定するための信号を出力する。そして、前記出力信号は、前記CPUが動作している期間に前記外部信号端子42を制御するために出力されるポート制御信号と共に、論理ゲート41を介して前記出力バッファ43Aに与えられる。

(もっと読む)

半導体装置及びデータ処理システム

【課題】中央処理装置が設定した低消費電力状態の解除に伴う電力消費と処理時間を短縮することができ、且つ、中央処理装置が既に設定した低消費電力状態の強制解除と復帰との関係の制御を容易に行うことができる半導体装置を提供する。

【解決手段】中央処理装置(41)自らに対して、そして被制御回路(12,22)に対して、電源及びクロックの停止と供給を制御する低消費電力のための制御機構に、所定の被制御回路から出力される電源及びクロックの停止を要求する信号(400)が要求する期間だけ、別の被制御回路に対して既に設定されている電源及びクロックの供給停止を強制解除する、強制解除制御回路(70)を採用し、強制解除に中央処理装置を介在させることを要さず、また、所定の被制御回路からの要求が終われば元の低消費電力状態に復帰されるようにする。

(もっと読む)

マルチコアプロセッサ及びこれを用いる車載電子制御装置

【課題】各コアの動作周波数を時系列で適切に変動させることで、放射ノイズ等の問題点を少なくとも部分的に解決すること。

【解決手段】 本発明は、複数のコアを搭載したマルチコアプロセッサ1,2であって、複数のコアA,B,Cは、同一の周期Tで周期的に周波数が変動する動作クロックで動作するように構成され、コアの動作クロックの周波数の変動位相が、前記複数のコア間でずらされることを特徴とする。好ましくは、各コアの動作クロックの周波数の変動位相は、時間T/N(Nはコア数)に相当する位相ずつずらされる。好ましくは、コアの動作クロックの周波数の変動態様は、複数のコア間で、変動位相が異なる以外は同一である。

(もっと読む)

マルチプロセッサ装置

【課題】同一チップ上に複数のマルチプロセッサを含む場合、異なるアーキテクチャごとに独立したバスと外部バスI/Fを持つことで、高性能のマルチプロセッサを得ることを目的とする。

【解決手段】本発明におけるマルチプロセッサ装置は、例えばCPU1〜8、SIMD型超並列プロセッサ31,32、DSP41,42のようにアーキテクチャの異なる第1,第2のプロセッサ群を含む複数のプロセッサと、第1のプロセッサ群が接続されているCPU10バスである第1のバスと、第2のプロセッサ群が接続されて第1のバスとは独立した内部周辺バス14である第2のバスと、第1のバスが接続されている第1の外部バスI/Fと、第2のバスが接続されている第2の外部バスI/Fとを一の半導体チップ上に備える。

(もっと読む)

マイクロコンピュータ

【課題】ダブルデータレート(DDR)方式のシンクロナスDRAMを高速アクセス可能なマイクロコンピュータを提供する。

【解決手段】中央処理ユニット、メモリ制御手段、及びクロック制御部を有するマイクロコンピュータは、クロック制御部から供給されたクロックを外部クロックとしてマイクロコンピュータの外部に出力し、外部クロックを反転したクロックをマイクロコンピュータの外部に出力する。メモリ制御手段は、前記クロックに対応し、第1の電位状態と第2の電位状態とに遷移するデータストローブ信号を生成する。メモリ制御手段によって制御されるメモリは、データストローブ信号の立ち上がりエッジと立ち下がりエッジに同期してデータの入出力を行うDDR方式の同期型メモリである。メモリ制御手段は、同期型メモリにデータを書き込むとき、前記データストローブ信号の立ち上がりエッジと立ち下がりエッジに同期してデータを外部に出力する。

(もっと読む)

半導体集積回路装置

【課題】外部のデバイスに接続される回路とLSI内部の回路との間におけるタイミング設計を不要とすること。

【解決手段】半導体集積回路装置は、外部デバイスに対して接続されるインタフェース回路であって第1のクロック信号が供給される第1の回路と、第1のクロック信号を分周した第2のクロック信号が供給される第2の回路と、第2のクロック信号を第1のクロック信号に基いて遅延させた送受信タイミング信号を生成するタイミング生成回路と、第2の回路から受信した信号を第1のクロック信号に同期してサンプリングする複数段のシフトレジスタと該複数段のシフトレジスタに対する入出力信号に含まれるハイレベルの信号とロウレベルの信号の多数決を送受信タイミング信号に同期して行うとともに多数決により決定された信号を第1の回路に出力する多数決回路とを有する第1の位相調整回路とを備えている。

(もっと読む)

半導体集積装置およびその制御方法

【課題】複数の機能ブロックのうち1以上を選択し、当該選択した機能ブロックをリセットする半導体集積装置および半導体集積装置の制御方法を提供する。

【解決手段】本発明にかかる半導体集積回路20は、クロック信号35及びリセット信号36が供給されることでリセットされる機能ブロック24と、機能ブロック24をリセットするリセット信号36を出力するリセット信号出力部21と、機能ブロック24に供給するクロック信号35を停止するクロックマスク回路23と、クロックマスク回路23を制御するクロックマスク制御回路22を有する。

(もっと読む)

マイクロコンピュータ

【課題】 CPUのスリープ状態時に、CR発振回路が生成する低速且つ周波数ばらつきの大きいクロックに基づき動作する起動タイマを備えるマイクロコンピュータにおいて、正確なスリープ期間を判定することができる半導体集積回路を提供する。

【解決手段】 CR発振回路が生成するクロックを、分周比が選択可能な分周回路に入力し、分周比を設定するとともに、水晶発振回路が生成するクロックにより基準期間信号を生成し、分周回路からのクロック信号出力の1周期と、基準期間信号との比から、起動時間設定レジスタ値の補正を行う手段を備える。

(もっと読む)

マイクロコンピュータ及びマイクロコンピュータシステム

【課題】CPUのクロックが停止しているスリープモードにおいて出力端子のレベルを変える機能を有するマイクロコンピュータにおいて、出力端子のレベルを変えるまでの時間と出力端子のレベルを変えてからスリープモードを解除するまでの時間を自在に設定できるようにする。

【解決手段】CPUと、CPUのスリープモードの設定と解除を制御するスタンバイ制御部と、出力端子と、第1のタイマと、前記CPUがスリープモードのときに第1のタイマがあらかじめ定められた計時を行うと、スリープモードを保ったまま、出力端子のレベルを変える出力端子制御部と、スリープモードにおいて出力端子制御部が出力端子のレベルを変えるときに計時を開始する第2のタイマと、を備え、スタンバイ制御部は、第2のタイマが所定の計時を行うとCPUのスリープモードを解除する。

(もっと読む)

1 - 20 / 63

[ Back to top ]