Fターム[5B077AA18]の内容

Fターム[5B077AA18]に分類される特許

1 - 20 / 34

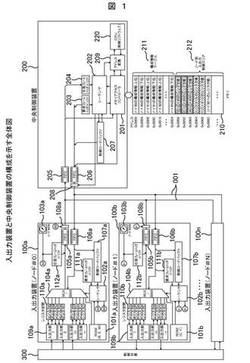

制御システムおよび制御システムのメモリ制御方法

【課題】本発明は、入出力装置と中央制御装置間の通信を効率的に行い、制御速度等の運用効率を向上させる制御システムおよび制御システムのメモリ制御方法を提供することを目的とする。

【解決手段】中央制御装置と、制御対象との間でデータの入出力を行う複数の入出力装置と、を備え、前記複数の入出力装置それぞれは、前記制御対象との間で入出力するデータを一時記憶する一時記憶手段を有する制御システムにおいて、前記複数の入出力装置は、前記制御対象との間で入出力を行うための所定の領域を示す構成情報を記憶し、前記複数の入出力装置は、前記構成情報が示す領域を選択してデータを読み出すとともに、当該読み出したデータを前記中央制御装置へ送信し、または、前記中央制御装置からデータを受信するとともに、前記構成情報が示す領域を選択して当該受信したデータを書き出すことを特徴とする制御システム。

(もっと読む)

デバイスシステムおよびチップ

【課題】拡張性のよいシステムを提供する。

【解決手段】マスター(プロセッサー52a)は送信先のスレーブ(SDRAMコントローラー34)の識別情報S1と自身の識別情報M3とを格納してリクエストを送信し、ルーター57は識別情報S1に基づいてポートP56にリクエストを転送し、チップリンク58,39を介してリクエストを受信したルーター37は識別情報S1に基づいてポートP33にリクエストを転送する。スレーブは識別情報M3を格納してレスポンスを送信し、ルーター37は識別情報M3に基づいてポートP35にレスポンスを転送し、チップリンク39,58を介してレスポンスを受信したルーター57は識別情報M3に基づいてポートP51にレスポンスを転送する。これにより、マスターやスレーブ,各ルーターは、チップ内の通信と同様な処理でチップ31,47間の通信を行なうことができる。

(もっと読む)

クロック同期式シリアル通信装置およびその通信制御方法

【課題】マスターデバイスと複数のスレーブデバイスとがシリアルデータ通信を行う場合に、通信対象とするスレーブデバイスの指定時に生じる通信オーバーヘッドを削減すること。

【解決手段】クロック同期式シリアル通信装置は、クロック信号の周波数を調整するとともに、周波数が調整されたクロック信号およびデータ信号を出力するマスターデバイスと、前記マスターデバイスから出力されたクロック信号およびデータ信号を受信するとともに、受信したクロック信号の周波数を計測する複数のスレーブデバイスとを備え、

前記複数のスレーブデバイスは、それぞれ、識別用の周波数を保持し、計測した周波数と該識別用の周波数とが一致したか否かに応じて、前記マスターデバイスから出力されたデータ信号を保持または破棄する。

(もっと読む)

データ転送制御装置、データ転送制御方法、及びそのためのプログラム

【課題】 パケット交換網を介して記憶装置間のデータ転送を行う記憶装置において、転送するデータがアドレス境界条件を満たしていない場合に、転送するデータのメモリアクセス性能を低下させないようにする。

【解決手段】 送信側転送開始アドレスと受信側転送開始アドレスとを少なくとも含むデータ転送命令に基づいて、送信側メモリアクセス単位で転送データを読み出すことを送信側メモリに要求する、データ読出要求を出力する転送命令実行部と、

送信側転送開始アドレスと受信側転送開始アドレスと受信側メモリアクセス単位とデータを送信側から受信側へ転送する際の転送パケットサイズに基づいて、データ読出要求に応答して送信側メモリから出力された転送データを、受信側メモリアクセス単位の境界で分割して転送パケットを生成し、出力する転送パケット生成部と、を含む。

(もっと読む)

シリアル伝送システム及びそれに用いるに適したスレーブユニット

【課題】省配線化を達成し得るコピー装置及びプリンタ装置等に用いるシリアル伝送システムを提供する。

【解決手段】シリアル伝送システム1は、複数の動作指示手段を格納したスレーブIC群、当該スレーブIC群のうち少なくとも第一及び第二のスレーブICを制御するに要するマスターIC21、当該第一及び第二のスレーブIC内、または、近接して配置され、当該マスターICが出力発信した情報が自己に宛てられたものであるどうかを判断する判断手段40、当該マスターICに接続され、当該第一及び第二のスレーブICにシリアル的に情報を伝達する主バス配線10、当該主バス配線から第一の電子コンポーネントを動作させる為の情報を第一のスレーブICにシリアル的に伝送するに要する受動的な第一分岐手段51、及び当該主バス配線から第二の電子コンポーネントを動作させる為の情報を第二のスレーブICにシリアル的に伝送するに要する受動的な第二分岐手段52とを備える情報のシリアル伝送システムとして構成される。

(もっと読む)

マルチインターフェースメモリカードとその動作方法

【課題】マルチインターフェースメモリカードの動作方法を提供する。

【解決手段】ホストから入力された電圧レベルを検出して電圧レベル情報を生成させる段階と、ホストから入力されたリセット信号に応答して、電圧レベル情報を解析する段階と、解析結果によって、第1インターフェースと第2インターフェースとのうち、何れか一つをイネーブルさせる段階と、を含むマルチインターフェースメモリカードの動作方法。

(もっと読む)

データ送信システムおよびデータ送信プログラム

【課題】ハードウェアコストを増大させずにホストCPUの処理負担を軽減させて、効率的にデータ転送を行えるようにする。

【解決手段】データ送信システムは、プロセッサ2と、格納されたデータをブロック単位でI/Oバス上に送信するデータ記録装置4と、I/Oバスに接続されてプロセッサ2に代行して所定の通信プロトコル処理を行うプロトコル処理装置5と、を備える。プロセッサ2は、データ記録装置4から送信されるべきデータをブロック単位で特定するデータ特定部21と、プロトコル処理装置5のアドレス情報を指定して、データ記録装置4からプロトコル処理装置5へのデータ転送を指示する転送指示部23と、を有する。プロトコル処理装置5は、データ記録装置4からブロック単位でI/Oバスに送信されたデータを、主記憶装置を経由せずに直接受け付けるデータ受付部51と、データ受付部51で受け付けたブロック単位のデータをパケット単位でネットワークに送信するネットワーク処理部53と、を有する。

(もっと読む)

通信システム、マスター装置、及びスレーブ装置、並びに通信方法

【課題】マスター側デバイスの負担を低減すること。

【解決手段】通信システムは、マスター装置とスレーブ装置とを有する。スレーブ装置は、送信すべきデータが発生した場合に、マスター装置に送信要求を表すリクエスト信号を生成するリクエスト信号生成部と、マスター装置に、前記リクエスト信号を送信する送信部とを有する。マスター装置は、スレーブ装置からのリクエスト信号を受信するリクエスト信号受信部と、該リクエスト信号に応じて、送信させるべきスレーブ装置を選択する選択部と、該選択スレーブ装置に、データ送信が許可されたことを表す信号を送信する送信部と、選択スレーブ装置からのデータを受信するデータ受信部とを有する。

(もっと読む)

中継装置およびプロセッサーシステム

【課題】先入れ先出し方式のバッファーをより適切に構成して効率的にリクエストを中継する。

【解決手段】転送元であるマスターデバイス30側からのリクエストの分配を行なうTブリッジ42と、Tブリッジ42から分配されたリクエストを転送先であるスレーブデバイス80側に転送するIブリッジ46とを備えて通信を中継するクロスバースイッチ40において、Tブリッジ42のT−B0内に各スレーブデバイスの共用のFIFO43aを構成し、Tブリッジ42とIブリッジ46との間に各スレーブデバイスの専用のFIFO45a〜45cを構成するから、転送先のスレーブデバイスが受け入れ可能な状態になくリクエストの転送待ちが生じる場合であっても、他のスレーブデバイスに転送されるリクエストが転送待ちとなるのを減少させることができる。

(もっと読む)

情報処理装置、及びデータの転送方法

【課題】データ転送路の信頼性を高めつつシステムとしての可用性を向上させる情報処理装置、及びデータの転送方法を提供する。

【解決手段】ルートノードから複数のノードにツリー状に分岐しつつその間を通信可能に接続するデータ転送路を有し、前記ルートノードと前記複数のノードとの間でシリアルデータ伝送が行われる情報処理装置であって、前記複数のノードのうちの少なくとも1組のノード間に設けられた、前記シリアルデータ伝送が行われる2本のノード間データ転送パスと、前記ノード間データ転送パスの両端にある前記ノードである端末ノードにそれぞれ設けられており、各前記端末ノードが他方の前記端末ノードを介して送信先である前記ノードのいずれかに送信元である他の前記ノードのいずれかから受信したデータを転送する場合に、前記送信先のノードから前記送信元のノードへの返信データを、前記送信先のノードへのデータ転送に使用した前記ノード間データ転送パスと同一の前記ノード間データ転送パスを使用して実行するルーティング処理部とを備えている

(もっと読む)

端末装置及びそのUSB機器制御方法

【課題】 本発明は、上記問題を解決するためのものであり、本発明の目的とするところは、外部機器に接続されたUSB機器が使用できる端末装置及びそのUSB機器制御方法を提供することにある。

【解決手段】 外部機器に接続される端末装置が開示される。本装置は、データチャネルを含む通信インターフェースを介して外部機器に接続されるインターフェース部、外部機器とUSB機器の接続状態がインターフェース部を介して通知されると、USB機器の使用を要請するクエリーを外部機器に伝送する通信部及びクエリーに対応して、外部機器から伝送されるUSB機器情報を保存する保存部及び保存されたUSB機器情報に対応されるドライバプログラムを実行させ、データチャネルを介してUSB機器にアクセスする制御部を含む。これにより、外部機器に接続されたUSB機器を制御できるようになる。

(もっと読む)

USB装置

【課題】USB接続される外部記憶機器に対してUSB接続されるホスト機器からのデータの読み書きを簡易な構成で可能にする。

【解決手段】メモリーカードが挿入されたときには(S110)、USBDeviceに対してカードの接続を有効なものとしてリムーバブルメディアが接続されたことを示す「Unit Attention」がホスト機器であるPCに送信されるよう設定してPCからのアクセスを許可し(S130,150,160)、ストレージ機器としてメモリーカードと同一のプロトコルを用いてアクセス可能なダイレクトアクセスデバイスが接続されたときには(S120)、USBDeviceに対してストレージ機器の接続を有効なものとしてメモリーカード挿入時と共通の応答である「Unit Attention」がPCに送信されるよう設定してPCからのアクセスを許可する(S140〜160)。

(もっと読む)

出力回路および転送制御方法

【課題】複数のメモリ間でデータを転送する場合に、オーバーフローによるデータの破棄を防ぐ。

【解決手段】本願の開示する技術は、データを記憶する複数の一次メモリと、各一次メモリに記憶されたデータを集約して出力する一つの2次メモリと、に記憶されたデータの蓄積量に応じて、各一次メモリに記憶されたデータを2次メモリに転送する転送制御部を備える。そのため、出力回路は、各1次メモリおよび2次メモリに記憶されたデータの量を考慮して、各一次メモリから2次メモリへデータの転送を行うので、各メモリのオーバーフローを防止し、データの破棄を防止することができる。

(もっと読む)

データ入出力装置

【課題】FIFOモジュールが出力すべき順序でレスポンスを出力できるようにする。

【解決手段】レスポンス出力ルーチンが実行されると、FIFOモジュール最先に格納したレスポンスである先頭レスポンスの順序情報が予め記憶した順序ガイド値と一致するか否かを判定することで、先頭レスポンスが次に出力すべきレスポンスであるか否かを判定する(ステップS100)。そして、肯定的な判定をしたときには、順序ガイド値を1インクリメントして(ステップS110)、先頭レスポンスを出力する(ステップS120)。一方、否定的な判定をしたときには、新たなレスポンスをFIFOモジュールが格納するレスポンス入力処理中であればレスポンス入力処理が終了するまで待ち(ステップS130)、FIFOモジュールの先頭レスポンスを出力して再格納する(ステップS140)。このルーチンを繰り返すことにより、レスポンスを出力すべき順序で出力できる。

(もっと読む)

集積回路

【課題】容易に機能拡張が可能な集積回路を提供する。

【解決手段】ASIC1は、外部CPU3からデータを受信するコマンドIF10と、コマンドIF10により受信されたデータの宛先を特定する第1リストを記憶する記憶部11と、記憶部11に記憶された第1リストに基づいて、コマンドIF10により受信されたデータの宛先が自己宛であるか又はASIC2であるかを判別する判別部12と、ASIC2宛のデータをASIC2に送信するコマンドIF15とを備えている。

(もっと読む)

シリアルデータ伝送方法およびそのシステム

【課題】マスター装置から出力すべき信号線数を増大させることなく、且つシリアルデータのビット数を増すことなく、マスター装置から複数のスレーブ装置に対してシリアルデータを選択的に伝送できるようにする。

【解決手段】マスター装置は、伝送すべき相手側スレーブ装置のスレーブアドレスに応じてストローブ信号STBのパルス幅を切り替える。スレーブ装置では、ストローブ信号STBのパルス幅を測定するとともに、そのパルス幅に応じたスレーブアドレスと自身のスレーブアドレスとが一致するか否かを検知し、一致する時に、シリアルデータ信号SDATAおよび同期クロック信号SCKによって取り込んだ所定ビット数のデータを確定する。

(もっと読む)

ストリームデータ再生システム

【課題】入出力バッファとの間のデータ転送に係るDSPの処理負荷を軽減する。

【解決手段】ストリームソースから入力されたストリームデータを蓄積する入力バッファと、前記入力バッファに蓄積された前記ストリームデータを所定の処理単位毎にデコードしてデコードデータを生成するデコードコア回路と、前記デコードデータを蓄積した後に出力する出力バッファと、を有したストリームデータ再生システムにおいて、前記デコードコア回路と接続され、前記入力バッファに蓄積された前記ストリームデータ及び前記デコードコア回路において生成された前記デコードデータを記憶する転送用メモリセルと、前記入力バッファから前記転送用メモリセルへの前記ストリームデータの前記処理単位毎の転送並びに前記転送用メモリセルから前記出力バッファへの前記デコードデータの前記処理単位毎の転送を制御するデータ転送制御回路と、を有することとする。

(もっと読む)

インタフェース方法及びデータ処理システム

【課題】複数のデータ処理装置を接続したシステムにおいて、データの転送速度を高速化する。

【解決手段】送信を行うインタフェース回路を有する第1のデータ処理装置と、受信を行うインタフェース回路を有する第2のデータ処理装置と、転送すべきデータを保持する記憶装置とを備えるデータ処理システムにおいて、データの転送を行うインタフェース方法であって、前記記憶装置における前記転送すべきデータを示すアドレス情報を、前記第1のデータ処理装置のインタフェース回路から前記第2のデータ処理装置のインタフェース回路に通知するアドレス通知ステップと、前記第2のデータ処理装置が、前記アドレス情報に基づいて前記記憶装置にアクセスし、前記転送すべきデータを読み出すデータ読み出しステップとを備える。

(もっと読む)

シリアルデータ転送装置及びシリアルデータ転送方法

【課題】 シリアルデータ転送に使用する信号数を最小限に抑え、データ転送するデバイスが増加しても信号線数が増加しないシリアルデータ転送装置を実現することを目的とする。

【解決手段】 マスターシリアルインタフェース回路と、該マスターシリアルインタフェース回路によりデバイス選択され、シリアルデータ信号により指定されたアドレスのデータを読み出し/書き込みする複数のスレーブシリアルインタフェース回路とを備えたシリアルデータ転送装置において、シリアルデータ信号がスタート信号とデバイス選択信号を含むように構成することにより、シリアルデータ転送に使用する信号線がクロック用とデータ用の2線のみとなるようにした。

(もっと読む)

デバイス装置および接続制御方法

【課題】ホスト装置とデバイス装置から構成され、接続について、デバイス装置からアクションを起こすシステムにおいて、接続に際しての利便性を提供する。

【解決手段】ホスト装置と無線接続して使用されるデバイス装置において、ホスト識別情報保持部は、ホスト装置の識別情報を保持する。デバイス装置の接続制御部は、ホスト装置に接続するための探索であって、ホスト装置から発信されるホスト識別情報を含む識別信号の探索を、成功するまで所定の時間間隔毎に探索を行わせる。ホスト装置は、ワイヤレスUSB(WUSB:WirelessUniversalSerialBus)ホスト装置とすることができる。この場合、接続制御部は、ワイヤレスUSBホスト装置からのMMC(Micro−scheduled Management Command)の探索を行わせる。

(もっと読む)

1 - 20 / 34

[ Back to top ]