Fターム[5B077BA02]の内容

情報転送方式 (3,847) | 処理装置間の情報転送 (462) | 通信用バッファを介した転送 (155)

Fターム[5B077BA02]に分類される特許

1 - 20 / 155

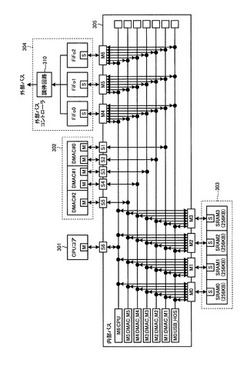

アクセス制御装置、画像形成装置およびアクセス制御方法

【課題】複数の内部モジュールから異なる外部バス空間へ同時に書き込みアクセスがあった場合に、内部バスが待ち状態になる頻度を低下させ、内部バスのパフォーマンスを向上させること。

【解決手段】アクセス制御装置は、内部バス305と、外部デバイスとのデータの送受信を行うための外部バスと、外部バスを制御する外部バスコントローラ304と、を備え、外部バスコントローラ304は、外部デバイスに対応して設けられ、内部バスからのデータを一時的に保存する複数のFiFo0〜2と、内部バス305からのアクセス要求に対して、複数のFiFo0〜2のうち、外部バスにデータ転送するFiFoの選択を行い、選択されたFiFoに保存されたデータを外部バスに出力する調停回路310と、を備えた。

(もっと読む)

推測的技術を用いるメッセージベースのネットワークインターフェースのためのプロセッサ

【課題】メッセージネットワークインターフェースユニットを提供すること。

【解決手段】メッセージネットワークインターフェースユニットは、プロセッサに連結されており、プロセッサがプロセッサによって生成された複数のメッセージをハードウェアユニットに送信することを可能にし、メッセージネットワークインターフェースユニットは、プロセッサによって生成された複数のメッセージのうちの少なくもと1つのメッセージの引数を格納するように動作可能な伝送レジスタであって、少なくとも1つのメッセージが推測的に生成される、伝送レジスタと、伝送レジスタに連結されており、複数のメッセージをキューに入れるように動作可能なキューであって、動作は、メッセージネットワークインターフェースユニットがトリガーメッセージを受信することに応じてキューにおいて実行される、キューとを含む。

(もっと読む)

集積回路装置及びその制御方法

【課題】USBホストコントローラを有する集積回路装置において消費電力を削減する。

【解決手段】集積回路装置は、USBを介してUSBデバイスとの間で通信を行うUSBホストコントローラと、通常動作状態において、前記USBホストコントローラを制御して、前記USBホストコントローラと前記USBデバイスとの間の通信が可能になるようにするための処理を行い、スタンバイ状態において動作を停止する第1プロセッサと、前記スタンバイ状態において、前記USBホストコントローラを制御して、前記通常動作状態に移行するための処理を行い、前記通常動作状態において動作を停止する第2プロセッサとを有する。前記USBホストコントローラと前記USBデバイスとの間で通信可能な状態を維持したまま、前記USBホストコントローラに対する制御が、前記第1プロセッサによる制御と前記第2プロセッサによる制御との間で切り替えられる。

(もっと読む)

デバイスコントローラ、USBデバイスコントローラ及び電力制御方法

【課題】バッファを効率的に使用し、バッファに蓄積されたデータ量に基づいて電力制御を行うことができるデバイスコントローラ、デバイス装置及び電力制御方法を提供すること

【解決手段】本発明にかかるデバイスコントローラ20は、ホスト装置40から出力されたデータを蓄積する入力バッファと、ホスト装置40へ出力するデータを蓄積する出力バッファと入力バッファ及び出力バッファと、ホスト装置40との間のデータの受け渡しを行うデータ通信部と、入力バッファ及び出力バッファの少なくとも一方に蓄積されているデータ量に基づいて、入力バッファ及び出力バッファに対するバッファの割当量を変更させるデータバッファコントロール部25とを備える。データバッファコントロール部25は、データ量が所定の値に達した場合にデータ通信部を通常電力モードから省電力モードへ遷移させる。

(もっと読む)

制御システムおよび制御システムのメモリ制御方法

【課題】本発明は、入出力装置と中央制御装置間の通信を効率的に行い、制御速度等の運用効率を向上させる制御システムおよび制御システムのメモリ制御方法を提供することを目的とする。

【解決手段】中央制御装置と、制御対象との間でデータの入出力を行う複数の入出力装置と、を備え、前記複数の入出力装置それぞれは、前記制御対象との間で入出力するデータを一時記憶する一時記憶手段を有する制御システムにおいて、前記複数の入出力装置は、前記制御対象との間で入出力を行うための所定の領域を示す構成情報を記憶し、前記複数の入出力装置は、前記構成情報が示す領域を選択してデータを読み出すとともに、当該読み出したデータを前記中央制御装置へ送信し、または、前記中央制御装置からデータを受信するとともに、前記構成情報が示す領域を選択して当該受信したデータを書き出すことを特徴とする制御システム。

(もっと読む)

マイクロコンピュータ

【課題】通信ネットワークに接続されるものにつき、簡単で且つ低コストで実現できる構成で、ホストによる処理効率の低下を防止できるマイクロコンピュータを提供する。

【解決手段】CPU2と通信モジュール3との間に、CPU2が直接アクセスを行う読み出しバッファ9,及び書き込みバッファ8と、通信要求を周期的に出力することで通信モジュールが他のノードより受信したデータを読み出しバッファに転送する読み出し制御部11と、書き込みバッファ8に書き込まれているデータを送信データとして通信モジュール3に転送する書き込み制御部8aとを備える。また、CPU2が通信モジュール3との間で直接データの読み書きを行うように制御するバイパスアクセス制御部7と、読み出し,書き込み,バイパスアクセスの各制御部6,7,8aによる通信モジュール3へのアクセス順序を制御するアクセス順序制御部10とを備える。

(もっと読む)

キャッシュ制御方法、キャッシュ制御装置およびキャッシュ制御用プログラム

【課題】受信したデータをキャッシュメモリに書き込んで処理を行う場合に、大量のデータを受信する状況であっても、処理性能が低下することを抑制できるキャッシュ制御方法を提供する。

【解決手段】領域設定手段81は、予め定められた量の受信データを書き込み可能な領域である書き込み領域をキャッシュメモリに設定する。領域削除手段82は、書き込み領域に書き込まれた一部または全部の受信データに対する処理ごとに、その処理の対象になった受信データが書き込まれた領域を削除する。また、領域設定手段81は、受信データに対する処理ごとに、予め定められた量の受信データを受信した後に受信する受信データを書き込む位置に、受信データを書き込み可能な領域として、削除された領域に相当する量の領域を新たに設定する。

(もっと読む)

データ転送装置及びデータ転送方法

【課題】データ転送時の待ち時間を減らすこと。

【解決手段】データ転送装置20の分割サイズ算出部21は、各バッファ12a,12bの分割サイズBsa,Bsbを、互いに他のバッファのデータ蓄積量に基づいて算出する。例えば、バッファ12bのデータ蓄積量Dsbに基づいて、バッファ12bにしきい値Bib以上のデータが蓄積されるまでのデータ蓄積時間を予測し、そのデータ蓄積時間に応じて、バッファ12aから転送するデータの分割サイズBsaを算出する。分割転送制御部23a,23bは、分割サイズBsa,Bsbとデータ蓄積量Dsa,Dsbに応じて、各バッファ12a,12bに対する転送指示Tba,Tbbを発行する。転送制御部25は、転送指示Tbs(転送指示Tba,Tbb)に応じて、各バッファ12a,12bから装置14にデータを転送する。

(もっと読む)

データ転送制御装置及び方法並びにデータ処理装置

【課題】転送されるデータに転送が完了されるべき時間である締切時間が設定される場合、例えば、優先度が低いデータであって、比較的締切時間が近いデータの場合でも、データ転送の締切時間に応じた転送スケジュールでデータの転送を行い、締切時間内に転送が行われるようにする。

【解決手段】データ転送制御装置は、データを入力する複数の入力ポートと、データを出力する出力ポートと、データに設定される締切時間に基づいて、データを複数の入力ポートから出力ポートに転送する転送制御部とを備える。

(もっと読む)

データ処理装置

【課題】 階層化されたバス構造をもつマルチマスタバスシステムにおいては、データを書き込む経路と読み出す経路によっては、書き込むマスタが共有メモリデバイスからのライト応答を待たずに、もう一方の読み出すマスタに通知し、データを読み出しても、ライトトランザクションとリードトランザクションの実行順序は保証されることがある。それにも関わらず、いつも共有メモリデバイスからのライト応答を待つことは不必要に性能を損なう。

【解決手段】 階層化されたバス構造をもつマルチマスタバスシステムにおいて、2つのマスタ間で共有メモリを介してデータの受け渡しを行う際に、データを書き込む経路と読み出す経路に応じて、最適なスレーブがライト応答を生成することで、ライトアクセスとリードアクセスの順序保証をする。

(もっと読む)

非同期FIFO間順序制御回路、データ処理装置及びそれらに用いる非同期FIFO間順序制御方法

【課題】 実装面積を抑えた上で、入力された要求の処理順序を効率的に組み替えることが可能なデータ処理装置を提供する。

【解決手段】 データ処理装置は、第1のクロック信号に同期して動作するインタフェース(11)と、それとは異なる第2のクロック信号に同期して動作する記憶装置制御回路(16)とを備え、第1及び第2のクロック信号の非同期クロック間において要求を受け渡すための非同期FIFO[優先度が高く先行する要求を追い越すことが可能な要求を格納するための第1の非同期FIFO(13)、優先度が低く先行する要求を追い越すことが不可能な要求を格納するための第2の非同期FIFO(14)]と、強制されるべきオーダー関係を管理するための情報を付与する書込み制御手段(12)と、強制されるべきオーダー関係を考慮した上で効率的に処理順序を組み替える読出し制御手段(15)とを有する。

(もっと読む)

転送装置、転送方法および転送プログラム

【課題】メモリに格納された情報に対する処理を効率的に実行させる。

【解決手段】転送装置1は、メモリに格納された情報に対する処理の要求を記憶する複数の記憶部A2〜C4を有する転送装置である。また転送装置1は、要求を第一の装置から受信した場合には、受信した要求を解析し、要求された処理の対象となるデータが格納されたメモリアドレスを内包するアドレス範囲を特定する。そして、転送装置は、特定されたアドレス範囲ごとに異なる記憶部A2〜C4に要求を格納する。また、転送装置は、格納された要求が第二の装置によって実行されているか否かを記憶部ごとに判別する。そして、転送装置は、格納された要求が実行されていないと判別された記憶部に格納した要求を第二の装置へ送信する。

(もっと読む)

携帯装置、通信システムおよび転送方法

【課題】自装置が有する記憶装置の容量を補完することが可能な携帯装置、通信システムおよび転送方法を提供する。

【解決手段】コンテンツデータを提供するコンテンツサーバと記憶サーバとのそれぞれと、通信を行う携帯装置は、記憶部と、コンテンツサーバからコンテンツデータを受信する無線部と、無線部がコンテンツデータを受信したときの記憶部の空き容量が、コンテンツデータを記憶部に記憶するのに必要な容量よりも小さい場合には、コンテンツデータを記憶サーバ宛てに転送する処理部と、を含む。

(もっと読む)

通信装置

【課題】デバイスとの通信速度を適正にして無駄な電力消費を抑えることができる通信装置を提供する。

【解決手段】USB3.0での接続が確立後に、CPU16が、メモリーカードコントローラ3から転送スピード情報を取得してファンクション情報バッファ部15に保持させて、CPU16では、ファンクション情報バッファ部15に保持された転送スピード情報に基づいて、USB3.0のスーパースピードが適正なのかUSB2.0のハイスピードが適正なのかを決定して、USB2.0のハイスピードが適正と決定された場合は、US側、DS側ともにUSB2.0のハイスピードに切り替える。

(もっと読む)

バッファ管理装置、同装置を備えた記憶装置、及びバッファ管理方法

【課題】コマンドの実行が滞ってもバッファ転送効率が低下するのを防止する。

【解決手段】実施形態によれば、中間FIFOは、送信FIFOまたは受信FIFOとバッファとの間で転送されるデータを格納する、テーブルは、ホストからのデータ転送コマンド毎に、当該コマンドで指定された、送信FIFOまたは受信FIFOとバッファとの間のデータ転送を管理するためのバッファ転送情報を保持する。第1のシーケンサは、テーブルに保持されているバッファ転送情報に基づいて、対応するコマンドで指定されたデータ転送のためのバッファ転送を、少なくとも1つのフレームを単位に起動する。第2のシーケンサは、バッファ転送の起動に応じて、送信FIFOまたは受信FIFOと中間FIFOとの間でフレーム単位でデータを転送する。第3のシーケンサは、バッファ転送の起動に応じて、中間FIFOとバッファとの間でセクタ単位にデータを転送する。

(もっと読む)

アクセス制御方法及び周辺装置

【課題】排他処理を無くしてシステム全体の効率を向上させることを可能とした周辺装置へのアクセス制御方法及びそのような周辺装置を提供すること。

【解決手段】CPU100による周辺装置300からのデータの読み出しサイクルにおいて、周辺装置300を特定するためのアドレスに加えて周辺装置300のバッファ303に書き込む書き込みデータを、アドレスバス201を介して送信する。バッファ303への書き込みデータの書き込み結果を示す状態データを読み出しデータとしてデータバス202を介して読み出す。

(もっと読む)

CPU間通信システム及びCPU間通信方法

【課題】CPU間通信において、同期の待ち時間に応じてウェイト処理を最適に制御できるようにする。

【解決手段】送信側CPUと受信側CPUとがメモリ104を介してデータ通信を行うCPU間通信システム800において、送信側CPUは、メモリ104に空き領域があるかを判定するメモリ領域判定部351と、空き領域がある場合に、メモリ104にデータを書き込むデータ書き込み部352と、空き領域がない場合に、受信側CPUの状態を判定する受信側CPU判定部353と、受信側CPUの状態がデータ読み出し処理の実行状態である場合に、メモリ104に空き領域ができるまでデータ書き込み部352を待ち状態とし、受信側CPUの状態がデータ読み出し処理の実行状態でない場合に、受信側CPUにデータ読み出し処理の実行を開始させるための読み出し開始要求を受信側CPUへ送信する送信側制御部354とを備える。

(もっと読む)

情報処理装置

【課題】エンディアンの異なる他の情報処理装置との間で通信フレームを用いて複数のデータを送受信する場合にエンディアン変換全体に要する処理時間を短縮する情報処理装置を提供することを課題とする。

【解決手段】他の情報処理装置との間で通信フレームを用いて複数のデータを送受信する情報処理装置であって、エンディアンの異なる他の情報処理装置に通信フレームを送信する前にエンディアン変換を行う場合又は/及びエンディアンの異なる他の情報処理装置からの通信フレームを受信した後にエンディアン変換を行う場合、通信フレームとバイト並びを反転させた反転バッファを生成することを特徴とし、反転バッファにおける各データのバイト位置を通信フレームのバイトサイズから通信フレームにおける各データのバイト位置とデータのサイズに応じたバイト数を減算した位置とする。

(もっと読む)

中継装置およびプロセッサーシステム

【課題】先入れ先出し方式のバッファーをより適切に構成して効率的にリクエストを中継する。

【解決手段】転送元であるマスターデバイス30側からのリクエストの分配を行なうTブリッジ42と、Tブリッジ42から分配されたリクエストを転送先であるスレーブデバイス80側に転送するIブリッジ46とを備えて通信を中継するクロスバースイッチ40において、Tブリッジ42のT−B0内に各スレーブデバイスの共用のFIFO43aを構成し、Tブリッジ42とIブリッジ46との間に各スレーブデバイスの専用のFIFO45a〜45cを構成するから、転送先のスレーブデバイスが受け入れ可能な状態になくリクエストの転送待ちが生じる場合であっても、他のスレーブデバイスに転送されるリクエストが転送待ちとなるのを減少させることができる。

(もっと読む)

メモリシステム及びそのデータ転送方法

【課題】メモリシステムの回路面積を縮小する。

【解決手段】メモリシステム10は、データ部に対して誤り訂正のためのパリティビットを生成するECCエンコーダ17と、ページ単位でデータを格納する不揮発性メモリ11と、パリティビットを用いてデータ部の誤りを訂正するECCデコーダ18と、不揮発性メモリ11から読み出されたページ、或いはECCエンコーダ17から転送されたフレームを一時的に格納する第1のメモリバッファ15と、パリティビットが付加される直前のデータ部、或いはECCデコーダ18により誤りが訂正されたデータ部を一時的に格納する第2のメモリバッファ19と、不揮発性メモリ11及び第2のメモリバッファ19間のデータ転送を制御し、かつデータコピー動作時に第1のメモリバッファ15をシリアルにアクセスするデータ転送制御部22とを含む。

(もっと読む)

1 - 20 / 155

[ Back to top ]