Fターム[5B077GG02]の内容

情報転送方式 (3,847) | タイミング制御 (384) | タイミング制御の目的 (147) | 非同期信号のサンプリング (56)

Fターム[5B077GG02]の下位に属するFターム

不安定状態/雑音の除去 (35)

サンプリング時間の短縮化

Fターム[5B077GG02]に分類される特許

1 - 20 / 21

データ転送システム、データ転送方法、受信回路、及び受信方法

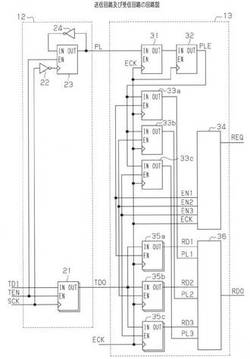

【課題】連続したデータの転送を可能とすること。

【解決手段】送信回路12は、データTDOを出力する毎に、ポール信号PLのレベルを反転する。受信回路13は、リードリクエスト信号REQに応答してポール信号を複数のタイミングで受け取るとともに、送信データTDOを複数のタイミングで受け取る。そして、受信回路13は、タイミングが異なる複数のポール信号に基づいて、受け取った複数のデータのうちの1つと等しい受信データRDOを出力する。

(もっと読む)

データ転送システム、データ転送装置及びデータ転送方法

【課題】設計自由度を向上させることのできるデータ転送システム、データ転送装置及びデータ転送方法を提供する。

【解決手段】第1転送装置10から第2転送装置20への転送データTDの送信の際に信号レベルが切替えられる送信状態信号Tsと、第2転送装置20での転送データTDの受信の際に信号レベルが切替えられる受信状態信号Rsとの一致・不一致を、第1転送装置10の論理回路15及び第2転送装置20の論理回路24の双方で比較する。これら論理回路15,24における比較結果に応じて、第1転送装置10での新規のデータ信号D1の取り込みと、第2転送装置20での転送データTDの受信とを交互に許可する。

(もっと読む)

サンプリング位相を補正するホストコントローラ及び方法

【課題】 転送データの信頼性向上ならびにエラー対処性能の向上を実現する。

【解決手段】 一実施形態は、外部機器から受信した信号をサンプリングする際のサンプリングクロックの位相シフト補正を行うホストコントローラ10であって、前記サンプリングクロックの位相シフトが必要か判定し、位相シフトが必要な場合は、シフト方向に応じてカウンタ108をアップ/ダウンカウントする位相シフト判定部107と、前記位相シフトの変動範囲制限値を格納する制限値格納部109と、前記カウンタ値が前記位相シフトの制限値を超えているか判定し、超えている場合にエラーの通知を可能とし、超えていない場合に、前記カウンタ108のカウンタ値に応じて、前記サンプリングクロックの位相をシフトするシフト制限判定部110とを具備する。

(もっと読む)

非同期統合アップサイジング回路

【課題】システムオンチップに採用するのに適する非同期統合アップサイジング回路を提供する。

【解決手段】非同期統合アップサイジング回路は非同期パッカーと非同期アンパッカーを具備する。非同期パッカーは、非同期ブリッジ及びアップサイジングに共通で用いられ、ライトチャンネルデータをバッファリングするライトバッファと、バーストライト時に前記ライトバッファに入出力される前記ライトチャンネルデータに対するチャンネル圧縮を第1及び第2クロックによって各々制御する第1及び第2非同期パッキング制御器を含む。また、非同期アンパッカーは、前記非同期ブリッジ及びアップサイジングに共通で用いられ、リードチャンネルデータをバッファリングするリードバッファと、バーストリード時に前記リードバッファに入出力される前記リードチャンネルデータに対するチャンネル圧縮を前記第1及び第2クロックによって各々制御する第1及び2非同期アンパッキング制御器を含む。

(もっと読む)

半導体装置

【課題】複数のマスタやスレーブを接続する場合のインターコネクトを低レイテンシ及び低コストで実現する。

【解決手段】データ転送に使用される第1インタフェース(201,301)と、データ転送の競合を調停するための信号の伝達に使用される第2インタフェース(202,302)とを含んで転送系回路(13)を形成する。上記第1インタフェースは、パラレル形式のデータをシリアル形式に変換するパラレル・シリアル変換回路(132,142)を含む。上記パラレル・シリアル変換回路の出力データの転送速度は、上記第2インタフェースにおける信号伝達速度に比べて高速に設定される。上記第2インタフェースは、上記複数の送信側回路からのデータ転送の競合を調停するアービタ(133,143)を含む。上記アービタによる調停後に、上記第1インタフェースを介して多量のデータを転送可能にする。

(もっと読む)

非同期バス・インタフェース回路

【課題】マイクロプロセッサにはバス・アクセスのためのバス・アクセス・ウエイトを最小とし、一連の連続バス・アクセス動作が書き込み動作、読み出し動作とも互いに物理的な影響を与えず、各動作を停止させることなく連続非同期バス・アクセスを正常に実行することができる非同期バス・インタフェース回路を提供する。

【解決手段】アドレスを一時保存し、出力するライト・アドレス・バッファ114と、データを一時保存し、出力するライト・データ・バッファ116と、ライト・イネーブル信号を生成し、出力するライト制御回路115と、を備え、ライト・イネーブル信号がイネーブルのとき、ライト・アドレス・バッファ114から出力されるアドレスとライト・データ・バッファ116から出力されるデータとを、内部レジスタ102に書き込む。

(もっと読む)

半導体集積回路、データ処理方法、画像形成装置

【課題】シングルポートの記憶装置を用いて非同期の連続書き込み及び連続読み出しを行うことが可能な半導体集積回路、データ処理方法、画像形成装置を提供する。

【解決手段】シングルポート記憶装置を用いてFIFO動作を行う半導体集積回路120であって、書き込み用クロック信号と同期して書き込まれたデータを保持するバッファ回路121と、前記書き込み用クロック信号と、前記書き込み用クロック信号と独立して予め設定された読み出し用クロック信号との非同期を吸収する非同期吸収回路122と、前記データを前記読み出し用クロックと同期して前記シングルポート記憶装置へ出力する制御回路と、を有し、前記読み出し用クロック信号に基づき、前記シングルポート記憶装置のワードサイズと、前記書き込み用クロック信号の周波数の範囲とが設定される。

(もっと読む)

第2のリンクを介した内部リンクの観察

【課題】シリコンコンポーネントに集積されるようハードウェアを実装することにより、例えば、他の相互接続を介し、既存の外部インターフェースを用いてMCPからの可視性を提供する。

【解決手段】第1のクロック信号の第1のクロック周期間において、パッケージ内リンクを介し、マルチチップパッケージ(MCP)の第1のダイで受信された当該MCPの第2のダイからの第1のデータをセレクタからの出力用に選択する段階と、第2のクロック周期間において、第2のダイから第1のダイに送信される第2のデータをセレクタからの出力用に選択する段階と、第1のデータおよび第2のデータを外部リンクを介してMCPから送信する段階と、を備える。

(もっと読む)

クロックの異なるバス間におけるデータ転送

【課題】バスネットワークアーキテクチャにおける周辺機器にアクセスするレジスタの遅延を低減する。

【解決手段】低速バスから高速バスへデータを非同期に転送する方法は、上記高速バスのクロック周波数のサイクルにおける第1の所定時点でデータをラッチすることと、上記高速バスのクロック周波数の同一のサイクルにおける第2の所定時点でデータをラッチすることを備え、上記第2および第1の所定時点の間の時間周期は上記データの周期よりも短く、上記第1および第2の所定時点でラッチされたデータの値が等しい場合、上記ラッチされたデータが第3の所定時点で上記高速バスの上へ転送され、または上記第1および第2の所定時点でサンプリングされた値が異なる場合、現在存在するデータの値が上記第3の所定時点で上記高速バスへ転送される。

(もっと読む)

同期化回路

【課題】 同期化回路の無駄なスイッチング動作を回避し、消費電力を低減する。

【解決手段】 同期化レジスタ20および30には、受信レジスタ10が取り込んだデータの下位8ビットデータRD0〜RD7および上位8ビットデータRD8〜RD15が各々与えられる。クロックゲーティング制御回路40は、同期化レジスタ20の入力データおよび出力データの不一致が発生したときのみ同期化クロックCLK2aを同期化レジスタ20に与え、クロックゲーティング制御回路50は、ビット幅指定信号BT8がLレベルであり、同期化レジスタ30の入力データおよび出力データの不一致が発生したときのみ同期化クロックCLK2bを同期化レジスタ30に与える。

(もっと読む)

電力消費量を極めて少なくした疑似同期小型レジスタ設計及びその実施方法

電力消費量を低減させるとともに、クロックドメイン間でデータを転送する複雑性を低減させた1つ以上の疑似同期レジスタを構成及び動作させる方法及び装置を提供する。本発明の種々の実施例によれば、従来の連続的なクロックスキームの代わりに、1つ以上の疑似同期レジスタをもってデータ転送動作を実行する必要がある場合にのみ発生させるストローブ信号を用いる。ストローブ信号は、少なくとも1つの疑似同期レジスタが存在するクロックドメインを規定するクロック信号の1サイクル全体の持続時間を有するように発生させる。  (もっと読む)

(もっと読む)

データ同期装置及びそのデータ同期方法

【課題】従来のデータ同期装置は、サンプリングデータの受信開始後にサンプリングクロックの周波数が大きく変動する問題があった。

【解決手段】本発明のデータ同期装置は、入力データの周波数に読み出しクロックCLKを同期させてデータを出力する、あるいは出力データの周波数に読み込みクロックCLK´を同期させてデータを入力するデータ同期装置であって、読み出しクロックCLK、あるいは読み込みクロックCLK´の周波数を、入力データあるいは出力データの単位時間当たりのデータ量に基づき制御する周波数同期部15を有し、周波数同期部15は、入力データが入力される前の期間に読み出しクロックCLK、あるいは出力データを出力する前の期間に読み込みクロックCLK´の周波数を予め設定された第1の周波数設定値SG1に基づき制御するものである。

(もっと読む)

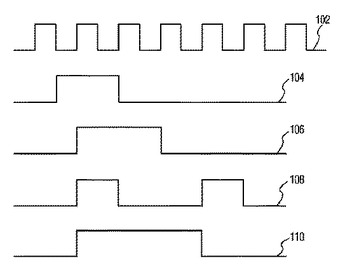

非同期伝送装置、非同期伝送方法

【課題】 同期化処理オーバヘッドを短縮する非同期伝送装置、非同期伝送方法を提供する。

【解決手段】 送信クロックに従って送信される少なくとも1つの通知信号を受信クロックに従って受信する非同期伝送装置であって、通知信号のシンボル周期に基づくトリガ信号を出力するトリガ信号送信部11と、トリガ信号送信部11により出力されるトリガ信号のタイミングに対して所定時間だけタイミングをずらした通知信号を出力する通知信号送信部12と、トリガ信号の同期化を行うと共に、通知信号のサンプリングタイミングを指示するサンプリングタイミング信号を出力するトリガ信号同期化部21と、サンプリングタイミングに従って通知信号を保持する通知信号保持部22とを備えた。

(もっと読む)

非同期バスインタフェース及びその処理方法

【課題】 クロックの周波数が変化しても、十分なアクセス有効期間を確保することができ、また無駄なアクセスウエイト時間をなくすことができる非同期バスインタフェースを提供することを課題とする。

【解決手段】 クロック(CK)に同期して動作する同期デバイス(102)のクロックの周波数情報を入力する入力部と、同期デバイスから非同期デバイス(106)への第1のアクセス信号を入力すると、第1のアクセス信号を基に第2のアクセス信号を生成して非同期デバイスに出力する信号生成部とを有する非同期バスインタフェース(104)が提供される。信号生成部は、クロックの周波数情報に応じて、第2のアクセス信号の有効サイクル数を決定する。

(もっと読む)

ブリッジインタフェースのデータ読み書き方法

【課題】本発明は、互換性が高いことと、容易に、コマンドの流れを変換できることと言う利点等がある、ブリッジインタフェースを提供する。

【解決手段】本発明は、ホストとデバイスとの間において、信号レベルとタイミングを、適当に制御することにより、ブリッジインタフェースが、完全なメッセージハンドシェイクをでき、何れの伝送速度でも、ワークを行い、簡単に、先端にある任意のバスのコマンドの流れを変換できる、ブリッジインタフェースのデータ読み書き方法を提供する。

(もっと読む)

フォールトトレラントコンピュータ及びその制御方法

【課題】 二重化されたシステム間の同期を確実にとることができるとともに、二重化されたシステム間でカウンタがばらばらに動作している状態でも同期をとる。

【解決手段】 システム3aからシステム3bにデータを送信する場合、そのデータの送信時刻を付与して送信する。システム3bにおいては、受信したデータに付与された送信時刻から理想受信時刻を算出し、理想受信時刻と実際の受信時刻とからクロックのずれ量を算出し、この算出結果に基づいてシステム3bのクロックを変更する。

(もっと読む)

マルチファンクションデバイス

【課題】 従来に比べて配線数を減らして省面積でマルチファンクション機能を実現することができるようにしたマルチファンクションデバイスを提供する。

【解決手段】 シリアル・インタフェースを構成するUSBホストコントローラ5とUSBハブ6とを備え、各ファンクション10,20とUSBホストコントローラ5との間で選択的にシリアル信号の中継を行う。これにより、PCIカードとして構成した場合であっても、カード内のバスとしてPCIバスを用いる必要が無くなり、内部バスとしてPCIバスを用いる場合に比べてデバイス内部の配線数を大幅に減らし、省面積でマルチファンクション機能を実現することができる。

(もっと読む)

データ入出力装置、データ入出力システム、及びデータ通信方法

【課題】簡単な構成で、高速動作が可能なデータ入出力を可能にすること。

【解決手段】第1のデータ入出力装置10を、第2のデータ入出力装置20に対してクロックを送信するための送信クロック端子103と、上記クロックのタイミングに同期した送信データを出力する出力タイミング制御回路104を有する送信データ出力部と、上記送信データを上記第2のデータ入出力装置20に対して送信するための送信データ端子107と、上記クロックとは異なる外部クロックを受信するための受信クロック端子110と、上記外部クロックに同期した受信データを上記第2のデータ入出力装置20から入力する入力タイミング制御回路115を有する受信データ入力部と、上記受信データを受信するための受信データ端子116と、を備えるICチップとして構成する。

(もっと読む)

スレーブ回路の動作周波数が変化するシステム

【課題】 スレーブ回路の動作周波数が変化するシステムにおいて、簡易な構成で、マスター回路がスレーブ回路とデータを交換することができるようにする技術を提供する。

【解決手段】 このシステム1は、可変の動作周波数faで動作するスレーブ回路30,40と、基準周波数f0で動作するマスター回路22と、基準クロック信号Sf0を生成してマスター回路に供給し、ローカルクロック信号Sfaを生成してスレーブ回路30,40に供給するクロック信号生成部10と、を備える。クロック信号生成部10は、マスター回路22からの指示に応じて動作周波数faを変えてローカルクロック信号Sfaを生成する。また、クロック信号生成部10は、動作周波数faの情報を含むスレーブ動作信号reqen1,acken1を生成して、マスター回路22に供給する。マスター回路22は、スレーブ動作信号に従って、スレーブ回路とデータの受け渡しを行う。

(もっと読む)

2フェーズデータ転送プロトコル

データ通信装置は、2フェーズプロトコルを用いて、コントローラモジュール(102)と、複数のターゲットモジュール(104)の間で、効率的なデータ転送を可能にする。コントローラモジュール(102)とターゲットモジュール(104)は、それぞれ、個別のクロックドメインに属することができる。一実施形態の例と一致する、データ通信装置は、複数のターゲットモジュール(104)と、第1のデータ完全性表示信号(111)を供給し、ターゲットモジュール(104)のそれぞれからの、それぞれの第2のデータ完全性表示信号(108)に応じるように構成された第1のXORツリー(110)とを含む。第2のXORツリー(112)は、第1のデータバス(114)を供給し、ターゲットモジュール(104)のそれぞれからの、それぞれの第2のデータバス(106)に応じるように構成されている。また、コントローラモジュール(102)を用いて、第1のデータ完全性表示信号(111)に応じて、第1のデータバス(114)でのデータの利用可能性が決定される。  (もっと読む)

(もっと読む)

1 - 20 / 21

[ Back to top ]