Fターム[5B077GG15]の内容

情報転送方式 (3,847) | タイミング制御 (384) | タイミング制御の手段 (230) | 非同期信号サンプリングの制御手段 (104) | 遅延回路 (29)

Fターム[5B077GG15]に分類される特許

1 - 20 / 29

周辺機器

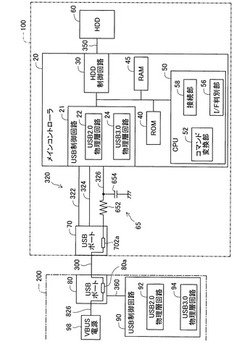

【課題】周辺機器について、コネクタによってホスト機器に物理的に接続された際に、誤ったインターフェースを用いた論理的な接続が形成される可能性を低減する技術を提供する。

【解決手段】周辺機器であって、複数種のインターフェースに対応する複数種のコネクタを選択的に接続可能な単一の接続部であって、コネクタを介してホスト機器から電力の供給を受けるための電源端子を有する接続部と、電力の供給を受けて、ホスト機器との間で複数種のインターフェースのいずれかを用いて論理的な接続を形成するための接続処理を開始する制御部と、制御部と端子とを接続する電源線と、ホスト機器から周辺機器に電力が供給されているにも拘わらず、制御部への電力の供給を所定時間遅延させる遅延処理部であって、電源線の途中に配置された遅延処理部と、を備える。

(もっと読む)

クロック同期化回路及び半導体集積回路

【課題】SoCにおいて、バスマスタとクロック生成回路間の配線が長くなると、CTSバッファやリピータが複数必要になる。その結果、SoC内での遅延ばらつきが増大し、基本クロックCLKとクロック同期化信号CLKENの適正なタイミングを維持することができず、正常なデータの送受信が行なえない。そのため、基本クロックとクロック同期化信号の遅延ばらつきを解消するクロック同期化回路及び半導体集積回路が、望まれる。

【解決手段】図1に示すクロック同期化回路は、基本クロックと、基本クロックとシステムクロックとを同期させる第1の同期化信号と、システムクロックの分周比に関する情報を含む選択信号と、を受け付け、選択信号に基づき第1の同期化信号を所定時間保持し、基本クロックに同期させて、基本クロックとシステムクロックとを同期させる第2の同期化信号を出力する。

(もっと読む)

情報処理装置、情報処理システムおよび情報処理システムの通信方法

【課題】通信速度の高速化を実現可能な情報処理装置、情報処理システムおよびその通信方法を提供する。

【解決手段】例えば、送信側の情報処理装置が送信動作(MWr1)を行い、これに応じて受信側の情報処理装置は、肯定応答(Ack1)を返信したのち、プロセッサ回路CPUを用いてMWr1に伴いバッファ回路BUF上に格納されたパケットデータの取り出しを行う。この際に、受信側は、BUF上のパケットデータの取り出しが完了した(すなわちBUFに空き容量が存在する)ことを意味する「UpdateFC1」を、実際にBUFに空き容量が存在する(BUFが開放される)よりも前の時刻(例えばAck1の直後)で返信する。送信側は、「UpdateFC1」に応じて次の送信動作(MWr2)を行う。

(もっと読む)

データプロセッサ、半導体装置及びデータ処理システム

【課題】外部インタフェースのアナログ特性が異なる複数の外部デバイスに対するクロック同期のデータリードにおける遅延設定が容易で融通性も高く、遅延時間の切換えを高速に行なうことができる外部バスインタフェース機能を備えたデータプロセッサを提供する。

【解決手段】外部データ端子から入力されたリードデータを遅延制御すると共に、遅延制御されたデータのラッチタイミングを制御する外部バスインタフェース制御回路を採用し、ラッチタイミングの制御には、クロック出力バッファを介して外部に出力する内部クロック信号を遅延させる複数の第1遅延回路の出力をチップ選択信号に基づいて選択して前記ラッチ回路のラッチクロックとして与える制御を行い、データ遅延制御には、データ端子から入力されるリードデータを遅延させる複数の第2遅延回路の出力をチップ選択信号に基づいて選択してラッチ回路にラッチするデータとして与える制御を行う。

(もっと読む)

データ受信回路

【課題】データ信号の立ち上がりエッジと立ち下がりエッジとの間の定常的な遅延の差を小さくする。

【解決手段】データ受信回路であって、データを伝送するデータ信号を増幅して出力する増幅回路と、第1の制御信号に従って前記増幅回路の出力を遅延させ、第1の遅延データ信号として出力する第1の遅延回路と、第2の制御信号に従って前記増幅回路の出力を遅延させ、第2の遅延データ信号として出力する第2の遅延回路とを有する。

(もっと読む)

遅延時間調整回路及び遅延時間調整方法並びにコンピュータプログラム

【課題】例えば、信号処理装置―メモリ装置間を接続する線路の線路長が異なっている場合や、基板毎に線路のインピーダンスにバラつきが存在する場合においても、メモリ装置や信号処理装置の受信端における複数の信号各々の受信タイミングの差を無くすこと。

【解決手段】信号処理装置1とメモリ装置2との間で遅延時間測定信号の送受信を行う。遅延時間演算部14は、遅延時間測定信号送信部12と遅延時間測定信号受信部13とからの前記信号の各々を入力信号とし、バス4の線路40〜4n−1毎に各遅延時間を測定し、バス4の線路40〜4n−1に対応する各線路の遅延補正情報を計算する。遅延時間調整部16は、前記遅延補正情報を参照し、バス4の線路40〜4n−1間の信号伝達時間のバラつきが吸収されるように、内部的に備える遅延回路の構成を変更する。

(もっと読む)

データ転送装置及び撮像装置

【課題】 クロック信号に対するデータ信号の遅延調節を高速に行うことができる技術を提供することを目的とする。

【解決手段】 基準信号とともにデータのデータ信号を受信する受信部と、データ信号に対して複数の遅延素子を用いて、それぞれ相異なる遅延量を有する複数の遅延データ信号を所定の基準に基づいて出力する遅延部と、基準信号によって与えられる契機での複数の遅延データ信号の各々の値と基準信号によって与えられる契機においてデータのデータ信号から取得されるべき値の基準となる基準値とを比較し、一致するか否かの判定に基づいて一の遅延量を選択する制御部と、制御部によって選択された一の遅延量を有する遅延データ信号を出力する選択出力部と、を備える。

(もっと読む)

高速データレートインタフェース装置及び方法

【課題】デジタル制御データとデジタルプレゼンテーションデータの事前に選択されたセットを通信するための通信プロトコルを形成するために、共にリンクされるパケット構造を使用して、通信経路上、ホストとクライアントの間でデジタルデータを転送するためのデータインタフェースを提供する。

【解決手段】信号プロトコルは、通信プロトコルを形成するパケットを生成、送信、及び受信し、デジタルデータを1つ又は複数のタイプのデータパケットに形成するように構成され、少なくとも1台が該ホストデバイスに常駐し、該通信経路を通して該クライアントに結合される、リンクコントローラによって使用される。インタフェースは、短距離「シリアル」タイプデータリンクでの、費用効果が高い、低電力の、双方向高速データ転送機構となる。

(もっと読む)

同期型データ転送システムおよび同期型データ転送制御方法

【課題】システムが動作中であっても、さらには、小型化・高速化を要する環境下であっても、安定した同期型データ転送の実現が可能な同期型データ転送システムを提供する。

【解決手段】例えばメモリ2からデータ転送用クロック32に同期させてデータ・バス31aを介してデータを転送する際に、データ転送要求受付後最初のデータをメモリコア22から取り出すまでのデータ出力待ち時間を利用して、遅延時間測定データ格納部23に格納している遅延時間測定データ23a〜23cをデータ・バス31aに送信することにより、制御LSI10の遅延時間測定部12にてデータ・バス31aの遅延時間を測定し、遅延調整制御部17は、測定した遅延時間に基づいて、データ・バス31aを介して転送されてくるメモリコア22からのデータを取り込むためのデータ取り込みタイミングを調整して、メモリコントローラ11に供給する。

(もっと読む)

データ転送装置およびカメラ

【課題】 ノイズ等の影響をより低減しうるデータ転送装置を提供する。

【解決手段】 データ転送装置の送信部は、テストデータを基準信号に同期させて送信する。遅延部は、送信部から送信されたデータ信号の遅延量を基準信号に基づいて調整する。判定部は、遅延量が同じ条件でテストデータを複数回取得し、所定の遅延量でテストデータを取り込んだときの信号値の信頼性を判定する。制御部は、遅延量を変化させながらテストデータを取り込んだ結果に基づいて、正規のデータ通信で適用する遅延量(調整値)を決定する。また、制御部は、取り込んだ信号値のうちで信頼性が高いと判定されたものを用いて、ハイレベルが最も長く連続する第1区間と、ローレベルが最も長く連続する第2区間とをそれぞれ求める。そして、制御部は、第1区間および第2区間に基づいて調整値を決定する。

(もっと読む)

位相調整装置およびカメラ

【課題】 より簡易な構成で、データとクロックとの位相の関係を適切に調整するための手段を提供する。

【解決手段】 位相調整装置は、比較コード生成部と、演算部と、遅延部とを備える。比較コード生成部は、シリアル転送データに含まれる先頭コードの位相を進めた第1比較コードと、先頭コードの位相を遅らせた第2比較コードとをそれぞれ生成する。演算部は、先頭コードおよび第1比較コードの比較結果と、先頭コードおよび第2比較コードの比較結果とを用いて、シリアル転送データの位相の調整方向を求める。遅延部は、位相の調整方向に基づいて、シリアル転送データの遅延量を調整する。

(もっと読む)

通信装置及びそれを有する通信システム並びに通信方法

【課題】新たな信号の追加無く、ホスト装置がディジーチェーン接続されたデバイスに対するデータ転送タイミングを変化させる必要が無い通信装置及びそれを有する通信システム並びに通信方法を提供する。

【解決手段】ディジーチェーンに接続されたデバイス100、200、300において、デバイスID機能部102にデバイス識別番号を設定し、そのデバイス識別番号に応じてレイテンシコントロール103がデバイスからリードする際の遅延値を決定しているので、例えば、デバイス300がホストから一番遠いとすると、ホスト装置10がデバイス300からリードした際の遅延値に合わせてデバイス100とデバイス200のレイテンシコントロール102で遅延値を設定することで各デバイスからのリードする際のレイテンシを同一とすることができる。

(もっと読む)

タイミング調整装置

【課題】温度変化に起因したタイミングのずれによるデータ不一致の発生を抑制

【解決手段】高速揮発性メモリ3にデータを書き込む場合には、CPU温度検出部6にCPU2の温度を検出させて、この検出結果に基づいて、書き込み用DLL14に対してレジスタ設定を行う。これにより、書き込み用DLL14に入力したデータ取り込み信号DQSは、CPU2の温度に応じた時間分遅延して、書き込み用DLL14から出力される。また、高速揮発性メモリ3からデータを読み出す場合には、CPU温度検出部6にCPU2の温度を検出させて、この検出結果に基づいて、読み出し用DLL11に対してレジスタ設定を行う。これにより、読み出し用DLL11に入力したデータ取り込み信号DQSは、CPU2の温度に応じた時間分遅延して、読み出し用DLL11から出力される。

(もっと読む)

メソシンクロナス・データ・バス装置及びデータ伝送方法

メモリ・システムにおける指定されたポイント間の全体の時間遅延が一定に維持されるように、メモリ・モジュール間のデータの伝送時間が管理される、メモリ・システムについて説明される。多数のレーンのバスの各レーンを別個に管理することができ、中間モジュールにおいてスキュー除去する必要なしに、宛先モジュールにおいてデータフレームを評価することができる。バス・シリアル・データ速度の1つ又それ以上の約数でモジュールを通してデータ経路を作動させ、受信されたデータのサンプリング・ポイントを選択し、温度変化又は時間経過に起因する時間遅延の変動を調整することによって、データを経路指定するためのスイッチを有するモジュールを通したデータの伝播における時間遅延が低減される。 (もっと読む)

自動遅延制御回路およびその回路を用いたメモリインタフェース制御回路

【課題】 回路面積および消費電力を削減することならびに遅延回路の遅延量を最適とすることが可能な自動遅延制御回路の提供。

【解決手段】 自動遅延制御回路8はカウンタ6のカウンタ値に応じて遅延量が段階的に増加する可変遅延回路3、4を備える。可変遅延回路3にはデータストローブ信号DQS0が入力され、この信号が入力されるたびにカウンタ6がカウントアップを行う。信号DQS0と可変遅延回路3から出力される信号DDQSとの位相差が180°となるとF/F5によりカウントアップは停止される。可変遅延回路4にもデータストローブ信号DQS0が入力されるが、この回路にはカウンタ6のカウンタ値の1/2が入力される。よって、データストローブ信号DQS0と信号DDQSとの位相差が180°となったとき、データストローブ信号DQS0と信号DQS1との位相差は90°となる。

(もっと読む)

調停回路

【課題】読み出し要求と書き込み要求のタイミングに拘らず安定した動作が可能な調停回路を提供する。

【解決手段】読み出し要求信号RRQまたは書き込み要求信号WRQにより、所定のパルス幅のラッチ信号LATを発生してラッチ15,25に与え、このラッチ信号LATの時間内に発生した書き込み要求と読み出し要求をFF11,21で取り込み、取り込んだ要求を、同一のタイミングでラッチ15,25から信号S15、S25として出力させる。これにより、ラッチ制御部40からラッチ信号LATが出力されている間に、近接した間隔で書き込み要求と読み出し要求があった場合でも、信号S15,S25のタイミングが一致するので、遅延部30によって予め定められた優先順位に従って書き込み制御信号WTまたは読み出し制御信号TRを安定して出力することができる。

(もっと読む)

メモリカード及びホスト機器

【課題】高いクロック周波数による動作においても安定したデータ転送が可能なメモリカード及びホスト機器を提供する。

【解決手段】ホスト機器20からアクセスされるメモリカード1において、クロック入力回路69は、ホスト機器20からクロックラインを介して第1クロック信号を受け取る。データ入出力回路65は、ライトタイミング調整モードにてホスト機器20からデータラインを介して第2クロック信号を受け取り、リードタイミング調整モードにて第3クロック信号を出力する。ディレイ素子66は、ライトタイミング調整モードにて、データを第1クロックで受け取れるように、第1クロック信号に対する第2クロック信号の位相を調整する。調整値保持回路62は、第2クロック信号の位相の調整値を保持する。ディレイ素子66は、データ転送モードにて、保持された調整値に応じてデータ入出力回路65から出力されたデータのディレイ値を調整する。

(もっと読む)

データインタフェースキャリブレーション

【課題】ユニット間のインタフェースが伝送速度及び/又はバス幅を増すにつれて、雑音及び信号に対する完全性問題の重要性が高まり、データ信号と1個以上のデータストローブ信号との間のタイミング差を補償する方法を提供する。

【解決手段】設定可能なタイミング量だけ1個以上のデータ信号のタイミングを変更するステップと、前記1個以上のデータ信号を使用してキャリブレーションテストデータを受信装置へ書き込むステップと、前記受信装置からテスト値を読み出すステップと、前記受信装置から返送された前記テスト値に少なくとも部分的に応じてクロック信号に関して前記1個以上のデータ信号の前記タイミングを調整するステップと、を備える。

(もっと読む)

半導体装置

【課題】受信したクロックと入力信号の間に位相ずれがあっても、位相ずれをなくした状態で入力信号を取り込める半導体装置の実現。

【解決手段】受信したクロックに基づいて内部クロックを発生するクロック発生回路451と、入力信号を受ける入力バッファ回路452と、内部クロックに同期して入力信号を取り込んで出力する入力回路458とを備える半導体装置において、入力回路は、入力バッファ回路の出力を遅延させ、遅延量が選択可能なディレイ回路460と、内部クロックに同期して入力バッファ回路の出力を取り込む入力回路462と、入力回路の出力信号値を判定することにより、入力バッファ回路の出力の内部クロックに対する位相を判定する位相判定回路465と、位相判定回路の判定結果に基づいて、入力バッファ回路の出力が内部クロックに対して所定の位相になるようにディレイ回路の遅延量を制御するディレイ制御回路461とを備える。

(もっと読む)

信号処理回路

【課題】データ量に合わせて設定される時間情報が変更されてもデータ損出や不要なデータがアプリケーション側へ出力されることを防止できる信号処理回路を提供する。

【解決手段】送信後処理回路107でデータ読出制御信号S1063をアクティブで受けた場合には、データ量が増えて短い遅延時間に変更されたものと判断して、格納情報信号S106が示す書き込みポインターに読み出しポインターを一致させてデータ量が増えた新しい送信パケットをFIFO110から読み出し、データ量が増える前に設定された遅延時間に基づくタイムスタンプを付加されたデータをリセットして、読み出したパケットに1394ヘッダ、CIPヘッダ1,2を付加してリンクコア111の送信回路に出力する。

(もっと読む)

1 - 20 / 29

[ Back to top ]