Fターム[5B077MM01]の内容

Fターム[5B077MM01]に分類される特許

1 - 20 / 109

シリアル転送装置及びシリアル転送方法

推測的技術を用いるメッセージベースのネットワークインターフェースのためのプロセッサ

【課題】メッセージネットワークインターフェースユニットを提供すること。

【解決手段】メッセージネットワークインターフェースユニットは、プロセッサに連結されており、プロセッサがプロセッサによって生成された複数のメッセージをハードウェアユニットに送信することを可能にし、メッセージネットワークインターフェースユニットは、プロセッサによって生成された複数のメッセージのうちの少なくもと1つのメッセージの引数を格納するように動作可能な伝送レジスタであって、少なくとも1つのメッセージが推測的に生成される、伝送レジスタと、伝送レジスタに連結されており、複数のメッセージをキューに入れるように動作可能なキューであって、動作は、メッセージネットワークインターフェースユニットがトリガーメッセージを受信することに応じてキューにおいて実行される、キューとを含む。

(もっと読む)

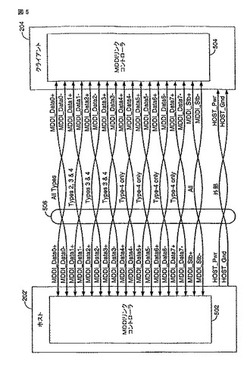

改善されたリンク制御を有する高速データレートインタフェース

【課題】高速データレートインタフェース。

【解決手段】デジタル制御データとデジタルプレゼンテーションデータの事前に選択されたセットを通信するための通信プロトコルを形成するために、共にリンクされるパケット構造を使用して、通信経路上、ホストとクライアントの間でデジタルデータを転送するためのデータインタフェース。前記信号プロトコルは、通信プロトコルを形成するパケットを生成、送信、及び受信し、デジタルデータを1つ又は複数のタイプのデータパケットに形成するように構成され、少なくとも1台が該ホストデバイスに常駐し、該通信経路を通して該クライアントに結合される、リンクコントローラによって使用される。インタフェースは、短距離「シリアル」タイプデータリンクでの、費用効果が高い、低電力の、双方向高速データ転送機構となる。

(もっと読む)

情報処理装置、データバス設定方法、およびプログラム

【課題】装置を小型化でき、かつ、複数のメモリデバイスのいずれにもアクセス可能な情報処理装置を提供する。

【解決手段】複数の記憶手段と、複数の記憶手段に対して情報の入出力を制御する制御手段と、情報を制御手段と送受信するために複数の記憶手段毎に制御手段と接続された第1の信号線と、情報を制御手段と送受信するために複数の記憶手段で共用され、制御手段の接続先を変更可能な第2の信号線と、制御手段からの指示に基づいて、複数の記憶手段のうち、いずれか1つの記憶手段に第2の信号線を接続させる切り替え手段と、を有する。

(もっと読む)

伝送装置、伝送方法、画像形成装置、送信装置及び受信装置

【課題】併走クロックを使用する信号伝送において、併走クロックの周波数を落とすことなく、信号の長距離伝送を行うことを可能とする。

【解決手段】送信側の通信装置1と受信側の通信装置4との間で、クロック信号と併走してデータ信号の伝送を行う伝送装置である。送信側の通信装置1は、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内少なくとも連続する2ビットを同一データとして持つ複数のデータ群として前記受信側の通信装置4送信する。受信側の通信装置は、受信したデータの少なくとも連続する2ビットの同一データを持つデータ群の内、2ビット目以降の何れか1ビットのデータを有効なデータとして受信する。

(もっと読む)

データ転送システム、データ転送装置及びデータ転送方法

【課題】設計自由度を向上させることのできるデータ転送システム、データ転送装置及びデータ転送方法を提供する。

【解決手段】第1転送装置10から第2転送装置20への転送データTDの送信の際に信号レベルが切替えられる送信状態信号Tsと、第2転送装置20での転送データTDの受信の際に信号レベルが切替えられる受信状態信号Rsとの一致・不一致を、第1転送装置10の論理回路15及び第2転送装置20の論理回路24の双方で比較する。これら論理回路15,24における比較結果に応じて、第1転送装置10での新規のデータ信号D1の取り込みと、第2転送装置20での転送データTDの受信とを交互に許可する。

(もっと読む)

同期制御システム

【課題】マスタとスレーブを有し時計により同期する同期システムを得る。

【解決手段】生成部と送受信時間の計測部を有するマスタ11、第1折返し部を含みリセットを受信すると第1時刻に動作する第1スレーブ12、第2折返し部を含みリセットを受信すると第2時刻に動作する第2スレーブ13、第1信号を第1スレーブへ送信する第1ケーブル、それと等長で第1信号をマスタへ送信する第2ケーブル、第2信号を第2スレーブへ送信する第3ケーブル、それと等長で第2信号をマスタへ送信する第4ケーブルを備え、計測部は第1信号が第1信号折返し部を経て受信される時間の半分の第1時間と第2信号が第2信号折返し部を経て受信される時間の半分の第2時間を算出し、生成部は到達時間の中で第2時間が最長の場合は第2時刻を0に第2時間と第1時間の差を第1時刻に設定し、第1時間が最長の場合は第1時刻を0に第1時間と第2時間の差を第2時刻に設定する。

(もっと読む)

マイクロコンピュータ

【課題】通信ネットワークに接続されるものにつき、簡単で且つ低コストで実現できる構成で、ホストによる処理効率の低下を防止できるマイクロコンピュータを提供する。

【解決手段】CPU2と通信モジュール3との間に、CPU2が直接アクセスを行う読み出しバッファ9,及び書き込みバッファ8と、通信要求を周期的に出力することで通信モジュールが他のノードより受信したデータを読み出しバッファに転送する読み出し制御部11と、書き込みバッファ8に書き込まれているデータを送信データとして通信モジュール3に転送する書き込み制御部8aとを備える。また、CPU2が通信モジュール3との間で直接データの読み書きを行うように制御するバイパスアクセス制御部7と、読み出し,書き込み,バイパスアクセスの各制御部6,7,8aによる通信モジュール3へのアクセス順序を制御するアクセス順序制御部10とを備える。

(もっと読む)

データ転送回路

【課題】異なるクロックのデータ転送を行うときに、パルスストレッチ回路を用いることなく、不正な値が転送されないようにすることを目的とする。

【解決手段】クロックCLK−Aで動作する入力側回路部2とクロックCLK−Bで動作する出力側回路部3とを有し、データData−Aを出力データData−Bとして出力させる回路であって、入力側回路部2に設けられ、入力データData−Aを入力して中間データMidとして出力する入力側フリップフロップ4と、出力側回路3に設けられ、中間データMidを入力して出力データData−Bとして出力させる出力側フリップフロップ5と、出力側フリップフロップ5が中間データMidを入力するときには、中間データMidを固定値として出力するように入力側フリップフロップ4を制御する制御部6と、を備えたことを特徴とする。

(もっと読む)

通信システム及びそのデバイス

【課題】1本の信号線を用いて双方向のシリアル通信を行う通信システム及びそのデバイスを提供することを目的とする。

【解決手段】第1デバイス11と第2デバイス12間を1本の信号線で接続し、互いにレベルの異なる第1レベルと第2レベル、及び前記第1レベルと第2レベルの中間レベルを用いてシリアル通信を行う通信システムであって、第1デバイスは、第1レベルと中間レベルを繰り返すことで第2デバイスにクロックを送信し、第2デバイスは、受信したクロックの中間レベルの期間に第2レベルを出力するか否かで第1デバイスに情報を送信し、第1デバイスは、第2デバイスが情報を送信していない場合に、クロックの中間レベルの期間に第2レベルを出力するか否かで前記第2デバイス12に情報を送信する。

(もっと読む)

送受信装置及び信号伝送装置

【課題】一対の信号線からなる差動信号線に接続された送受信部が差動信号線を介して送信側又は受信側の何れに接続された場合にも通信を行うことが可能な送受信装置、及びそれを備えた信号伝送装置を提供する。

【解決手段】送受信装置1は、第1の信号線21及び第2の信号線22からなる差動信号線20を介して送信側又は受信側に接続され、送信側に接続されたときは第1の信号線21によって信号を受信し、受信側に接続されたときは第2の信号線22によって信号を送信する送受信部10と、送受信部10によって送信又は受信される信号を処理する信号処理部14とを備える。

(もっと読む)

電子機器、電子機器の制御方法、送信装置および受信装置

【課題】HDMI等のデジタルインタフェースにおいて大容量のデータ通信を可能にする。

【解決手段】DDCラインを構成する2本の信号ライン、つまりSDAラインおよびSCLラインを、I2C通信ラインとして用いる他に、高速データ通信ラインとしても用いる。この2本の信号ラインをI2C通信ラインとして用いる場合、ソース機器110、シンク機器120は、I2C通信部を2本の信号ラインに接続した状態となり、I2Cの双方向通信を行う。一方、この2本の信号ラインを高速データ通信ラインとして用いる場合、ソース機器110、シンク機器120は、差動高速ドライバ/レシーバを2本の信号ラインに接続した状態となり、双方向差動通信を行う。双方向差動通信を行う場合、時分割双方向通信を行うことで、全体としての伝送速度は片方向の2倍強必要とされるが、エコーキャンセラを用いた双方向構造よりも安価に実現できる可能性がある。

(もっと読む)

ユニバーサルシリアルバス(USB)システムのオンライン較正方法及びその装置

【課題】USBホストとデバイスの終端抵抗特性を同時に参考することができ、USB装置同士の適応性を向上させる。

【解決手段】USBシステムに適用するオンライン較正方法は、複数の対のチャープ信号を提供するステップと、前記チャープ信号を検出し、所定数量の前記チャープ信号を発信する前に、前記デバイスの終端抵抗とそれに接続されるホストの終端抵抗に電源を加えて、前記チャープ信号の準位を変更するステップと、前記変更後のチャープ信号のノード上での準位変化を検出するステップと、前記準位変化に基づきオンライン較正を行い前記変更後のチャープ信号の準位を所定範囲内に維持するステップと、を有する。

(もっと読む)

USB通信装置、及びUSB通信装置の消費電力削減方法

【課題】USB通信においてパケット送信中も消費電力の低減を図ることが可能なUSB通信装置を提供する。

【解決手段】USB通信装置は、ドライバ回路(51)は、上位装置(2)からの送信要求信号(8)に基づくパケット送信期間にパケットをUSBバス(3)へ送信する。レシーバ回路(52)は、前記USBバス(3)に前記パケットが送信されたことを検出すると検出するとパケット送信中を示すスケルチ信号(11)を出力する。ラインステート信号制御回路(6)は、スケルチ信号を入力すると予め定められたラインステート信号(12)により上位装置へ通知する。レシーバ回路は、パケット送信期間において、ラインステート信号の出力を固定させるようにラインステート信号制御回路を制御すると共にレシーバ回路を停止させるように制御する。

(もっと読む)

通信方法及びデバイス装置

【課題】クラス選択におけるユーザの利便性を向上させつつも、ユーザの意図に沿ったデバイスクラスを選択することのできる通信方法を提供する。

【解決手段】DSC(デバイス装置)が、自身が対応している全てのデバイスクラスについてPC(ホスト装置)と接続可能か否かを判断する(ステップS8〜ステップS13)。次に、ホスト装置と接続可能と判断されたデバイスクラスを表示部に表示する(ステップS15)。その後、表示部に表示されたデバイスクラスの中から1つのデバイスクラスが選択されると、そのデバイスクラスの通信プロトコルでデータ通信を開始する(ステップS20)。

(もっと読む)

バッファ制御装置およびバッファ制御方法

【課題】QoS制御回路自身も含めたバッファ制御の低消費電力化を実現する。

【解決手段】パケット多重手段(2)と、多重データに対して大容量バッファ制御を行うQoSバッファ制御手段(5)と、多重データに対して小容量バッファ制御を行うFIFO手段(6)と、大容量バッファ制御中のトラヒック状態および小容量バッファ制御中のトラヒック状態をそれぞれモニタし、大容量バッファ制御または小容量バッファ制御のいずれかを選択切り替えする入力選択信号および出力選択信号を生成するとともに、小容量バッファ制御中においてQoSバッファ制御手段をパワーダウンさせておく省電力選択制御手段(4)と、選択信号に基づいて小容量バッファ制御と大容量バッファ制御の入出力を切り替える入力選択手段(3)および出力選択手段(7)とを備える。

(もっと読む)

データ同期化回路、通信インタフェース回路及び通信装置

【課題】データを同期化させるクロック信号の許容される周波数の範囲を広げる。

【解決手段】実施形態によれば、データ同期化回路SYNC0は、データホールド回路BLC0と、受信タイミング生成回路BLB0と、更新タイミング調整回路BLE0とを備えている。データホールド回路BLC0は、クロック信号CLK_A0に同期したデータDOUT0を受信して、当該データDOUT0がクロック信号CLK_Bに同期化されたデータSYNC_DATA0を出力する。更新タイミング調整回路BLE0は、受信タイミング生成回路BLB0内のDフリップフロップ230_0,230_1及び230_2の値の更新のタイミングを、クロック信号CLK_Bに同期した更新イネーブル信号UE0に基づいて制限する。

(もっと読む)

データプロセッサ

【課題】プロセッサコアのローカルメモリや共有メモリの所要のアドレスに対して小さな回路規模で排他制御を行うことができるデータプロセッサを提供する。

【解決手段】要求に従ってバスロック設定と解除が可能にされるシステムバス(5)を共有する複数個のプロセッサコア(20,40)が相互に互いの内部リソース(22,42)を共有するデータプロセッサ(1)において、プロセッサコアが内部リソースの第1アドレス(ロック変数割り当てアドレス)へアクセスを行うときバスロックの要求を伴って当該アクセス要求をシステムバスに出力することによりシステムバスにバスをロックさせると共にシステムバスから当該プロセッサコアに帰還されるのを待って当該アクセス要求を処理し、プロセッサコアが内部の第2アドレスへアクセスを行うとき当該アクセス要求をプロセッサコアの内部で処理する。

(もっと読む)

携帯端末

【課題】折り畳み式の携帯端末等で、シリアルインターフェースにて接続される制御デバイスと、被制御デバイス(複数)とが別々の筐体に配置される場合、筐体間の信号本数が多くなると断線の可能性が増大するだけでなく、フレキケーブルなどが広くなりコストアップや外観デザインへの悪影響の要因となる。

【解決手段】複数の被制御デバイスが同期式シリアルインターフェースの場合において、1系統の同期式シリアルインターフェースのシリアルデータ信号の先頭に接続するデバイスを選択するためのデータを付加し、そのデバイス選択データをデコードして接続するデバイスのCS(チップセレクト)信号を付加ビットと選択デバイスへの送信データの間で生成し、送信データの送信完了(入力CSの完了)でCS信号を停止する回路を制御される基板側に搭載することによって、1系統の高速同期式シリアルで複数のデバイスが制御可能となり、筐体間の信号本数低減を可能とする。

(もっと読む)

共通クロック方式の同期型シリアル転送回路

【課題】シリアルクロックの動作周波数が上限に達していても、新たなシリアルデータ信号線路を追加することなく、転送速度のさらなる高速化が可能な、共通クロック方式のシリアル転送回路を提供する。

【解決手段】シリアルデータ信号を伝送する線路として、従来のシリアルデータ信号線路に加えて、シリアルクロック信号を伝送する線路をも利用する。このとき、シリアルクロック信号を伝送する線路のインピーダンスを制御することによって、シリアルデータ信号の一部を表現する。

(もっと読む)

1 - 20 / 109

[ Back to top ]