Fターム[5B081AA06]の内容

特別なプログラム実行装置 (1,497) | プログラミング言語 (310) | C (78)

Fターム[5B081AA06]に分類される特許

1 - 20 / 78

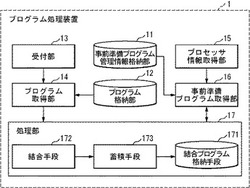

プログラム処理装置、プログラム処理方法、およびプログラム

【課題】従来のライブラリは、プロセッサごとに最適化され、それぞれの環境に依存するものである。

【解決手段】プロセッサ条件と、事前準備プログラム識別子とを有する事前準備プログラム管理情報を格納し得る事前準備プログラム管理情報格納部と、事前準備プログラムと、プログラムとを格納し得るプログラム格納部と、プログラム識別子を有する指示を受け付ける受付部と、当該プログラムをプログラム格納部から取得するプログラム取得部と、プロセッサ情報を取得するプロセッサ情報取得部と、プロセッサ情報が合致するプロセッサ条件に対応する事前準備プログラムを取得する事前準備プログラム取得部と、事前準備プログラム取得部が取得した事前準備プログラムを用いて、プログラム取得部が取得したプログラムを処理する処理部を具備するプログラム処理装置により、プロセッサに適合する事前準備プログラムを用いて、プログラムを処理することができる。

(もっと読む)

コンパイル装置、コンパイル方法、及びプログラム

【課題】コンパイルにより生成するオブジェクトコードのデータサイズを小さくすること

【解決手段】サブルーチン検出部131は、ソースプログラムの解析から得られる中間コードに含まれる命令列に対し、所定規則により類似と判定される類似命令列をも同一命令列とみなす比較を行い、サブルーチン化可能な命令列群であるサブルーチン対象命令列群を検出する。サブルーチン生成部132は、サブルーチン対象命令列群から前記オブジェクトコード内に埋め込むサブルーチンを生成する。この際、サブルーチン生成部132は、類似命令列に関する処理を置換可能に構成したサブルーチンを生成する。サブルーチン呼び出し部133は、オブジェクトコードに対し、類似命令列の各々に応じた処理を埋め込む。

(もっと読む)

データ処理装置、データ処理方法、及びプログラム

【課題】インライン展開の確認が容易なデータ処理装置、データ処理方法、及びプログラムを提供すること

【解決手段】コンパイラ10は、ソースプログラムをコンパイルしてアセンブリプログラムを生成すると共に、アセンブリプログラムの生成の際にインライン展開を行った関数呼び出し命令の位置情報を記載したデバッグ情報を生成する。ソースプログラム表示編集部20は、デバッグ情報に基づいて、インライン展開を行った関数呼び出し命令を特定した表示画面を生成する。

(もっと読む)

情報処理装置およびプログラム

【課題】高性能な並列プログラムを低コストで生成可能とする。

【解決手段】タスク境界を示す情報と、1のデータに対するデータアクセスに対応するN個のノードとノード間の依存関係を示すエッジとを含み、少なくとも1のノードは対応するデータアクセスが確実/不確実を示すアクセス確実性フラグを持つ第1依存関係情報とに基づき、タスク境界を跨ぐエッジのうち、不確実アクセスノードを少なくとも一方に接続しているタスク境界エッジを特定し、当該不確実アクセスノードを示す提示情報を生成する。1のデータに対応して入力された依存有無情報に従い、不確実アクセスノードに対するデータアクセスが無いことを示す情報を含む変換情報を出力する。変換情報に従い、第1依存関係情報を、1のデータに対するデータアクセスに対応するM(0≦M≦N)個のノードと、ノード間の依存関係を示すエッジとを含む第2依存関係情報に変換する。

(もっと読む)

コンパイラ装置、コンパイル方法及びコンパイラプログラム

【課題】条件分岐命令の条件判定処理と、分岐後の各命令がグローバル変数に依存している場合に、条件分岐命令の条件判定処理と、分岐後の各命令が並列処理されても誤動作しないオブジェクトプログラムを生成するコンパイラ装置を提供する。

【解決手段】本発明のコンパイラ装置は、グローバル変数の値に基づいてグローバル変数の値を変更する処理を含む関数を、コア割り当て対象関数として抽出するコア割り当て対象関数抽出部と、コア割り当て対象関数が、条件分岐命令の条件判定処理による分岐後の呼出し関数となる場合には、マルチコアプロセッサの各CPUコアにコア割り当て対象関数を割り当て、条件分岐命令の条件判定処理によって、グローバル変数が変更された場合には、グローバル変数の値に基づいてグローバル変数の値を変更する処理を、コア割り当て対象関数にリトライさせるようにソースプログラムを修正するソース修正部とを備える。

(もっと読む)

プログラム並列化装置およびプログラム

【課題】メモリを圧迫せず、制御容易な並列化プログラムを出力する。

【解決手段】並列化部は、入力された、変換対象プログラムとループ内の処理の分割を示す分割情報からループを第1および第2の処理に分割する。第1及び第2の処理は、それぞれループの終了制御処理を含むことを示す終了制御情報と、ループの後続処理で参照されるデータの変更を示す変更情報とを持つ。並列化部は、変換対象プログラム上で、第2の処理が第1の処理に後続する場合に第2のスレッドが第2の処理の反復回数(n−1)回目の実行で終了するか否かを判定し、第2の処理が第1の処理に先行する場合に第2の処理が第2の処理の反復回数n回目の実行で終了するか否かを判定するための判定処理を第1の処理に挿入し、判定処理により通知された判定の結果により第2の処理の実行を制御するための制御処理を第2の処理に挿入する。

(もっと読む)

コンパイル装置及び方法

【課題】関数呼び出し時の引数としてプロセッサエレメント用変数名を指定することができ、関数内の自動変数としてプロセッサエレメント用変数名を指定することができ、かつ変数値を記憶するスタックの領域を減少させることができるコンパイル装置及び方法を提供する。

【解決手段】コンパイル装置は、関数呼び出し時に、引数がグローバルプロセッサの変数名であればグローバルプロセッサのスタック領域に引数値を退避し、引数がプロセッサエレメントの変数名であればプロセッサエレメントのスタック領域に引数値を退避し、かつ各スタック領域から引数値を取り出すようにコード展開し、自動変数の領域を確保する時に、自動変数がグローバルプロセッサの変数名であればグローバルプロセッサのスタック領域に自動変数の領域を確保し、自動変数がプロセッサエレメントの変数名であればプロセッサエレメントのスタック領域に自動変数の領域を確保するようにコード展開する。

(もっと読む)

プログラム変換処理装置、方法及びプログラム、並びに記録媒体

【課題】ラダープログラムをC言語プログラムに変換可能で、C言語プログラムの知識が無くともCPU基板上で動作するプログラムを簡単に作製可能とし、また既存のプログラム資産の有効活用を可能とする。

【解決手段】ラダーコマンドに対応するC言語コマンドを記録したプログラム変換テーブル50を格納した記憶手段20と、入力されたラダープログラムのコマンドを前記プログラム変換テーブル50を用いてC言語コマンドに変換して、前記ラダープログラムからC言語プログラムを作成する情報処理手段10とを備えている。変換結果は、記憶手段20内の変換データ記憶領域70に順次格納される。

(もっと読む)

プログラム変換装置、およびそのプログラム

【課題】マルチコアプロセッサのメモリ使用効率を向上できる。

【解決手段】本発明の一実施形態に係るプログラム変換装置は、複数の変数を有する第1プログラムコードを、複数のコアを有するプロセッサによって実行される第2プログラムコードへ変換する。第2のプログラムコードは、所定のアクセスパターンでアクセスされると判定された変数を含むメンバ構造体と、そのメンバ構造体を指定するルートポインタとを有する。

(もっと読む)

コンパイル装置、コンパイル方法、コンパイラ

【課題】オブジェクトコード実行時に、自動変数に対するデータアクセス時間を短縮できるコンパイル装置を提供すること

【解決手段】コンパイル装置1は、コンパイル部40内に自動変数解析部411と、自動変数スタック処理部421と、を備える。自動変数解析部411は、ソースプログラムに含まれる自動変数を解析した解析情報を抽出する。自動変数スタック処理部421は、自動変数解析部411による解析に応じて、自動変数を格納するスタック領域を複数の記憶装置から選択する。

(もっと読む)

データ処理装置、データ処理方法およびプログラム

【課題】連想配列を扱えないプログラミング言語でのプログラミングで、連想配列に相当するデータ構造をメモリに容易に実装可能なデータ処理装置を提供する。

【解決手段】 データ処理装置は、連想配列の宣言を受け付けると第1領域にポインタ配列を生成し、ポインタ配列の存在時に登録指示を受け付けると、第1文字列のハッシュ値を求め、第1文字列を第2領域に格納し登録データを第3領域に格納し、第1文字列のハッシュ値で指定されるポインタ配列の第1要素に第2および3領域を特定するための特定情報を格納し、第1要素に特定情報が格納されている状況で参照指示を受け付けると、第2文字列のハッシュ値を求め、第2文字列のハッシュ値が第1文字列のハッシュ値と同一である場合、第1要素内の特定情報を用いて第1文字列を読み出し、第1文字列が第2文字列と同一である場合、特定情報を用いて登録データを読み出し実行部に送信する

(もっと読む)

デバッグシステムおよびプログラム開発システム

【課題】ソースレベルでの変換・最適化を実施した際にもデバッグのし易さを確保し、ソフトウェア開発の利便性および開発効率を高めることができるコンパイルシステムを提供する。

【解決手段】高級言語で記述されたソースプログラムを機械語プログラムに翻訳するコンパイルシステムであって、オリジナルソースプログラム101に対してソースプログラムレベルの最適化を施すことにより、オリジナルソースプログラム101を最適化ソースプログラム102に変換するソースレベルオプティマイザ3と、最適化ソースプログラム102を機械語プログラム104に変換するコンパイラ5と、オリジナルソースプログラム101と機械語プログラム104との対応関係を示す最終デバッグ情報112を生成する最終デバッグ情報選択生成部52とを備える。

(もっと読む)

ソースプログラム他言語変換支援装置、変換支援方法および変換支援プログラム

【課題】単純な予約語の変換では対応できない場合にも変換作業を効率的に行えるよう支援することを可能とするソースプログラム他言語変換支援装置等を提供する。

【解決手段】本実施形態に係るプログラム変換支援装置10は、ユーザに入力された入力文章を一時的に保存する一時記憶手段14と、変換対応情報23および文脈パターン情報24が予め記憶されている固定記憶手段12と、変換前ソースプログラムが1行ずつ入力されるたびにこの入力文章を一時記憶手段に記憶させる一時記憶制御部21Aと、入力文章と一致する入力内容が変換対応情報に含まれているか否かを判断する入力内容比較部21Bと、一時記憶手段に記憶されている内容を文脈パターン情報と比較して一致する行数を点数として算出する文脈比較部21Cと、点数が最も高い変換内容を入力文章に対して出力する変換出力部21Dとを有する。

(もっと読む)

オブジェクトプログラム作成装置、及びオブジェクトプログラム作成方法

【課題】複数の命令実行手段と複数のメモリを有する情報処理装置により実行されるオブジェクトプログラムを、より効率的な配列で作成すること。

【解決手段】複数の命令実行手段から前記複数のメモリへのアクセスに関するレイテンシ情報を記憶したレイテンシ情報記憶手段と、オブジェクトプログラム生成手段により生成されたオブジェクトプログラムに含まれる複数のメモリアクセス命令のそれぞれについて、レイテンシ情報を参照してレイテンシを付与するレイテンシ付与手段と、付与されたレイテンシに基づいてオブジェクトプログラムに含まれる複数の命令を並べ替える並べ替え手段と、を備え、レイテンシ情報記憶手段に記憶されているレイテンシ情報は、メモリアクセスのアクセス元とアクセス先の組み合わせに応じてそれぞれ個別のレイテンシを規定していることを特徴とする、オブジェクトプログラム作成装置。

(もっと読む)

エンディアン変換のための方法および装置

【課題】バイトオーダ依存コードを逆のバイトオーダ依存アーキテクチャまたはシステム上で実行することのできるコンパイラを提供する。

【解決手段】コンパイラは、コード(例えばソースコード)を分析して、逆のバイトオーダ依存アーキテクチャまたはシステムと互換性を有する「エンディアン中立」ソースコードバージョン等を生成するために、ソースコードの変更が望ましい箇所を示す診断レポートを生成する(110)。例えば、プログラマは、ソースコードの特定のコード領域に望ましいバイトオーダを指定することができ、これによりコンパイラは、プログラマがこれら望ましいエンディアン構成を実行するのに必要な変更を行う助けをする。

(もっと読む)

マクロ展開方法およびプリプロセッサ

【課題】プリプロセッサにおいて多段のマクロ呼び出しの展開を含むマクロ展開処理を柔軟かつ簡素に実装することができるマクロ展開方法を提供する。

【解決手段】ソースコードの文字列から第1のトークンを切り出してトークン配列を生成するステップS102と、トークン配列から順に第1のトークンをバッファに読み込むステップS104と、バッファ内の第1のトークンについて、マクロ呼び出しに該当する部分ではない場合に処理結果として出力するステップS109と、マクロ呼び出しに該当する部分であり、かつマクロ呼び出しとして完結している場合に、マクロ呼び出しに該当する部分を対応するマクロ定義の内容によって置換して展開するステップS111と、マクロ呼び出しを展開した文字列から第2のトークンを切り出すステップS112と、第2のトークンを入力のトークン配列の先頭に戻すステップS113とを実行する。

(もっと読む)

アプリケーション生成システム、方法及びプログラム

【課題】互いにネットワークで接続されていてもよい、複数のコンピュータ・システムからなるハイブリッド・システム上で、リソースの利用及び実行速度の点で可能な限り最適化された実行可能コードを生成可能なコード生成技術を提供する。

【解決手段】ソースコードのライブラリ部品について最適化表を作成する処理と、結果の最適化表を用いて、自動的な計算リソース割り当てと、互いにネットワークで接続されているハイブリッド・システムのための、ネットワーク・エンベディングを行うことによって、最適化された実行可能コードを生成する。

(もっと読む)

コンパイラ装置

【課題】プログラムの開発工数がかからないコンパイラを提供する。

【解決手段】高級言語で記述されたソースプログラム72を機械語プログラムに翻訳するコンパイラ58であって、生成する機械語プログラムを最適化する旨の指示を取得する指示取得部と、前記ソースプログラム72を解析するパーサー部76と、前記パーサー部76における解析結果に基づいて、前記ソースプログラム72を中間コードに変換する中間コード変換部78と、前記指示に従って、前記中間コードを最適化する最適化部68と、前記中間コードを前記機械語プログラムに変換するコード生成部90とを備え、前記指示は、キャッシュメモリを利用するプロセッサをターゲットプロセッサとする最適化指示である。

(もっと読む)

プログラム生成方法およびシステムの動作方法

【課題】 プログラムを高速に実行し、システムの性能を向上する。

【解決手段】 情報処理装置は、階層構造を有する複数の関数を含むソースプログラムにおいて、実行頻度の高い関数を、内部メモリに格納する選択関数として順次に選択する。情報処理装置は、選択関数を内部メモリの記憶領域に割り当て、選択関数から呼び出される選択関数以外の関数を内部メモリの記憶領域に近接する領域に割り当てて内部ロードモジュールを生成する。情報処理装置は、残りの関数をプロセッサに接続される外部メモリに割り当てて外部ロードモジュールを生成する。そして、プログラムが格納される内部メモリを有するプロセッサにより実行されるプログラムが生成される。階層構造を有する複数の関数のうち実行頻度の高い関数を内部メモリに割り当てることで、プログラムを高速に実行でき、システムの性能を向上できる。

(もっと読む)

オブジェクトコード生成システム、及びオブジェクトコード生成方法

【課題】フラッシュメモリのブロック情報の準備を不要とする。

【解決手段】cソースをコンパイル・リンクする時に関数名、配置アドレス、最大サイズ、ダミー関数有無フラグの情報を格納した関数情報を作成し、ある関数を修正後に再度コンパイル・リンクする時に、その情報を基に関数単位でコードサイズが修正前より大きくなった場合、修正前のサイズを超えたサイズ分をダミー関数として出力することで、cソースの変更に着目せず、コードサイズでの差分に着目し、分岐命令出力を最小限に抑える。このようにして、cソースのコンパイル、リンク時に関数情報を自動で作成及び更新する。

(もっと読む)

1 - 20 / 78

[ Back to top ]