Fターム[5B083EE06]の内容

計算機における入出力系RAS (2,172) | 障害発生源(ハード関連) (258) | 入出力制御装置(IOC) (20)

Fターム[5B083EE06]に分類される特許

1 - 20 / 20

データ転送制御装置

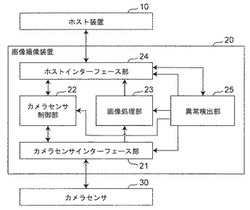

【課題】連続的で高速なデータ転送に起因する、データ転送停止や回路の異常発熱を回避することが可能なデータ転送制御装置を実現する。

【解決手段】データ転送制御装置(20)は、ホスト装置とのデータのやりとりを行うことが可能なホストインターフェース部(24)と、周辺装置とのデータのやりとりを行うことが可能な周辺装置インターフェース部(21)と、ホストインターフェース部または周辺装置インターフェース部の異常状態を検出する異常検出部(25)と、異常検出部が異常を検出した場合に、ホストインターフェース部または周辺装置インターフェース部でのデータ転送を中断し、その後、異常検出部がホストインターフェース部または周辺装置インターフェース部の正常状態への回復を検出した場合に、ホストインターフェース部または周辺装置インターフェース部でのデータ転送動作を再開する転送制御部(25)とを備える。

(もっと読む)

バス接続回路及びバス接続方法

【課題】I2Cバス接続された周辺部品がBus-Busyとなった場合でも、システム全体が動作し続けることができるようにすること。

【解決手段】本発明のバス接続回路21は、周辺部品側のI2C端子レベルを検出するバッファ24と、周辺部品とシステム全体のI2Cバスとを切り離すSW25と、I2C故障検出制御モジュール26と、周辺部品側がHi-Z状態になっているかを確認するためのPull Up抵抗34と、Pull Down抵抗35と、を備える。I2C故障検出制御モジュール26は、バッファ24で受けた値が、Highレベルか、それともLowレベルであるかを判断するH/Lレベル検出部30と、Lowレベルの持続時間を測るLowレベル検出時間計測部31と、SW25をON/OFF制御するI2Cバス切断制御部32と、Pull抵抗制御部33と、を備える。

(もっと読む)

シリアル通信カード試験装置

【課題】大量の高速シリアルデータの送受信を複数回繰返す動作確認試験を試験員が手作業で行うことは長時間を要する。

【解決手段】一実施形態によれば、シリアル通信路と、基準シリアル通信カードと、被試験シリアル通信カードと、記憶部及びCPUを持つ第1の処理装置と、ネットワークと、記憶部及びCPUを持つ第2の処理装置と、これらの処理装置の各記憶部に各試験プログラムをロードし、操作指令を発行して各シリアル通信カード間の送受信を制御する制御装置とを備え、この制御装置は、各シリアル通信カードにシリアルデータの送受信を複数回繰返させ、送受信終了後、各記憶部からそれぞれ送受信データを収集し、データの相互比較により被試験シリアル通信カードの動作確認試験を行うシリアル通信カード試験装置が提供される。

(もっと読む)

周辺装置の設定情報のエラー検出を有するデータ処理システム

【課題】高い強固であり、且つ高い信頼性を有するデータ処理システムを提供する。

【解決手段】データ処理システムは、周辺装置用バスインタフェースと動作可能に接続された第1マスタと、周辺装置用バスインタフェースに動作可能に接続された複数の周辺装置とを含む。第1マスタは、前記周辺装置用バスインタフェースを介して複数の周辺装置の各々と通信する。該データ処理システムにおける方法は、第1マスタによって設定情報を複数の周辺装置のうちの第1周辺装置に書き込みを開始することを含む。書き込み開始に応答して、第1周辺装置に格納するために周辺装置用バスインタフェースを介して設定情報が供給される。設定情報の第1エラーシンドロームは、周辺装置用バスインタフェースによって生成される。供給された設定情報は第1周辺装置に格納され、第1エラーシンドロームは周辺装置用バスインタフェースの記憶回路に格納される。第1エラーシンドロームは、次のエラー検出中に、設定情報の完全性をチェックするように使用され得る。

(もっと読む)

周辺デバイス部のオンラインテスト機能を備えたCPUボード、及びそのオンラインテスト方法

【課題】周辺デバイス部のオンラインテスト機能を備えたCPUボード、及びそのオンラインテスト方法を提供することを目的とする。

【解決手段】プログラムを実行するCPU1と、その周辺デバイス部3−1〜3−nと、周辺デバイス部に対して自己診断テストを実行するテスト回路部5と、前記CPUとテスト回路部とが、夫々異なる周辺デバイス部に同時アクセスを可能に接続するクロスバースイッチ型のバス制御部4とを備え、テスト回路部5は、CPUのアクセス予測を監視し、CPUが次にアクセスしない周辺デバイス部に対してテストを行う周辺デバイス部を求め、CPUが現在アクセス中の周辺デバイス部と異なる周辺デバイス部であり、且つ、次のバスサイクルでもアクセスしない周辺デバイス部を選択して自己診断テストを実行するようにしたことを特徴とする。

(もっと読む)

障害箇所推定システム、障害箇所推定装置および障害箇所推定方法

【課題】ネットワークの異常の原因となる範囲を絞り込み、システムのトラブル調査を支援すること。

【解決手段】障害箇所推定システム10の関連クラス適用部11は、構成情報21、関連クラス適用ルール22および関連クラス23を参照し、構成情報21に含まれる構成要素間の関係について、関連クラス適用ルール22に基づいて関連クラスを適用する。調査範囲限定部12は、関連クラス23、調査内容24、異常検知情報25を参照して、異常が発生した構成要素の各々について調査範囲に従って辿った構成要素及び関連を調査範囲限定ツリーとして求める。障害発生箇所候補推定部13は、異常が発生した構成要素の各々について求めた調査範囲限定ツリーにおける構成要素の出現頻度に基づいて異常の原因となる障害が発生した箇所の候補を推定する。

(もっと読む)

安全性関連処理のバス結合のための方法と装置

【課題】安全性関連の処理の1チャネルのバス結合のための方法、およびその方法を実行するように構成された装置を提供する。

【解決手段】プロトコル特異性に基づいて、安全性臨界処理に関連するデータ記録が少なくとも2つの冗長処理チャネル1、2を介して、各々のケースで1つの安全プロトコル14、24に関して同じ法則に従って処理され、1チャネルのバス結合のための冗長性の安全メッセージ14、24が一体に連結されることで共通の安全プロトコルを形成し、正確に述べると、各々のケースでそれぞれの安全性メッセージの異なる構成要素に書き込むことによって共通の安全プロトコルが構成要素内で一体に連結されるような方式で処理チャネル1、2の各々が、一回だけ割り当てられる各々のレジスタ場所に関する書き込み権限を伴って共通のバッファ・レジスタ30にアクセスする。

(もっと読む)

コンピュータ及び通信処理方法

【課題】ネットワーク装置が搭載されたコンピュータのネットワーク接続時における可用性の向上を図ることができ、コンピュータの信頼性の向上を図ること。

【解決手段】ネットワークに対して送受信する通信データを処理するネットワーク処理部と、このネットワーク処理部を介した通信動作を制御する通信制御処理部と、を備え、ネットワーク処理部による通信データの処理結果を取り出す処理結果取出手段と、通信制御処理部にてネットワーク処理部による処理と同一の通信データの処理を実行する同一処理実行手段と、ネットワーク処理部による処理結果と通信制御処理部による処理結果とを比較する処理結果比較手段と、この比較結果に基づいてネットワーク処理部の少なくとも一部の処理を代替する通信処理代替手段と、を備えた。

(もっと読む)

テスト装置、高速シリアルコントローラ及び画像処理装置

【課題】接続された半導体間におけるエラー機能評価を行う際に、エラー機能評価を行うための機器類を用意する必要がないテスト装置、高速シリアルコントローラ及び画像処理装置を提供する。

【解決手段】ダウンストリーム通信の際に用いる第1の高速シリアルインターフェースと、アップストリーム通信の際に用いる第2の高速シリアルインターフェースと、第1の高速シリアルインターフェースの論理層を制御するダウンストリーム制御モジュールと、第2の高速シリアルインターフェースの論理層を制御するアップストリーム制御モジュールと、を備えた高速シリアルコントローラに内蔵され、高速シリアルインターフェースのエラー機能を評価する際に必要なエラーパケットを生成する機能と、生成したエラーパケットを、高速シリアルインターフェースへ出力する機能と、を有する。

(もっと読む)

USBデータ転送システム及びそのコンピュータ

【課題】コンピュータが、USBハブを介して周辺機器としての記憶装置との間でデータ転送する場合、USBハブへの周辺機器の接続状態を検出するため、その記憶装置をUSBハブを介して接続するときは、コンピュータのUSBポートに直接に挿入して接続するときよりもデータ転送の効率が悪く、時間を要する。

【解決手段】記憶装置とUSBハブを介して接続し、当該USBハブに当該記憶装置を接続しているか否かを検出をする接続状態検出部を有するコンピュータを備えたデータ転送システムにおいて、当該コンピュータは、当該記憶装置との間のデータ転送開始を検出する転送開始検出手段を有し、データ転送開始を検出した場合、当該接続状態検出部の接続状態検出機能を停止する停止手段を備えるUSBデータ転送システム。

(もっと読む)

データ中継装置、ストレージ装置、および応答遅延監視方法

【課題】リード要求に応じたデータの読み出しの遅延を抑制するとともに、キャッシュメモリを制御するプロセッサの処理負荷を軽減すること。

【解決手段】リード要求送信部52aは、送信したリード要求のタグを要求管理テーブル52bへ通知する。要求管理テーブル52bは、リード要求送信部52aから通知されるタグごとに、リード要求が送信されてからの経過時間を管理する。遅延監視部52dは、要求管理テーブル52bにおいてカウントされるリード要求ごとの経過時間を監視する。そして、遅延監視部52dは、経過時間が警告レベルまたはエラーレベルに達すると、警告メッセージまたはエラーメッセージの送信をメッセージ送信部51cに指示する。メッセージ送信部51cは、キャッシュ接続部52からの指示により、警告メッセージまたはエラーメッセージを送信する。

(もっと読む)

ネットワークブート計算機システムの高信頼化方法

【課題】ネットワーク計算機システムにおいて、ネットワーク上のネットワークスイッチや外部ディスク装置などの機器の障害発生時には、障害回復ができない場合がある。

【解決手段】複数のサーバと、複数のネットワークと、複数の外部ディスク装置と、管理計算機と、を備える計算機システムにおいて、前記管理計算機は、障害が発生したことを検知し、前記障害を原因として、利用していた前記ディスクにアクセスできなくなる業務停止サーバを検索し、前記検索された業務停止サーバが利用していたディスクと同一の内容を格納するディスクと、そのディスクを含む前記外部ディスク装置を検索し、前記検索された外部ディスク装置にアクセスできる業務再開サーバを検索し、前記検索された業務再開サーバに、前記検索されたディスクを利用して起動するための指示を送信する。

(もっと読む)

テスト方法およびプログラム

【課題】本発明によれば、コストおよびコンピュータの部品点数の増加を招くことなく、物理アドレスを再利用することが可能なテスト方法およびプログラムを実現する。

【解決手段】CPU111は、フロッピーディスク100等に格納されたテストプログラム200を実行する。テストプログラム200は、通信デバイス125の動作をテストする処理を実行する。CPU111は、通信デバイス125の動作不良が検出された場合、通信デバイス125の不揮発性メモリ131からMACアドレスを取得し、フロッピーディスク100に保存する。通信デバイス125が新たな通信デバイスに交換された後、CPU111は、新たな通信デバイスに、フロッピーディスク100に保存されたMACアドレスを保存する。

(もっと読む)

車載電子機器、故障検出方法

【課題】IEEE1394インターフェース以外の別のインターフェースで、そのIEEE1394システム機器と接続する必要なしにIEEE1394インターフェースの故障を検出できる車載電子機器を提供する。

【解決手段】接続ポートA182をIEEE1394システム機器24から切断し、接続ポートB183をIEEE1394システム機器21と接続し、ナビゲーション装置1と接続しているIEEE1394システム機器21〜24の台数を検出する。次に、接続ポートA182をIEEE1394システム機器24と接続し、接続ポートB183をIEEE1394システム機器21から切断し、ナビゲーション装置1に接続しているIEEE1394システム機器21〜24の台数を検出する。検出した台数とナビゲーション装置1に記憶されている接続台数ととより故障を検出し、故障している場合は、その故障している機器を特定する。

(もっと読む)

情報処理装置および情報処理方法

【課題】複数の装置により同一処理を実行する情報処理装置の信頼性を向上させる。

【解決手段】第1のステータス取得手段103は、第1の装置においてステータスを取得し、第2のステータス取得手段104は、第2の装置においてステータスを取得し、ステータス比較手段105は、第1のステータス取得手段103により取得されたステータスと、第2のステータス取得手段104により取得されたステータスとを比較する。ステータス選択手段106は、比較された両ステータスが異なる場合に第1のステータス取得手段103または第2のステータス取得手段104により取得されたステータスのいずれかを選択する。イベント発生手段102は、選択されたステータスに応じた共通のイベントを、第1の装置および第2の装置において発生させる。

(もっと読む)

情報処理装置およびシステムバス制御方法

【課題】ドライバやOSがPCI Express特有の機能に対応していない場合であっても、PCI Expressインターフェースのレーン数の縮退が発生した場合に適切な対処をおこなうことができる情報処理装置およびシステムバス制御方法を提供すること。

【解決手段】MMB400は、システムの初期化完了時に、Negotiated Link Widthレジスタ211cの値を参照し、この値を自身が有する記憶手段であるRAM420に記憶しておく。そして、OSやハードウェアから何らかの装置の異常の通知を受けた場合には、再度Negotiated Link Widthレジスタ211cの値を参照して、RAM420に記憶しておいた値と比較する。そして、両者の値が異なっていた場合には、レーン数の縮退が発生した旨のメッセージをコンソールに送信し、デバイスを切り離す等の所定の対応を実施する。

(もっと読む)

WAIT信号解除回路

【課題】 LSIが暴走したとき、LSIからCPUへ出力されているWAIT信号を解除して、CPUのハングアップを防ぐWAIT信号解除回路を得る。

【解決手段】 LSIから入力されたWAIT信号が所定時間以上継続したとき抵抗10、コンデンサ11、及びインバータ12によってエラー信号を発生させ、LSIから入力されたWAIT信号をCPUへ出力するORゲート13が、インバータ12からエラー信号を受けたときCPUへのWAIT信号出力を解除し、またエラー信号を受けたCPUがLSIをリセットしてLSIからのWAIT信号を解除する。

(もっと読む)

情報処理システム及びアクセス方法

【課題】IO要求のスループットを向上させる。

【解決手段】情報処理装置とストレージ装置に設定された複数の論理ユニットのそれぞれが、複数の論理的なパスで接続されたシステムにおいて、情報処理装置は、データのミラーリングを行うために複数の論理ユニットに対してデータの書き込み要求を発行する。また情報処理装置は、パスの状態を監視し、パスの状態変化があったときに論理ユニットに接続された正常なパスを求めて読出し要求の対象となる論理ユニットを決定し、決定された論理ユニットに対してデータの読出し要求を発行する。

(もっと読む)

試験装置及びその方法

【課題】本発明は、PCIバスを実装するコンピュータ製品の評価試験として、PCI信号のネゴシエーションが失敗した場合におけるRAS試験を確実に行うことができるようにする技術の提供を目的とする。

【解決手段】PCIバスネゴシエーション信号のサンプリングに用いられるリセット信号を所定の遅延時間だけ遅延させる遅延手段と、PCIバスネゴシエーションが失敗することになるPCIバスネゴシエーション信号の論理を設定する設定手段と、リセット信号の変化位置を検出する検出手段と、検出手段により検出された変化位置を基準として、リセット信号の遅延時間よりも長い時間、設定手段により設定された論理に従ってPCIバスネゴシエーション信号を変更する変更手段とを備えるように構成する。

(もっと読む)

PCIカード情報採取装置

【課題】システムの運用中にPCIカードの交換がされた場合でも、交換されたPCIカードのVID/DID情報を確実に採取する。

【解決手段】PCIカードが交換された後に、そのPCIカードに対してOS6から命令が出された場合、PCIカード情報採取装置7の発行制御部11において、その命令を停止し、替わりにVID/DID情報読み出し命令をそのPCIカードに対して出力する。受信制御部12では、発行制御部11により発行されたVID/DID情報読み出し命令に対する受信データをレジスタに保持しておく。診断プロセッサ3はVID/DID情報読み出し命令を発行することなく交換されたPCIカードのVID/DID情報を採取することが可能となり、OS6からのPCIカードリセット処理と診断プロセッサからのVID/DID情報読み出し命令の競合を発生させることなく、正しいVID/DID情報を採取できる。

(もっと読む)

1 - 20 / 20

[ Back to top ]