Fターム[5B125DB02]の内容

リードオンリーメモリ (43,397) | 書込動作 (3,780) | 書込動作 (910) | 同一ワード線内のセルの連続、同時書込 (554)

Fターム[5B125DB02]に分類される特許

1 - 20 / 554

ホスト装置、装置、システム

半導体記憶装置

半導体記憶装置

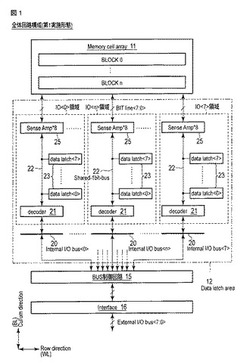

【課題】微細化に対して有利な半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、複数のメモリセルが配置されるメモリセルアレイ11と、前記複数のメモリセルのデータをラッチし、前記メモリセルアレイのデータの入力または出力(I/O)ごとに分割して配置される複数のアドレス領域(IO<0>領域〜IO<7>領域)と、前記複数のアドレス領域に対応して配置され、それぞれが前記複数のアドレス領域と電気的に直列に接続される内部バス配線20と、前記内部バス配線のデータ転送を制御する制御回路15とを具備する。

(もっと読む)

メモリシステム及びそれの動作方法

【課題】動作速度及び電力消耗を減らすことができるメモリシステム及びそれの動作方法が提供される。

【解決手段】本発明の実施形態によるメモリシステムは不揮発性メモリ装置と、前記不揮発性メモリ装置を制御するように構成されたメモリ制御器と、を含み、前記メモリ制御器は前記不揮発性メモリ装置から読み出されたデータのエラーの位置情報を含むエラーフラッグ情報を前記不揮発性メモリ装置へ提供する。

(もっと読む)

不揮発性メモリ装置、不揮発性メモリ装置のプログラム方法、不揮発性メモリ装置を含むメモリシステム

【課題】向上された信頼性を有する不揮発性メモリ装置のプログラム方法が提供される。

【解決手段】本発明のプログラム方法は、第1メモリセルトランジスターの閾値電圧がプログラム状態から移動する傾向を判別する段階と、判別結果に応答して、複数の検証電圧の中で第1検証電圧を選択する段階と、第1メモリセルトランジスターの閾値電圧が変化するように第1メモリセルトランジスターをプログラムする段階と、で構成される。プログラムする段階は第1メモリセルトランジスターの閾値電圧が十分に変化されたかを第1検証電圧を利用して検証する段階を含む。判別する段階は第1メモリセルトランジスターの閾値電圧の第1範囲からの変化を判別する段階を含む。

(もっと読む)

半導体記憶装置

【課題】読出速度が速い半導体記憶装置を提供する。

【解決手段】フラッシュメモリ3は、選択ビット線BLをプリチャージするプリチャージ回路45と、定電流源50と、電流検知型のセンスアンプ23と、選択ビット線BLがメモリアレイMA2に属する場合は、選択ビット線BLおよび定電流源50をそれぞれセンスアンプ23の入力ノードLBT,LBBに接続し、選択ビット線BLがメモリアレイMA3に属する場合は、選択ビット線BLおよび定電流源50を入力ノードLBB,LBTに接続する切換回路SWT2,SWB2,SWとを含む。したがって、ビット線BLのプリチャージとデータ読出を並列に実行できる。

(もっと読む)

不揮発性メモリ装置のデータリード方法、及びそれを行う装置

【課題】新たなリードパラメータで不揮発性メモリ装置をリードするリードリトライを行う方法、該方法を行う装置を提供する。

【解決手段】リードリトライ動作及び/またはその部属的なリードリトライ動作は、リードリトライ動作が保証(warranted)されるか否かを判断する前に初期化されるか、完了することができる。例えば、NANDフラッシュメモリ装置のページは、新たなリード電圧レベルをページのワードラインに印加して、リードリトライ動作でリードされうる。例えば、リードリトライ動作は、エラー訂正動作でターゲットページのデータの以前リードページのエラーを訂正不能と判断される前に、ターゲットページで行われる。

(もっと読む)

不揮発性半導体記憶装置

【課題】データ書き込みを高速化した不揮発性半導体記憶装置を提供することを目的とする。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、メモリセルアレイと、プログラム動作並びにベリファイ動作を有する書き込みループを繰り返し実行する制御回路とを備え、ベリファイ動作は、メモリセルの閾値電圧が、メモリセルの所望の閾値電圧の下限を示す本ベリファイ電圧よりも低い値で設定された予備ベリファイ電圧まで遷移したことを確認する予備ベリファイステップ、並びに、メモリセルの閾値電圧が本ベリファイ電圧まで遷移したことを確認する本ベリファイステップからなり、書き込みループは、各データに対応した1又は2以上のベリファイ動作からなり、制御回路は、所定の第1条件を具備した後、所定のデータに対応したベリファイ動作の予備ベリファイステップを省略させた書き込みループを実行する。

(もっと読む)

半導体記憶装置及びその制御方法

【課題】カラムブロックのデータラッチに対するデータの高速転送を可能にする。

【解決手段】半導体記憶装置1は、メモリセルアレイ2と、データバスDBと、転送制御部TC0〜TC2と、複数のカラムブロックC(0+4×i)〜C(3+4×i)と、カラムセレクタCSとを含む。カラムブロックおよびカラムセレクタはメモリセルアレイより下に形成される。データバスDBは複数のステージS0〜S3に分割される。転送制御部は複数のステージのそれぞれにデータが割り当てられるようにデータをシリアル転送する。カラムブロックは選択された場合にデータを一次記憶する。カラムセレクタCSはカラムブロックの中から、ステージごとにいずれかのカラムブロックを選択し、ステージごとに選択されたカラムブロックとの間でデータをパラレル転送する。データバスDBはカラムブロックの配列方向の一方の端側から他方の端側へ向かい、他方の端側で折り返す。

(もっと読む)

揮発性メモリ装置のマルチレベルセルプログラム方法

【課題】頁バッファをプレーンの中央部に位置させ、上側メモリレジスタと下側メモリレジスタを区分させる不揮発性メモリ装置を提供する。

【解決手段】第1メモリセルグループと接続される第1レジスタ及び第2メモリセルグループと接続される第2レジスタを含む頁バッファが提供され、各メモリセルに対して下位ビットプログラムを完了する段階と、第1レジスタのデータラッチ部の第1ノードに上位ビットデータを設定する段階と、上位ビットプログラムを行う段階と、第1検証電圧以上にプログラムされた場合、第1ノードに第1データを設定する段階と、第2検証電圧以上にプログラムされた場合、第1ノードに第1データと相反したレベルの第2データを設定する段階と、第3検証電圧以上にプログラムされた場合、第1ノードに第1データを設定する段階と、第1ノードに設定されたデータにより上位ビットプログラムを繰り返す段階を含む。

(もっと読む)

半導体記憶装置

【課題】インタリーブ動作を実行可能に構成された半導体記憶装置における更なる動作の高速化を図る。

【解決手段】複数のアドレス変換回路151a〜151dが、メモリコア11a〜11dの各々にそれぞれ設けられ、外部から供給される論理アドレスデータを物理アドレスデータに変換する。アドレス変換回路は、インタリーブ動作において第1のメモリコアが第2のメモリコアより先にアクセスされる場合には、論理アドレスデータを変換せず物理アドレスとして出力する一方、第2のメモリコアが第1のメモリコアより先にアクセスされる場合には、論理アドレスデータに所定値を加算したアドレスデータに対応する物理アドレスデータとして出力する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルの劣化による影響を考慮した読み出し動作を実行できる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施の形態に係る不揮発性半導体記憶装置は、メモリセルアレイと、読み出し動作及び書き込みベリファイ動作を制御する制御回路とを備える。制御回路は、第1の場合に、選択ワード線に印加する電圧を第1の書き込みベリファイ電圧又は第1の読み出し電圧に設定して、動作を行う。制御回路は、第1の場合よりもメモリセルの劣化が進んだ第2の場合に、選択ワード線に印加する電圧を第2の書き込みベリファイ電圧又は第2の読み出し電圧に設定して、動作を行う。制御回路は、第1の書き込みベリファイ電圧の最大値と第1の読み出し電圧の最大値との差を、第2の書き込みベリファイ電圧の最大値と第2の読み出し電圧の最大値との差よりも大きい値に設定する。

(もっと読む)

不揮発性半導体記憶装置及び不揮発性半導体記憶装置のデータ書き込み方法

【課題】セル間干渉によるしきい値電圧の変動を低減させる。

【解決手段】不揮発性半導体記憶装置は、第1及び第2の選択ゲートトランジスタ、並びに第1及び第2の選択ゲートトランジスタ間に設けられ電気的に書き換え可能なデータを記憶する複数のメモリセルが直列接続されたメモリストリングからなるセルユニットと、メモリセルに第1の選択ゲートトランジスタ側から第2の選択ゲートトランジスタ側へ下位ページデータ及び下位ページデータに応じた上位ページデータを順次書き込むデータ書き込み手段とを備える。データ書き込み手段は、選択メモリセルに対して下位ページデータを書き込む第1の書き込み動作と、選択メモリセルに対して第2の選択ゲートトランジスタ側に隣接するn個(nは2以上の整数)の非選択メモリセルに対する第1の書き込み動作が終了した後に、選択メモリセルに対して上位ページデータを書き込む第2の書き込み動作とを行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルの過消去を防止し、データの誤書き込みを低減した不揮発性半導体記憶装置を提供することを目的とする。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、メモリストリングに隣接するダミーに接続された第1配線、並びに、メモリセル毎に接続された第2配線を有するセルアレイを備え、ダミーセルに隣接する前記メモリセルを第1対象メモリセル、第1対象メモリセルに隣接する前記メモリセルを第2対象メモリセルとし、第1配線に印加される電圧を隣接第1配線電圧とし、第1対象メモリセルに接続された第2配線に印加される電圧を第2配線電圧とし、第2対象メモリセルに接続された第2配線に印加される電圧を第3配線電圧とした場合、駆動回路は、消去動作時において、第1配線電圧よりも第3配線電圧が小さい場合、第1配線電圧と第3配線電圧の差を第1配線電圧と第2配線電圧の差よりも小さくする。

(もっと読む)

不揮発性半導体記憶装置

【課題】高集積化を図ることができる不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、セルの書き込みにおいて、制御装置は複数の第2の選択ゲートトランジスタに第1電位を与えた後、第1電位よりも低い第2電位を与える。複数のビット線のうち、書き込み不十分のセルに第3電位を与え、書き込み終了に間近のセルに第3電位より高い第4電位を与え、書き込みが終わったセルに第4電位より高い第5電位を与える。制御装置は、第2電位を与えた後、複数のワード線のうち選択されたワード線に書き込み電位を与え、第1電位は、第2の選択ゲートトランジスタをオンすることにより第3電位をNANDストリングに転送する電位であり、第2電位は、第3電位をNANDストリングに転送した後、前記第2の選択ゲートトランジスタをオフする電位である。

(もっと読む)

不揮発性半導体記憶装置

【課題】 不揮発性半導体記憶装置の信頼性を、より向上させる技術が望まれている。

【解決手段】 閾値レベルの相違によって少なくとも4つのデータ状態が定義され、複数のデータ状態の各々に、複数ビットで構成される値が割り当てられるメモルセルがメモリ部に複数配置される。コントローラが、メモリセルの各々が記憶する複数ビットのうち、少なくとも1つのビットを、「正常」及び「異常」のいずれかの状態を表すエラー訂正ビットとし、他のビットを、データを記憶するためのデータビットとする。複数のデータ状態を、閾値レベルの大きさの順番に並べたとき、連続する4つのデータ状態のうち、閾値レベルが最小及び最大のデータ状態のエラー訂正ビットに「正常」を割り当て、閾値レベルが中間の2つのデータ状態のエラー訂正ビットに「異常」を割り当てる。周期的にメモリセルのエラー訂正ビットのデータを読み出し、読み出された値が「異常」である場合には、当該メモリセルのエラー訂正ビットを「正常」に再設定する。

(もっと読む)

不揮発性記憶装置

【課題】動作速度が高い不揮発性記憶装置を提供する。

【解決手段】実施形態に係る不揮発性記憶装置は、書込電圧を出力する駆動回路と、前記書込電圧が印加されることによってデータが書き込まれるメモリセルと、を備える。前記駆動回路は、前記書込電圧の出力をn回(nは3以上の整数)繰り返す場合に、k回目(kは2以上n以下の整数)の出力における前記書込電圧をVpgm(k)とし、一定電圧をΔv1とし、前記k回目の出力を継続する時間をTpgm(k)とし、一定時間をΔt1とするとき、前記書込電圧を下記数式を満たすように出力する。

Vpgm(k)=Vpgm(k−1)+Δv1

Tpgm(k)=Tpgm(k−1)+Δt1

(もっと読む)

不揮発性半導体記憶装置

【課題】正確に書き込み動作を行うことができる不揮発性半導体記憶装置を提供する。

【解決手段】

複数の素子分離絶縁膜は、半導体層中に形成され、第1方向を長手方向とする。複数の素子形成領域は、素子分離絶縁膜により分離して形成される。素子形成領域にはメモリストリングが形成される。複数の素子形成領域群が素子形成領域により構成される。メモリセルアレイは、第1方向と直交する第2方向において、前記素子形成領域群の間隔が前記素子形成領域群の中の前記素子形成領域の間隔より大きくされている。制御回路は、前記メモリセルアレイに対する書き込み動作を、前記素子形成領域群ごとに実行する。

(もっと読む)

半導体記憶装置

【課題】製造ばらつきにより生じる不良ブロックを判定可能な半導体記憶装置を提供する。

【解決手段】メモリセルと、複数の前記メモリセルを含むページ、複数の前記ページを含むブロックを有するメモリセルアレイと、前記ページのうち、第1カラムに対応する第1メモリセルにデータを書き込むとき、プログラム動作を繰り返した第1回数を保持する第1記憶部63と、前記ページのうち、前記第1カラムとは異なる第2カラムに対応する第2メモリセルにデータを書き込むとき、プログラム動作を繰り返した第2回数を保持する第2記憶部64と、第1回数と第2回数の差が規定値を超えたとき、前記第1メモリセルと前記第2メモリセルとを含むブロックを不良ブロックとして登録する制御部6とを備える。

(もっと読む)

半導体記憶装置

【課題】データの信頼性を向上可能な半導体記憶装置を提供する。

【解決手段】m個のページ(mは自然数)を含むメモリセルアレイと、書き込み動作を制御する制御回路とを備え、n番目のページ(1≦n≦mを満たす自然数)のメモリセルに書き込み動作で、(n+1)番目からm番目のページのメモリセルが消去状態とは異なる閾値を有するデータを保持するとき、前記制御回路は、フェイルを出力する。

(もっと読む)

1 - 20 / 554

[ Back to top ]