Fターム[5B125DD03]の内容

リードオンリーメモリ (43,397) | メモリ管理動作 (1,014) | 物理、論理アドレスの設定 (307) | アドレスの対応関係を変更 (154)

Fターム[5B125DD03]に分類される特許

1 - 20 / 154

メモリシステム及びそれのブロック複写方法

メモリシステム及びそれの動作方法

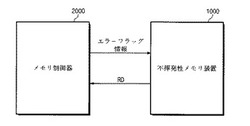

【課題】動作速度及び電力消耗を減らすことができるメモリシステム及びそれの動作方法が提供される。

【解決手段】本発明の実施形態によるメモリシステムは不揮発性メモリ装置と、前記不揮発性メモリ装置を制御するように構成されたメモリ制御器と、を含み、前記メモリ制御器は前記不揮発性メモリ装置から読み出されたデータのエラーの位置情報を含むエラーフラッグ情報を前記不揮発性メモリ装置へ提供する。

(もっと読む)

半導体記憶装置及び半導体集積回路

【課題】メモリセルの誤読み出しを抑制する。

【解決手段】内部アドレス生成部14が、連続する第1の外部アドレスと第2の外部アドレスを受信すると、第1の外部アドレスに応じて選択されるメモリセルに接続されるビット線及びワード線以外のビット線及びワード線に接続されるメモリセルの何れかを選択する内部アドレスを第2の外部アドレスから生成することで、連続する外部アドレスを受信したとき、続けて同じビット線及びワード線に接続されたメモリセルが選択されなくなり、非選択状態のメモリセルの値が書き変わることによる誤読み出しが抑制される。

(もっと読む)

半導体記憶装置

【課題】インタリーブ動作を実行可能に構成された半導体記憶装置における更なる動作の高速化を図る。

【解決手段】複数のアドレス変換回路151a〜151dが、メモリコア11a〜11dの各々にそれぞれ設けられ、外部から供給される論理アドレスデータを物理アドレスデータに変換する。アドレス変換回路は、インタリーブ動作において第1のメモリコアが第2のメモリコアより先にアクセスされる場合には、論理アドレスデータを変換せず物理アドレスとして出力する一方、第2のメモリコアが第1のメモリコアより先にアクセスされる場合には、論理アドレスデータに所定値を加算したアドレスデータに対応する物理アドレスデータとして出力する。

(もっと読む)

不揮発性半導体記憶装置

【課題】 不揮発性半導体記憶装置の信頼性を、より向上させる技術が望まれている。

【解決手段】 閾値レベルの相違によって少なくとも4つのデータ状態が定義され、複数のデータ状態の各々に、複数ビットで構成される値が割り当てられるメモルセルがメモリ部に複数配置される。コントローラが、メモリセルの各々が記憶する複数ビットのうち、少なくとも1つのビットを、「正常」及び「異常」のいずれかの状態を表すエラー訂正ビットとし、他のビットを、データを記憶するためのデータビットとする。複数のデータ状態を、閾値レベルの大きさの順番に並べたとき、連続する4つのデータ状態のうち、閾値レベルが最小及び最大のデータ状態のエラー訂正ビットに「正常」を割り当て、閾値レベルが中間の2つのデータ状態のエラー訂正ビットに「異常」を割り当てる。周期的にメモリセルのエラー訂正ビットのデータを読み出し、読み出された値が「異常」である場合には、当該メモリセルのエラー訂正ビットを「正常」に再設定する。

(もっと読む)

半導体記憶装置

【課題】複数のメモリマクロを備え、かつメモリマクロへの入出力を並行して行なうことができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置1は、複数個のメモリマクロ2_0〜2_Nと、外部と接続される複数個の外部端子P0_0〜PN_3を備える。各外部端子P0_0〜PN_3は、対応するメモリマクロと接続される。

(もっと読む)

不揮発性メモリ装置

【課題】信頼性を向上させることができる不揮発性メモリ装置の提供。

【解決手段】メモリセルアレイの選択されたページからデータを読み出すか、或いはメモリセルアレイの選択されたページへ書き込むように構成されたページバッファ回路と、選択されたページに割り当てられたシードに基づいて、ページバッファ回路へ伝送されるか、或いはページバッファ回路から伝送されるデータをランダム化及びデランダム化するように構成されたランダム化及びデランダム化回路と、を有し、選択されたページは複数のセグメントで構成され、ランダム化及びデランダム化回路は、選択されたページに割り当てられたシードに基づいて選択されたページのアクセス要請されたセグメントの各々に対するランダムシークェンスを生成するように構成され、シードにしたがって反復的に生成されたランダムシークェンスに基づいて各アクセス要請されたセグメントのデータをランダム化及びデランダム化するように構成される。

(もっと読む)

ページフラッグを有する不揮発性メモリ装置、それを含む駆動方法、及びメモリシステム

【課題】データをランダム化させて格納する不揮発性メモリ装置、それのプログラム方法及び読出し方法、及びそれを含むメモリシステムが提供される。

【解決手段】本発明による不揮発性メモリ装置のプログラム方法は、第1ページプログラム動作の時、前記第1ページプログラムの可否に関連された情報を有する第1ページフラッグをプログラムする段階及び第2ページプログラム動作の時、前記第2ページプログラムの可否に関連された情報を有する第2ページフラッグをプログラムする段階を含む。上述したように本発明による不揮発性メモリ装置は、データをランダム化させて格納することによって、データの信頼性を向上させる。また、本発明による不揮発性メモリ装置は、読出し動作の時、ページのプログラムの可否にしたがってランダム化の可否を決定することによって、読出しエラーを減らし得る。

(もっと読む)

不揮発性半導体記憶装置

【課題】リードディスターブを効率良く回避するための技術を提供する。

【解決手段】不揮発性半導体記憶装置(1)は、不揮発性記憶部(11)と、上記不揮発性記憶部の消去単位とされるブロック毎のデータを、当該ブロックとは異なるブロックに書き直すためのリフレッシュ処理を制御可能なコントローラ(12)とを含む。上記コントローラは、上記不揮発性記憶部に、第1領域とそれとは異なる第2領域とを設定し、上記第1領域のデータについてのリフレッシュ頻度が、上記第2領域のデータについてのリフレッシュ頻度に比べて高くなるように、リフレッシュトリガが発生される毎に上記第1領域及び上記第2領域についてのリフレッシュ処理を実行する。これにより、リードアクセスが繰り返される場合のリードディスターブを効率良く回避することができる。

(もっと読む)

ページ内・ページ間オンチップデータ擬似ランダム化のための不揮発性メモリおよび方法

【課題】集積回路メモリチップ内の機構により、不揮発性メモリセルアレイに蓄積されるデータのスクランブリングまたはランダム化を可能にする。

【解決手段】一実施形態において、検知中のソース負荷誤差と近傍セルのフローティングゲート間結合を抑制するため、ページ内ランダム化を役立てる。ページ単位ランダム化は、特定のデータパターンが繰り返し長期間にわたり蓄積されることから生じるプログラムディスターブ、ユーザリードディスターブ、フローティングゲート間結合を抑えるのに役立つ。別の実施形態では、ページ内ランダム化とページ単位ランダム化の両方を実施する。実施形態によってはスクランブリングまたはランダム化が予め決定されるか、あるいは符号生成擬似ランダム化となるか、あるいはユーザ主導ランダム化となる。これらの機構は、集積回路メモリチップの限られたリソースおよびバジェットの中で達成される。

(もっと読む)

非全単射写像を使用するマルチビットセルフラッシュメモリ装置

【課題】フラッシュコントローラにおいて、ECCと低次元非全単射写像との組み合わせを使用して、フラッシュのコスト、信頼性、及び性能の間での最適なトレードオフを実現する。

【解決手段】複数の入力ビットを記憶するために、ビットは、1つ又は複数のメモリセルの対応するプログラム状態に写像され、セルはその対応するプログラム状態にプログラムされる。写像は、多対1であってもよく、又は「中への」一般化グレイ写像であってもよい。セルは読み取られて、例えば、最尤復号化により、又は読み取り状態値を複数のソフトビットに写像し、次に、ソフトビットを復号化することにより、複数の出力ビットに変換される読み取り状態値を提供する。

(もっと読む)

半導体記憶装置、及び記憶媒体

【課題】ガベージコレクション処理による処理負荷を軽減し、ガベージコレクション処理の処理時間を短縮する。

【解決手段】フラッシュメモリ10は、予め定められたデータサイズ領域を示すページ単位でデータを書き込み可能な不揮発性記憶部11と、不揮発性記憶部11の指定された領域であって、複数のページを含む該指定された領域における有効データを一時記憶する記憶部12と、不揮発性記憶部11のページに有効なデータがあるか否かを示すアドレスマップ情報に基づいて、指定された領域における有効データを記憶部12に記憶させた後に、記憶部12に記憶された有効データを連続したページに書き込むガベージコレクション処理、及びガベージコレクション処理によって変更されたアドレスマップ情報を出力する処理を実行するコントロールロジック部13とを備える。

(もっと読む)

メモリシステム

【課題】メモリセルの状態を安定させることで信頼性を向上させることが可能なメモリシステムを提供する。

【解決手段】実施形態のメモリシステム1は、ワード線当たりのメモリセル群がn(n≧2)ページ分の記憶容量を有する不揮発性メモリと、ホストが指定する論理アドレスと前記不揮発性メモリ上のデータの位置を指定する物理アドレスとの対応を示すアドレス変換テーブルを管理するランダムアクセスメモリと、前記アドレス変換テーブルを前記ランダムアクセスメモリから前記不揮発性メモリにコピーするデータ確定処理を実行する前に、同一のワード線に対応する前記nページへの書き込みの書き込み順序におけるページ数単位での最大距離以上のページ分のダミーデータを、有効データを書き込んだ前記不揮発性メモリに引き続き書き込むメモリコントローラとを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】安定した動作を実行可能な不揮発性半導体記憶装置法を提供する。

【解決手段】メモリストリングは、電気的に書き換え可能な複数のメモリトランジスタ、及びスペアメモリトランジスタを直列接続してなる。ワード線は、メモリトランジスタのゲートに接続されている。スペアワード線は、スペアメモリトランジスタのゲートに接続されている。メモリストリングは、第1半導体層、電荷蓄積層、複数の第1導電層、及び第2導電層を備える。第1半導体層は、基板に対して垂直方向に延びる第1半導体層を含む。電荷蓄積層は、第1半導体層の側面を取り囲む。複数の第1導電層は、電荷蓄積層を介して第1半導体層の側面を取り囲みワード線として機能する。第2導電層は、電荷蓄積層を介して第1半導体層の側面を取り囲み、スペアワード線として機能する。制御回路は、ワード線に代えてスペアワード線を駆動可能である。

(もっと読む)

メモリシステム

【課題】SLCフラッシュメモリとMLCフラッシュメモリとのそれぞれのメリットを状況に応じて得る。

【解決手段】実施の形態によるメモリシステム1は、MLCフラッシュメモリ112と、ブロック管理部102と、転記部(107、108および109)と、を備える。MLCフラッシュメモリ112は、SLCモードおよびMLCモードのいずれでもデータの書込みが可能な複数のブロックを含む。ブロック管理部102は、有効データを格納しないブロックをフリーブロックとして管理する。転記部は、ブロック管理部102が管理するフリーブロックの数が所定の閾値Tbf以下である場合、有効データを格納する1つ以上の使用ブロックを転記元ブロックとして選択し、転記元ブロックに格納されている有効データをフリーブロックにMLCモードで転記する。

(もっと読む)

不揮発性半導体記憶装置

【課題】各物理ページの救済効率を向上させた不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、複数のワード線、前記複数のワード線に交差する複数のビット線、並びに前記ワード線及びビット線によって選択されそれぞれがNビット(N=2以上の整数)のデータを記憶可能な複数のメモリセルを有し、一の前記ワード線によって選択される複数のメモリセルの第nビット(n=1〜Nの整数)の集合は第nの物理ページを構成し、所定数の前記ビット線は、一のカラムを構成するメモリセルアレイと、外部から入力された前記物理ページ長以下の第1〜第Nの入力データをそれぞれ前記カラム長の単位データ毎に分割した後、データ書き込み前、所定の前記カラムの第1〜第Nの入力データの単位データをそれらの順序の少なくとも一部を同一カラム内で入れ替えて書き込むデータ書き込み部とを備えることを特徴とする。

(もっと読む)

不揮発性メモリコントローラ及び不揮発性記憶装置

【課題】任意に2値書き込み領域と多値書き込み領域とを設けた上で、それぞれの領域に対して物理的な領域制限を必要とせず、不揮発性メモリの全てのブロックを有効に利用することが可能な不揮発性メモリコントローラを提供する。

【解決手段】フラッシュメモリ部103は、複数のメモリセルを含み、データの消去単位である複数の物理ブロックを含み、メモリセルは、それぞれ1ビット以上の情報を記録可能であり、その特性の劣化量は、記録する情報量に応じて異なり、コントローラ102は、フラッシュメモリ部103に対してデータの読み出し、書き込み、及び消去の制御を行う制御部108と、物理ブロック単位でメモリセルの劣化度合いを記録するための劣化度テーブル113とを備え、制御部108は、物理ブロックに対する消去のサイクル毎に、メモリセルに格納する情報量に応じてメモリセルの劣化度合いを劣化度テーブル113に記録する。

(もっと読む)

不揮発性記憶装置および不揮発性メモリコントローラ

【課題】特に高いデータ保持信頼性が要求される読み出し専用のデータに対し、データ保持信頼性向上のためのリフレッシュ処理が適用された場合に、データ保持信頼性を維持する。

【解決手段】論理アドレスを複数の領域に分割し、分割された領域のデータに対しレベリング処理の適用を許可/禁止を示す領域指定テーブル112と、読み出し専用の物理ブロックのデータのリフレッシュ時に使用する物理ブロックのアドレスを登録した無劣化ブロックテーブル113と、アドレス変換テーブル109と、制御部108とECC回路107を有する不揮発性記憶装置101において、レベリング処理を禁止する領域の読み出し時に、ECC訂正ビット数が所定ビット数以上であることを検出した場合は、無劣化ブロックテーブルの物理ブロックを選択してデータをコピーするリフレッシュ処理を行う。

(もっと読む)

メモリシステム

【課題】ロット・個体・チップ・ブロック間などの書き込み・消去回数の耐性のばらつきを考慮して、従来に比べてシステム全体の寿命が長い、或いは信頼性の高いメモリシステムを提供すること。

【解決手段】データ消去の単位であるノーマルブロック1〜nを複数とダミーブロックDとを有する不揮発性半導体メモリ10と、前記ダミーブロックDに複数の前記ノーマルブロック1〜nの書き換え回数の最大回数以上の書き換えを行う書き込み制御部13と、前記ダミーブロックDのデータ消去時間或いは書き込み時間をモニタするモニタ部11と、前記ノーマルブロック1〜n間の書き換え回数を平均化させるウェアレベリング制御部12とを備え、前記モニタ部11のモニタ結果に基づいて前記ノーマルブロック1〜nの書き換え継続可否を決定する。

(もっと読む)

記憶装置および記憶システム

【課題】既にデータを保持している記憶領域に対して新たなデータの追加書込みが可能な記憶装置において、追加書込みによる書き込み済データの消失を防ぐ。

【解決手段】記憶装置1は、既にデータを保持する記憶領域に対して新たなデータを追加書込みすることにより当該記憶領域においてこれらのデータを保持可能なメモリ15と、書込みアクセスにおいて書込みデータが入力される入出力部11と、書込みアクセスに基づいてメモリ15に書込みデータを書込む制御部28とを有する。制御部28は、書込みアクセスに基づく内部処理において、当該処理において書込みデータを書込んだ記憶領域についての追加書込み処理を実行する。

(もっと読む)

1 - 20 / 154

[ Back to top ]