Fターム[5B125DE14]の内容

リードオンリーメモリ (43,397) | その他の動作 (2,583) | コピー、複写、転写動作 (184)

Fターム[5B125DE14]に分類される特許

1 - 20 / 184

メモリシステム及びそれのブロック複写方法

ホスト装置、装置、システム

半導体記憶装置

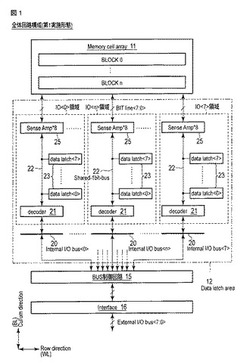

【課題】微細化に対して有利な半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、複数のメモリセルが配置されるメモリセルアレイ11と、前記複数のメモリセルのデータをラッチし、前記メモリセルアレイのデータの入力または出力(I/O)ごとに分割して配置される複数のアドレス領域(IO<0>領域〜IO<7>領域)と、前記複数のアドレス領域に対応して配置され、それぞれが前記複数のアドレス領域と電気的に直列に接続される内部バス配線20と、前記内部バス配線のデータ転送を制御する制御回路15とを具備する。

(もっと読む)

メモリシステム及びそれの動作方法

【課題】動作速度及び電力消耗を減らすことができるメモリシステム及びそれの動作方法が提供される。

【解決手段】本発明の実施形態によるメモリシステムは不揮発性メモリ装置と、前記不揮発性メモリ装置を制御するように構成されたメモリ制御器と、を含み、前記メモリ制御器は前記不揮発性メモリ装置から読み出されたデータのエラーの位置情報を含むエラーフラッグ情報を前記不揮発性メモリ装置へ提供する。

(もっと読む)

半導体記憶装置

【課題】インタリーブ動作を実行可能に構成され且つLMアドレススキャン動作を実行する半導体記憶装置における消費電力の削減、及び動作の高速化を図る。

【解決手段】複数のカラムのうちの少なくとも1つは、複数ビットのデータの書き込み動作の進行状況を示すLMフラグデータを記憶するためのLMカラムである。カラム制御回路の各々は、対応するメモリコアにLMカラムが存在するか否かを確認するためのLMアドレススキャン動作をする。そのLMアドレススキャン動作の結果をレジスタに格納し、その後の各種動作においては、前記データラッチ回路に保持されたデータが第1のデータである場合、そのメモリコアにおいて前記LMカラムからLMフラグデータを読み出す動作を実行する一方、前記レジスタに保持されたデータが第2のデータである場合、そのメモリコアにおいて前記LMカラムからLMフラグデータを読み出す動作を実行しない。

(もっと読む)

半導体記憶装置

【課題】ライトパラメータを効率よく探索することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、パラメータセットを初期値から変更して生成した新たな2以上のパラメータセットを用いて半導体メモリセルに情報を書き込み、その半導体メモリセルについて変換回路の出力を取得し、変換回路の出力の最大値が得られたパラメータセットと、最小値が得られたパラメータセットとをパラメータ空間上で結ぶ延長上に位置する、他のパラメータセットを、新たな初期値として設定して検証を再実施し、書き込んだ情報と読み出した情報が一致する半導体メモリセルについては、初期値を用いた検証を終了する。

(もっと読む)

半導体記憶装置

【課題】回路面積の縮小を図る。

【解決手段】半導体記憶装置は、第1メモリセルに接続される第1ワード線CG1と、第2メモリセルに接続される第2ワード線CG2と、各メモリセルに対する書き込み動作を制御し、第1ワード線および第2ワード線と電気的に接続された電源回路21を有する制御回路2と、第1ワード線と電源回路の間に設けられた第1転送スイッチCGSW1と、第2ワード線と電源回路の間に設けられた第2転送スイッチCGSW2と、を具備する。制御回路は、第1メモリセルに対する書き込み動作において、第1時刻で、第1転送スイッチおよび第2転送スイッチをオンし、第1ワード線および第2ワード線を昇圧させて、第1時刻後の第2時刻で、電源回路と第2ワード線との電気的な接続を切断して第2ワード線を浮遊状態とし、第2ワード線は書き込みパス電圧まで到達する。

(もっと読む)

半導体記憶装置及びその試験方法

【課題】ローデコーダ側に配置される転送トランジスタの特性評価を実施する。

【解決手段】一つの実施形態によれば、半導体記憶装置は、切り替え部、第一の転送トランジスタ、第一のトランジスタ、及び第二のトランジスタが設けられる。切り替え部が第一の状態のときに第一及び第二のトランジスタがオフし、第一の転送トランジスタがオンし、切り替え部が第二の状態のとき第一及び第二のトランジスタがオンする。

(もっと読む)

フラッシュメモリ装置

【課題】フラッシュメモリ装置において、ブロック間で最新値をコピーしている間にリセットが発生した場合であっても、真の最新値を認識することにある。

【解決手段】ブロック管理値をアクティブ状態とする際に、ブロック管理値がブロック毎に異なるとともに順に大きくなるように設定される。例えば、ブロック管理値として第1のブロックB1には「$1111」が、第2のブロックB2には「$1112」が記憶される。このため、たとえ、アクティブ状態であるブロックが複数存在する場合であっても、ブロック管理値が大きいブロックの最新値を読み出すことで、真の最新値を読み出すことができる。

(もっと読む)

記録再生装置

【課題】フラッシュメモリの劣化をより迅速に検出できる。

【解決手段】速度導出部180は、SSD136に対するデータの読み書き速度を導出する。速度保持部138は、速度導出部が導出した読み書き速度を保持する。劣化判定部182は、任意の時点のSSDに対するデータの読み書き速度の、速度保持部に保持されている任意の時点より前の読み書き速度に対する変化率を導出し、導出された変化率が所定の閾値以下となると、SSDが劣化していると判定する。報知部184は、劣化判定部が、SSDが劣化していると判定した場合、その旨報知する。

(もっと読む)

不揮発性半導体記憶装置

【課題】3次元型の半導体記憶装置のパフォーマンスの向上を図る。

【解決手段】

制御回路は、メモリセルに与えられる複数の閾値電圧分布の下限と上限との間の電圧である読み出し電圧を、選択された前記ワード線に印加することにより、メモリセルが保持するデータを読み出す読み出し動作を実行する。更に制御回路は、読み出し電圧よりも大きいベリファイ電圧を選択されたワード線に印加してメモリセルの読み出しを行うことにより、書き込み動作が完了したか否かを判定するベリファイ動作を実行する。そして制御回路は、選択されたワード線に接続された複数のメモリセルそれぞれの閾値電圧が所定値以下であるか否かを判定し、複数のメモリセルにおいて所定数以上のデータ変動が発生したか否かを判定するデータ変動判定動作を実行する。

(もっと読む)

半導体記憶装置

【課題】

実施形態は、メモリセルの信頼性を向上可能な半導体記憶装置を提供する。

【解決手段】

本実施形態の半導体記憶装置によれば、複数のメモリセルを有するメモリセルアレイと、前記メモリセルのデータを消去する場合において、消去後に第1データを書き込む予定のメモリセルの第1閾値分布を、消去後に第2データを書き込む予定のメモリセルの第2閾値分布より低くする制御回路とを備え、前記第1データを有するメモリセルの閾値分布は、前記第2データを有するメモリセルの閾値分布より低いことを特徴とする。

(もっと読む)

メモリシステム

【課題】

実施形態は、動作効率の低減を防止可能なメモリシステムを提供する。

【解決手段】

本実施形態のメモリシステムによれば、半導体チップの内部温度とアクセス可否とを対応づけたデータを保持する第1記憶部と、前記半導体チップの内部温度を計測する温度計測部と、前記データから、計測された内部温度に対応するアクセス可否を算出し、アクセス可の半導体チップに対して、シーケンスを実行し、アクセス否の半導体チップに対して、シーケンスを実行しない制御部とを備えることを特徴とする。

(もっと読む)

不揮発性半導体メモリ

【課題】フェイルビット数を高速に検知する。

【解決手段】実施形態に係わる不揮発性半導体メモリは、第1の単位のデータをz個の第2の単位のデータに分け、各第2の単位のデータについてフェイルビットを累積するアキュムレータ12と、書き込み後にフェイルビットを検知する動作を制御する制御回路10とを備える。制御回路10は、各第2の単位のデータについて、そのうちの第3の単位のデータをセンスアンプSA0に記憶させ、センスアンプSA0から、各第2の単位のデータを1ビットずつ、合計zビットずつパラレルに読み出し、検知回路DTCT0を用いてzビットからフェイルビットを検知し、zビットをアキュムレータ12に転送することにより、各第2の単位のデータについてフェイルビットを累積する。

(もっと読む)

半導体記憶装置

【課題】1つの実施形態は、例えば、出荷後においてメモリセルの動作特性を変更できる半導体記憶装置を提供することを目的とする。

【解決手段】1つの実施形態によれば、メモリセルアレイと記憶部と選択部と起動処理部と動作制御部とを有することを特徴とする半導体記憶装置が提供される。メモリセルアレイでは、複数のメモリセルが配列されている。記憶部は、選択される候補となる複数の動作パラメータを予め記憶する。選択部は、ユーザからの変更指示に応じて、前記複数の動作パラメータのうち前記メモリセルを動作させるために使用すべき動作パラメータを選択する。起動処理部は、ユーザからの起動指示に応じて、電源を起動するとともに、前記選択部により選択された動作パラメータを前記記憶部から読み出して使用可能な状態に設定する。動作制御部は、前記起動処理部により使用可能な状態に設定された動作パラメータを使用して、前記メモリセルを動作させる。

(もっと読む)

メモリシステム

【課題】書き換え回数制限下での実効的な書き換え容量を増大したメモリシステムを提供する。

【解決手段】実施形態のメモリシステム1は、2ビット以上の所定ビット数の記憶容量のメモリセルを複数個有する不揮発性メモリ2と、前記メモリセルの書き換え回数を管理する書き換え回数管理テーブル40を備える。実施形態のメモリシステムは、ホスト7からの書き込み要求に応じたビット数で前記メモリセルに書き込みを行い、前記書き換え回数管理テーブル40が管理する前記メモリセルの書き換え回数が所定の回数を超えた後は、前記メモリセルを前記記憶容量に依存したグループに分割し、ホストからの書き込み要求に応じたビット数の前記記憶容量に対応する前記グループの前記メモリセルに書き込みを行うコントローラ3を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】データ転送速度の切り替えが可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1は、不揮発性メモリ10と、第1の制御信号の立ち上がりエッジ及び立ち下がりエッジの一方に応答してデータ転送を行う第1のモードと、第2の制御信号の立ち上がりエッジ及び立ち下がりエッジの両方に応答してデータ転送を行う第2のモードとを有し、データ入力時に第1のモードを用いかつデータ出力時に第2のモードを用いるように第1及び第2のモードを切り替えるコントローラ17とを含む。

(もっと読む)

半導体記憶システム

【課題】 複数のチップを実装した場合において、消費電流の増加を抑制することが可能な半導体記憶システムを提供する。

【解決手段】 半導体記憶システムは、第1の半導体記憶装置71aと、第2の半導体記憶装置71bと、配線83とを有している。配線83は、第1の半導体記憶装置71aと第2の半導体記憶装置間71bに接続されている。第1、第2の半導体記憶装置71a,71bの一方が電荷を放電するとき、第1、第2の半導体記憶装置71a,71bの他方は、配線83を介して放電された電荷を受ける。

(もっと読む)

半導体メモリおよびシステム

【課題】 プリチャージ動作を不要にすることで、読み出しアクセス時間を短縮する。

【解決手段】 メモリセルは、第1電圧線と第2電圧線の間に接続ノードを介して直列に接続され、相補の論理を記憶する一対のセルトランジスタを有する。第1制御回路は、読み出し動作時に、一対のセルトランジスタのコントロールゲートを活性化レベルに設定する。第2制御回路は、読み出し動作時に、第1電圧線を第1電圧に設定し、第2電圧線を第1電圧より高い第2電圧に設定する。読み出し回路は、読み出し動作時に、接続ノードに生成される電圧に応じて、メモリセルに保持されている論理を判定する。これにより、読み出し動作において、メモリセルに保持されている論理に応じて、接続ノードを第1電圧または第2電圧に設定できる。

(もっと読む)

不揮発性メモリ装置及びメモリコントローラとこれらの動作方法、メモリシステムの動作方法、並びにウェアレベリング方法

【課題】メモリセルの劣化度を正確に検出することができる不揮発性メモリ装置及びメモリコントローラとこれらの動作方法、メモリシステムの動作方法、並びにウェアレベリング方法を提供する。

【解決手段】本発明の不揮発性メモリ装置の動作方法は、コントローラから出力されたブロックアドレスとイレース命令とを受信する段階と、ブロックアドレスに相応するブロックに対して、イレース命令によって行われるイレース動作が完了するまで、イレース動作に関連したパラメータ値を変更する段階と、最後に変更されたパラメータ値に相応する情報を保存する段階と、コントローラから出力された命令によって、情報をコントローラに伝送する段階と、を有する。

(もっと読む)

1 - 20 / 184

[ Back to top ]