Fターム[5B125EK06]の内容

リードオンリーメモリ (43,397) | 外部接続構成、外部出力情報 (1,198) | メモリの状態情報の出力 (341)

Fターム[5B125EK06]の下位に属するFターム

レディ、ビジー信号 (100)

書込状態、消去状態情報 (37)

保護情報 (12)

エラー情報 (147)

Fターム[5B125EK06]に分類される特許

1 - 20 / 45

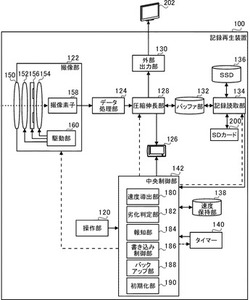

記録再生装置

【課題】フラッシュメモリの劣化をより迅速に検出できる。

【解決手段】速度導出部180は、SSD136に対するデータの読み書き速度を導出する。速度保持部138は、速度導出部が導出した読み書き速度を保持する。劣化判定部182は、任意の時点のSSDに対するデータの読み書き速度の、速度保持部に保持されている任意の時点より前の読み書き速度に対する変化率を導出し、導出された変化率が所定の閾値以下となると、SSDが劣化していると判定する。報知部184は、劣化判定部が、SSDが劣化していると判定した場合、その旨報知する。

(もっと読む)

不揮発性半導体記憶装置、及び読み出し電圧検出方法

【課題】読み出し動作の信頼性が高い不揮発性半導体記憶装置、及び読み出し電圧検出方法を提供する。

【解決手段】不揮発性半導体記憶装置100は、自装置の外部から第1データを取得するデータ入力バッファ102と、印加された電圧の電圧値に応じて第2データを出力する複数のメモリセルを有するNANDメモリセルアレイ108と、選択されたページに属するメモリセルに電圧値が順次変化する電圧を印加するワード線電圧制御回路107と、メモリセルから取得した第2データのエラーを検出するエラー検出回路104と、メモリセルから第2データを出力させるための読み出し電圧の最適値をエラーが検出された際にメモリセルに印加されていた電圧の電圧値に基づいて検出するワード線電圧補正回路106と、最適値を表すコードを自装置の外部に出力するデータ出力バッファ111とを備える。

(もっと読む)

半導体記憶装置、及び記憶媒体

【課題】ガベージコレクション処理による処理負荷を軽減し、ガベージコレクション処理の処理時間を短縮する。

【解決手段】フラッシュメモリ10は、予め定められたデータサイズ領域を示すページ単位でデータを書き込み可能な不揮発性記憶部11と、不揮発性記憶部11の指定された領域であって、複数のページを含む該指定された領域における有効データを一時記憶する記憶部12と、不揮発性記憶部11のページに有効なデータがあるか否かを示すアドレスマップ情報に基づいて、指定された領域における有効データを記憶部12に記憶させた後に、記憶部12に記憶された有効データを連続したページに書き込むガベージコレクション処理、及びガベージコレクション処理によって変更されたアドレスマップ情報を出力する処理を実行するコントロールロジック部13とを備える。

(もっと読む)

不揮発性記憶装置及びデータ保持状態監視方法

【課題】 より簡易な構成でかつ高精度に無電源期間のデータ保持状態をモニタすることができる不揮発性記憶装置を提供する。

【解決手段】 不揮発性記憶装置1を、データ記憶部2と、参照メモリセル部3と、状態検出部4と、制御回路部5とを備える構成とし、各部の構成及び機能を次のようにする。参照メモリセル部3は、非動作期間のデータ保持状態を検出するための参照メモリセル3aを含む。状態検出部4は、参照メモリセル3aの状態を検出する。そして、制御回路部5は、状態検出部4での検出結果に基づいて、非動作期間のデータ保持状態を特定する。

(もっと読む)

不揮発性半導体記憶装置、及び、メモリシステム

【課題】データ保持特性を向上することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、複数のメモリセルをそれぞれ含む複数のブロックを有し、前記複数のブロックのうちの通常ブロックに、通常のデータが記憶され、前記複数のブロックのうちのタイムコードブロックに、前記通常ブロック毎に設定され且つ前記通常ブロックの最後の書き込み動作を実行した時間に対応する時間データを含むタイムコードが記憶されたメモリセルアレイを備える。前記不揮発性半導体記憶装置は、前記タイムコードブロックから前記タイムコードを読み出し、現在の時間を取得し、読み出された前記タイムコードの時間データの時間と前記現在の時間との時間差が規定値よりも大きくなる選定された前記通常ブロックに対して、データを読み出し、消去し、且つ、読み出されたデータを書き込み、前記現在の時間の時間データに対応する新たなタイムコードを、選定された前記通常ブロックに対応させて、前記タイムコードブロックに書き込む。

(もっと読む)

メモリシステム

【課題】複数のブロックで構成された不揮発性半導体メモリ全体の劣化状態を正確に検出することができるメモリシステムを提供すること。

【解決手段】メモリシステムにおいて、データ消去の単位であるブロックを複数個有する不揮発性半導体メモリであるNANDメモリ20と、NANDメモリ20のデータ書き込みに要するNANDメモリ20への印加電圧のループ回数を書き込み時ループ回数としてモニタする書き込み時ループ回数モニタ部13と、書き込み時ループ回数をブロック単位に管理するための管理テーブルと、管理テーブルに基づいてNANDメモリ20の劣化状態を判定する寿命管理部14と、を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】本発明は、プログラムベリファイ機能を有するNAND型フラッシュメモリにお

いて、記憶データを高速に検索できるようにする。

【解決手段】たとえば、フラッシュメモリは、逆引き検索モードにおいて、各ブロックの

先頭ページより、そのブロックに記憶された記憶データに対応する検索データを読み出し

、その検索データとコントローラからの非検索データとを比較し、非検索データに一致す

る検索データのブロックアドレスおよびページアドレスをコントローラに送り返す。その

際に、フラッシュメモリは、自身が備えるプログラムベリファイ機能を利用して“0”デ

ータを比較することにより、検索データと非検索データとの一致をチェックする。

(もっと読む)

記憶装置

【課題】多値メモリセルアレイの端部において信頼性を向上させるとともに、クラスタ単位での書き込みにおける性能を向上させる記憶装置を提供する。

【解決手段】複数のメモリセルブロックを有し、メモリセルブロックはmビット(mは2以上の自然数)のデータを記憶可能に構成された複数の多値メモリセルがp行(pは3以上の自然数)のワード線と、q列(qは2以上の自然数)のビット線の交差部に配置されており、ワード線はそれぞれ第1ページ〜第mページのm個のページを有し、メモリセルブロックはn個(nは n<m×p を満たす自然数)のページを有し、すくなくとも1以上の端部ではないワード線には、m個のページの全てにページ番号が割り当てられると共にワード線の少なくとも一方の端部のワード線にページ番号が割り当てられた第1ページと、ページ番号が割り当てられない第mページとを有する記憶装置。

(もっと読む)

半導体装置

【課題】消去時間の短縮を行なうとともにデータアクセスを効率的に実行することのできる不揮発性メモリ機能を有する半導体装置を提供する。

【解決手段】コマンドレジスタ/制御回路(24)の制御のもとに、メモリセル境界領域に配置される埋込消去ゲート配線(4)に対して消去電圧を印加し、フローティングゲート(FG)と埋込消去ゲートEGの間で電荷を移動させて消去動作を行なうとき、消去電圧印加中にメモリゲート線(MGL)およびアシストゲート線(AGL)に読出選択電圧を印加してデータの読出を実行する。

(もっと読む)

フラッシュメモリのデータ処理方法及び記憶装置

【課題】データコピー及び元ブロックデータ消去に伴うデータ書き込み時間の遅延を抑制できるフラッシュメモリのデータ処理方法及び記憶装置を提供する。

【解決手段】フラッシュメモリのデータ処理方法であって、データ書き込みとは異なるタイミングで、ブロックにおけるデータ書き込み状態を検出し、検出した書き込み状態が、予め設定された所定の書き込み状態に対応するデータ移行条件と合致する場合、ブロックに対応するアプリケーションの実行手段に、該当するブロックのレコードのうち、有効なレコードのデータのみを、ブロックとは別の記憶媒体に移行するタイミングである旨を通知する。そして、通知を受け、アプリケーションの移行条件と合致することでなされる実行手段からの指示に基づき、該当するブロックの有効なレコードのデータのみを、記憶媒体にコピーするとともに、データコピー元のブロックのデータを消去する。

(もっと読む)

半導体記憶装置およびその制御方法

【課題】データリテンションの劣化によるデータの破壊を抑制できる半導体記憶装置およびその制御方法を提供する。

【解決手段】半導体記憶装置は、メモリセルアレイ11と、メモリセルに実際の読み出しレベルのパラメータで読み出しを行った、第1読み出しデータをラッチする第1データラッチ回路DL1と、前記メモリセルに前記実際の読み出しレベルより高くシフトさせたレベルのパラメータにて読み出しを行った、第2読み出しデータをラッチする第2データラッチ回路DL2と、前記第1,第2読み出しデータを演算する演算回路CBと、前記演算回路の演算結果において前記第1読み出しデータと前記第2読み出しデータとの差異の数データの数(N)をカウントするカウンタ回路BSと、前記数(N)と基準数(M)との大小比較を行い、N≧Mの場合は、フラグ情報を外部に出力するよう制御する制御回路17とを具備する。

(もっと読む)

ディスクドライブ装置及び不揮発性メモリ制御方法

【課題】エラーが発生した不揮発性メモリを即座に使用中止せずに、不揮発性メモリの信頼性(エラー履歴)に合わせてデータの読み書きを制御することで、使用可能なメモリ容量の減少を最小限にすることができるディスクドライブ装置を提供する。

【解決手段】ディスクドライブ装置10は、不揮発性メモリディスク12を構成する所定のメモリ単位毎にエラー発生回数を記憶するメモリ111aと、エラー発生回数毎に予め設定された複数個のメモリ単位に対して同じデータを重複して書き込むデータ制御部114と、同じデータが重複して書き込まれた複数個のメモリ単位から複数個のデータを読み込み、複数個の読み込みデータに対して多数決判定を行い、最も数が多い読み込みデータを最尤値として決定する読み込みデータ処理部112とを備える。

(もっと読む)

不揮発性半導体メモリ装置および不揮発性半導体メモリ装置のデータ記憶方法

【課題】データを長期間保存しこのデータの読み書き動作が長期間行われないメモリセルにおけるデータリテンション不良を防ぎ、不揮発性半導体メモリのデータ保持特性の十分な向上を図る。

【解決手段】不揮発性半導体メモリ装置(1)に、メモリセル領域(11)を構成している、任意のデータが保持されているメモリセル(A,B,…,N,…)の状態がデータの保持に及ぼす影響を検知する状態検知回路(13)と、前記状態検知回路の動作開始周期を決定する検知周期制御部(12)と、前記状態検知回路によるメモリセルの状態検知の結果に基づいたデータ書き込みを実行するデータ保持制御回路(14)とを備えた。

(もっと読む)

不揮発性メモリコントローラ、不揮発性記憶装置、及び不揮発性記憶システム

【課題】一般的なセクターデータの書き込みはランダムなデータではなく、データ“0”とデータ“1”の発生頻度の偏った特徴的なデータである。そういった偏ったセクターデータを不揮発性メモリに書き込むと不良が発生する確率が高くなる。書き込みデータにおけるデータ“0”とデータ“1”の発生頻度の偏りを解消し、信頼性の高い不揮発性記憶装置を実現する。

【解決手段】不揮発性記憶装置において、カテゴリ分析機能部でセクターデータにおけるデータの“0”とデータ“1”の発生頻度からカテゴリを決定し、スクランブルパターン発生器でデータが書き込まれるアドレス位置の情報と前記カテゴリから決定したスクランブルパターンを発生し、スクランブル回路でセクターデータのスクランブルを行い、前記カテゴリとともに不揮発性メモリに書き込む。

(もっと読む)

メモリ制御回路およびそのメモリ制御回路を搭載した電子機器

【課題】NOR型フラッシュメモリの消費電力を低減する技術を提供する。

【解決手段】通常状態とスタンバイ状態とDPD(Deep Power Down)状態との切り替えが可能な半導体記憶装置と、前記半導体記憶装置のデータの読み出しと書込みを実行する演算処理装置とを具備する半導体装置を構成する。前記演算処理装置は、前記半導体記憶装置に対するアクセス要求を出力するCPUコアと、前記半導体記憶装置の状態を制御するメモリ制御部とを含むことが好ましい。そして、前記メモリ制御部は、予め設定された規定時間に、前記半導体記憶装置に対するアクセス要求を受け取らなかったとき、前記半導体記憶装置を前記DPD状態に移行させる。

(もっと読む)

半導体記憶装置及びホスト装置

【課題】所望するデータ保持期間に応じて半導体記憶装置を有効に使うために、所望するデータ保持期間に対して許容される書き換え回数の残りを求め、表示することを目的とする。

【解決手段】保持期間設定手段14は、半導体記憶装置1Aに対して要求されるデータ保持期間を設定する。限界回数算出手段15Aは、フラッシュメモリ10の書き換え回数とデータ保持期間との関係を予め保持し、データ保持期間を基にしてフラッシュメモリ10の限界書き換え回数を算出する。書換回数計数手段16Aは、フラッシュメモリ10の書き換え回数を算出する。ホスト装置2Aの警告手段21は、限界書き換え回数から書き換え回数を差し引いて求めた残書き換え可能回数、及び残書き換え可能回数に応じた警告信号を出力する。表示手段18は、取得した残書き換え可能回数を表示するか、警告信号に基づいた警告を表示する。

(もっと読む)

半導体記憶装置及び不揮発性メモリ

【課題】複数のページ間でパリティに使用するビット数を有効に割り振り、ビットエラー発生率が高いページに対して訂正能力の高い誤り訂正を行える半導体記憶装置及び不揮発性メモリを提供することである。

【解決手段】半導体記憶装置300はメモリコントローラ100と不揮発性メモリ200を備える。不揮発性メモリは、複数のページで構成され、データとそのパリティが記憶される。メモリコントローラは、不揮発性メモリへのデータ書込み時は、ホスト機器から入力したデータにパリティを付加して不揮発性メモリに記憶し、データ読出し時は、不揮発性メモリからデータとそのパリティを読み出して誤り箇所を検出し、データ誤り訂正を行う機能を有する。メモリコントローラは、不揮発性メモリに記憶可能な複数のページのうちの所定数のページで使用可能な全てのパリティのビット数を、各ページのエラー発生率の大きさに応じて各ページ毎に割り振る。

(もっと読む)

不揮発性半導体記憶装置

【課題】最適動作条件の変動に対応可能とした不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、電気的書き換え可能な不揮発性メモリセルが配列されたメモリセルアレイと、動作制御に用いられる制御データを保持する第1のレジスタ群9−1と、前記メモリセルアレイ内に設定された、前記制御データを微調整するための調整データを記憶する調整データ記憶領域と、前記調整データ記憶領域から読み出された調整データを保持する第2のレジスタ群9−2と、を有する。

(もっと読む)

不揮発性メモリカード

【課題】不揮発性メモリとそのコントローラ部での各々の電圧検出器間の検出誤差による問題を生じることがなく、かつ回路規模を減少することが可能な不揮発性メモリカードを提供することである。

【解決手段】不揮発性メモリカード100Aは、不揮発性メモリ110Aとそのコントローラ部120Aを具備し、不揮発性メモリ110A及びコントローラ部120Aはそれぞれに対応して第1のロジック部111及び第2のロジック部121を備え、不揮発性メモリ110Aは不揮発性メモリ及びコントローラ部へ外部から供給される電源電圧を検出する電圧検出器112bを備え、その検出出力を電圧検出器が設けられている不揮発性メモリの第1のロジック部に供給すると同時に、バッファアンプを介してコントローラ部の第2のロジック部又は/及び追加した1つ以上の不揮発性メモリ110Bのロジック部111’に供給可能とする。

(もっと読む)

フラッシュメモリ

【課題】電荷保持能力を回復することが可能なフラッシュメモリを提供する。

【解決手段】フラッシュメモリ10は、フラッシュメモリ回路が形成された半導体チップ16と、フラッシュメモリ回路に対してアニーリング処理を行うヒータ13と、を備える。また、フラッシュメモリ10は、フラッシュメモリ回路の温度を計測する温度センサ11と、温度センサの検出値に基づいて所定のアニーリング条件に従ってヒータを制御する制御部15と、を備えてもよい。

(もっと読む)

1 - 20 / 45

[ Back to top ]